目前全球最先進的半導體工藝已經進入 7nm,下一步還要進入 5nm、3nm 節點,制造難度越來越大,其中晶體管結構的限制至關重要,未來的工藝需要新型晶體管。來自中科院的消息稱,中國科學家研發了一種新型垂直納米環柵晶體管,它被視為 2nm 及以下工藝的主要技術候選,意義重大。

從 Intel 首發 22nm FinFET 工藝之后,全球主要的半導體廠商在 22/16/14nm 節點開始啟用 FinFET 鰭式晶體管,一直用到現在的 7nm,未來 5nm、4nm 等節點也會使用 FinFET 晶體管,但 3nm 及之后的節點就要變了,三星在去年率先宣布 3nm 節點改用 GAA 環繞柵極晶體管。

根據官方所說,基于全新的 GAA 晶體管結構,三星通過使用納米片設備制造出了 MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應管),該技術可以顯著增強晶體管性能,主要取代 FinFET 晶體管技術。

此外,MBCFET 技術還能兼容現有的 FinFET 制造工藝的技術及設備,從而加速工藝開發及生產。

前不久三星還公布了 3nm 工藝的具體指標,與現在的 7nm 工藝相比,3nm 工藝可將核心面積減少 45%,功耗降低 50%,性能提升 35%。

從上面的信息也可以看出 GAA 環繞柵極晶體管的重要意義,而中科院微電子所先導中心朱慧瓏研究員及其課題組日前突破的也是這一領域,官方表示他們從 2016 年起針對相關基礎器件和關鍵工藝開展了系統研究,提出并實現了世界上首個具有自對準柵極的疊層垂直納米環柵晶體管(Vertical Sandwich Gate-All-Around FETs 或 VSAFETs),獲得多項中、美發明專利授權。

這一研究成果近日發表在國際微電子器件領域的頂級期刊《IEEE Electron Device Letters》上(DOI: 10.1109/LED.2019.2954537)。

左上:STEM 頂視圖,用原子層選擇性刻蝕鍺硅的方法制作的直徑為 10 納米的納米線(左)和厚度為 23 納米的納米片(右)

右上:具有自對準高k金屬柵的疊層垂直納米環柵晶體管(VSAFETs)的 TEM 截面圖(左)及 HKMG 局部放大圖(右)

下: pVSAFETs 器件的結構和I-V 特性:器件結構示意圖(左),轉移特性曲線(中)和輸出特性曲線(右)

據介紹,朱慧瓏課題組系統地研發了一種原子層選擇性刻蝕鍺硅的方法,結合多層外延生長技術將此方法用于鍺硅/硅超晶格疊層的選擇性刻蝕,從而精確地控制納米晶體管溝道尺寸和有效柵長;首次研發出了垂直納米環柵晶體管的自對準高k金屬柵后柵工藝;其集成工藝與主流先進 CMOS 制程兼容。課題組最終制造出了柵長 60 納米,納米片厚度 20 納米的p型 VSAFET。原型器件的 SS、DIBL 和電流開關比(Ion/Ioff)分別為 86mV/dec、40mV 和 1.8x105。

-

三星電子

+關注

關注

34文章

15867瀏覽量

181091 -

晶體管

+關注

關注

77文章

9708瀏覽量

138501

發布評論請先 登錄

相關推薦

7納米工藝面臨的各種挑戰與解決方案

臺積電分享 2nm 工藝深入細節:功耗降低 35% 或性能提升15%!

IBM與Rapidus在多閾值電壓GAA晶體管技術的新突破

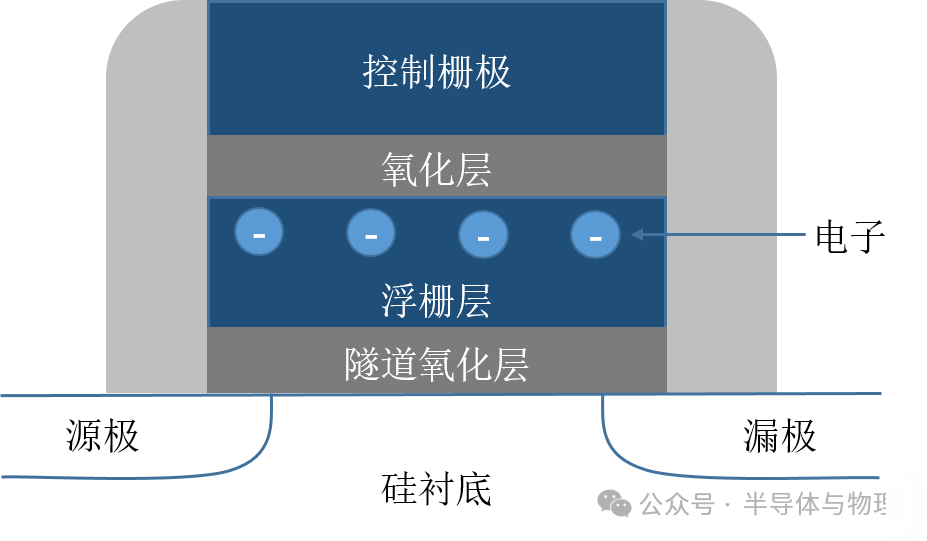

3D-NAND浮柵晶體管的結構解析

世芯電子成功流片2nm測試芯片

CMOS晶體管的尺寸規則

NMOS晶體管和PMOS晶體管的區別

GaN晶體管和SiC晶體管有什么不同

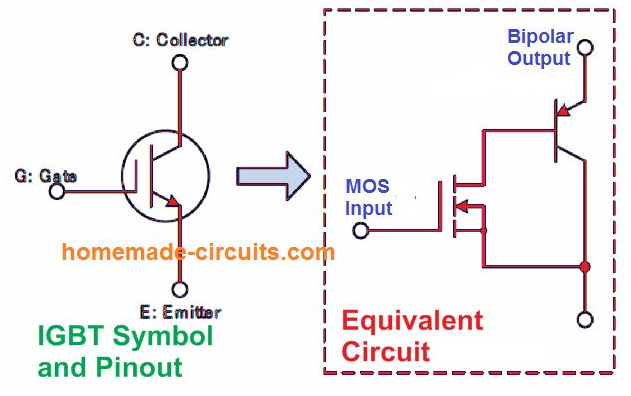

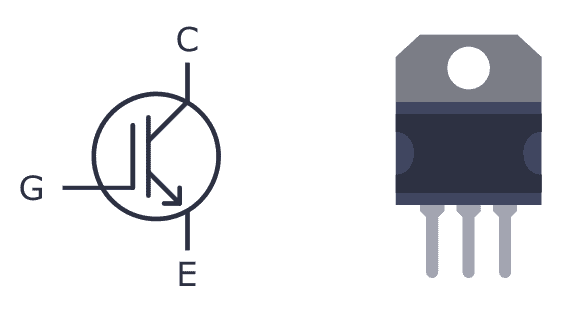

絕緣柵雙極晶體管的工作原理和結構

絕緣柵雙極晶體管的實用指南

新型垂直納米環柵晶體管,或是2nm及以下工藝的備選

新型垂直納米環柵晶體管,或是2nm及以下工藝的備選

評論