加利福尼亞州圣克拉拉(ChipWire) - 一家致力于高性能DSP內核的創業公司Bops Inc.推出了下一代產品本周在DesignCon上生成軟件開發工具。 Bopssoftware開發工具包的2.0版本包括C和MatLab的編譯器,可以解決為新架構開發高度調整的代碼的問題。總部位于加利福尼亞州帕洛阿爾托的Bops公司的目標是高性能應用,如視頻信號處理,3D圖形,xDSL和無線,銷售和營銷副總裁Rick Kepple說。例如,調制信號--Kepple稱之為“天線操作” - 對于第三代蜂窩基站來說,每秒需要數百億次操作。為了防止密集的系統過熱,每秒每1億條指令的功耗必須保持在10毫瓦左右。 Kepple表示,執行MPEG編碼和解碼的數碼攝像機的總功耗必須低于600 mW。

Bops內核旨在為這些應用程序提供可擴展的性能和低功耗。每個內核每秒將執行32億次16位操作,時鐘頻率為200 MHz。該架構支持8位,16位或32位操作數的固定和浮點數學運算。使用32位操作數,性能大約為每秒10億次浮點運算。

知識產權(IP)內核適用于I/O外設和內存,甚至適用于專用片上系統(SoC)設計的其他處理器。 Kepple表示,1999年銷售額約為4億美元,SoC市場每年增長50%。

就其本身而言,Bops內核不運行控制代碼,而是作為ARM或MIPS處理器內核的松散耦合協處理器。核心由兩個元素組成:用于控制和順序功能的序列處理器(SP),以及用于并行任務的從屬處理元件(PE)。雖然它與單個媒體訪問控制器(MAC)和算術邏輯單元(ALU)對話,但是單指令,多數據類SP包含三個并行級別:并行數據(通過數據存儲器),并行指令(通過VLIW) Kepple說,指令存儲器)和并行處理器(通過指令地址單元)。

不同版本的Bops核心將SP和PE并聯和串聯組合在一起 - 實際上是一個矩陣 - 用于各種性能組合。例如,Bops2010包括一個SP和一個1×1矩陣的PE。 Bops2020包括一個SP和兩個1x2矩陣的PE; Bops2040包括一個SP和4個4×4矩陣的PE。

集群交換機在后臺執行DMA控制器傳輸,并平衡矩陣中的活動。因此,根據Kepple的說法,在100 MHz時,Bops2040內核將在2.2微秒(213個周期)內執行256點快速傅里葉變換。 Kepple說,TI C6X在同一操作中需要13.3微秒(200 MHz時為2,660個周期)。他說,與C6X相比,Bops2040的芯片尺寸僅為四分之一,功耗僅為四分之一,內存和總線帶寬的五分之一。

與任何并行處理器一樣,編程仍然是個問題。本周推出的新軟件開發工具旨在增強可編程性--Kepple稱之為DSP標準的“第四個P”(性能,功耗和處理之后)。除了基本的DSP庫之外,Bops工具集還包括系統仿真器,指令集仿真器,GNU-C編譯器,GNU匯編器和鏈接器,VLIW指令打包器和寄存器分配器,以及用于編譯器和矢量庫的編譯器和矢量庫。 MATLAB軟件

世界上只有大約60,000名DSP程序員能夠使用匯編語言,相比之下,有600萬能夠使用C語言工作,Kepple說。任何編程工具的目標都是利用C語言程序員的基礎。

VLIW處理器,如德州儀器公司的C6X,使用C編譯器。他們的問題是,他們生產的匯編代碼永遠不如手動編碼產生的匯編代碼,并且在電池供電的IP核或SoC上永遠不能容忍隨后浪費的機器周期。 Bops聲稱其C編譯器是市場上最高效的編譯器之一。除了指令級編譯外,它的編譯器還將處理打包數據和多處理器系統。

編譯器效率最小化程序員調整。 Kepple說,需要進行一定數量的代碼調整,以最大限度地減少程序分支的處罰,并平衡并行處理器之間的負載。

Bops之前推出了Xemulator,它允許設計人員在基于FPGA的硬件中試用基于Bops的設計。在DesignCon上宣布的一項新營銷計劃允許那些對該架構非常感興趣的潛在Bops IP客戶通過從Bops接收除寄存器傳輸級代碼之外的所有內容來完成SoC設計和仿真。因此,與Bops IP的SoC設計工作可以與許可協商同時完成,Kepple說。

-

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43091

發布評論請先 登錄

相關推薦

TSP工具包軟件的應用說明

最新Simplicity SDK軟件開發工具包發布

FPGA通過SPI對DAC進行了配置,用頻譜儀測不到輸出是怎么回事?

基于EasyGo Vs工具包和Nl veristand軟件進行的永磁同步電機實時仿真

極海半導體推出AUTOSAR MCAL軟件包和配置工具

FPGA仿真工具包軟件EasyGo Vs Addon介紹

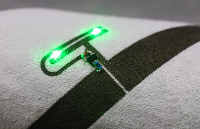

石墨烯基導電油墨具有良好的滲透性和低阻抗,針對 RFID天線性能進行了優

使用freeRTOS開發工具包時,在哪里可以找到freeRTOS的版本?

為何高端FPGA都非常重視軟件

QE for Motor V1.3.0:汽車開發輔助工具解決方案工具包

labview工具包下載

利用ProfiShark 構建便攜式網絡取證工具包

zpwsmileBops的軟件工具包針對高級DSP架構進行了調整

zpwsmileBops的軟件工具包針對高級DSP架構進行了調整

評論