多種趨勢正在將FPGA推向兩條截然不同的發展道路。

在第一條路上,FPGA不斷優化,主要用于加速數據中心工作負載。 數據中心是大型供應商關注的下一個“圣杯”。

在另一條發展道路上,有傳統的FPGA網絡市場、蜂窩基站、國防、商用航空、工業4.0和醫療。 在這些應用領域,許多工程師認為他們正在被拋棄。 他們面臨的發展挑戰與大型供應商關注的數據中心焦點截然不同。 設計人員面臨著越來越難以平衡的行為,因為他們試圖在不犧牲性能和安全性的情況下,實現低功耗和低成本。

要想實現這種平衡,就需要以新的方式來看待FPGA,采用新的工藝技術選擇、結構設計、收發器策略和內置的安全措施。這孕育出了一類新的、中等規模的FPGA,為傳統FPGA開發人員提供了新的功能。

新的工藝技術選擇

降低功耗同時優化中等規模FPGA成本的一種方法是:使用新的工藝技術。 例如,在28nm技術節點上使用Silicon-Oxide-Nitride-Silicon(SONOS)非易失性(NV)技術,其與相同或更小節點上的基于SRAM的FPGA相比,具有更低的功耗優勢。 使用65nm及以上浮柵NV技術的上一代非易失性FPGA比SONOS昂貴。 鑒于浮動柵極技術需要17.5 V來編程使用消耗大量芯片面積的大型電荷泵,SONOS技術只需要7.5 V編程,因此電荷泵可以更小。 這項技術可以縮小芯片尺寸,并有助于提供更具成本效益的器件。

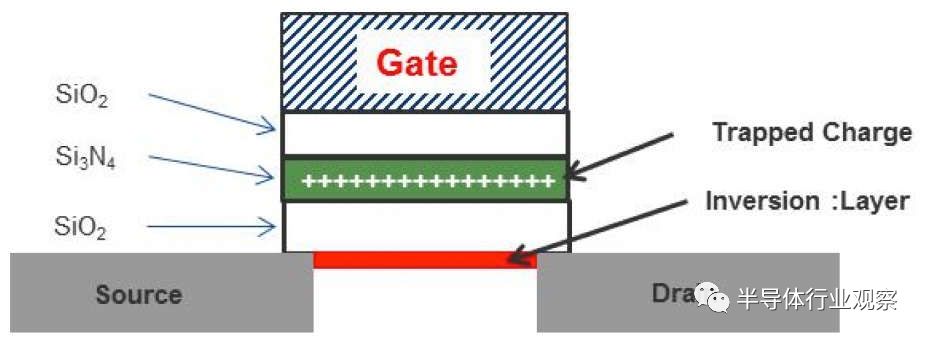

SONOS技術通過使用具有非導電氮化物電介質層(Si3N4)作為電荷存儲單元的單個多晶硅晶體管堆疊(見圖1)來實現這些優勢。 使用這種方法,在底部氧化物中可能存在的任何缺陷附近,只有非常少量的電荷將流失。

由于儲存的電荷在絕緣氮化物層中不可移動,所以大部分儲存的電荷仍然保持原樣,完好無損。 與浮柵技術相比,可以使用更薄的底部氧化物,并且可以用更低的編程電壓(?7.5 V)和更小的電荷泵進行編程。與SRAM存儲單元相比,使用SONOS所需的晶體管數量更少。

圖1:SONOS技術。 (來源:Microsemi)

SONOS技術通過使用包含N通道和P通道NV器件的推挽式單元來提高可靠性。 NV器件不處于數據路徑,僅用于控制用作數據路徑開關的標準晶體管。 這提供了很大的功能優勢,因為NV器件閾值電壓(Vt)的任何變化都不會改變開關電導。設備互動的方式充當了內置的準冗余,可防止產品在使用期間的性能下降。

功耗也會降低。 首先,SONOS NV FPGA配置單元啟用兩種不同的可編程“配置”狀態,控制FPGA數據信號路徑,關斷和開啟時優化開關器件以提供比標準晶體管低得多的漏電。 其次,SONOS技術可以將器件置于一種狀態:將電源電壓關閉至FPGA邏輯模塊中的配置存儲器,同時將用戶的狀態保存在低功耗鎖存器中。 這降低了約三分之二的待機功耗。

SONOS還有兩個重要的優勢。 首先是“即時開”功能:因為FPGA邏輯配置單元在掉電后保持其狀態,所以當電源返回時不需要重新加載FPGA設計代碼,也不需要外部引導PROM。其次,與基于SRAM的FPGA中的配置存儲器不同,該器件可由于中子轟擊而翻轉狀態,SONOS器件的FPGA邏輯配置不受SEU影響。 SONOS NV電荷存儲在氮化物電介質中,不容易受到中子轟擊帶來的電荷損失。

新的結構設計

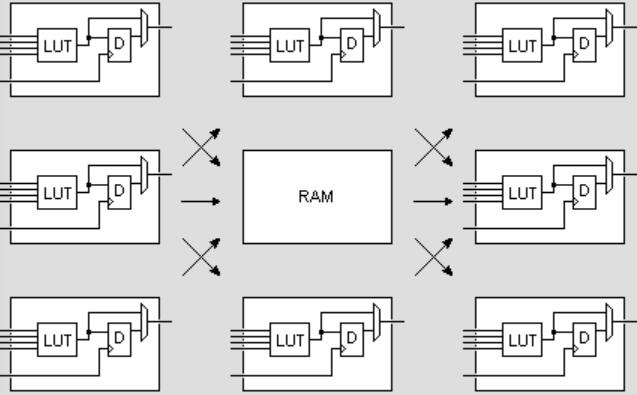

另一種提高中等規模FPGA性能的方法是:改變可編程邏輯結構。 這使得器件能夠滿足主流性能要求,同時,靜態功耗僅為SRAM FPGA的十分之一,以及總功耗的一半。

功耗和性能需要權衡考量。 例如,6輸入LUT可提供一些速度優勢,但4輸入LUT是現代工藝技術中功率和成本優化FPGA的更好選擇。 同時,隨著工藝技術從65nm發展到28nm及以上,由于金屬線和通孔電阻的縮放差,布線的延遲已成為邏輯延遲的主導因素。 拓寬金屬線會增加芯片面積和成本。 因此,隨著每一代后續的工藝技術的發展,集群間(inter-cluster)延遲將成為關鍵路徑的首要問題,6輸入LUT的速度優勢將會減弱。 確保相鄰LUT之間的快速直連可以減少集群內延遲,尤其是與先進的綜合和布局算法相結合。 某些邏輯功能(如MUX樹)會從直連中受益良多。

為了獲得最佳效果,應該仔細優化FPGA系列的功耗性能折衷方案,以便核心邏輯電源電壓略低于其制造過程的標稱電壓。 在28nm SONOS器件中,這意味著優化1.0V核心邏輯電源電壓,在需要額外速度時可選擇使用完整的1.05 V電源。

FPGA架構的最后一塊是數學模塊,它應該支持18位乘法累加操作。 通過提供具有完整19位結果和輸入值級聯鏈的預加法器,并通過確保數學模塊支持精確的9位操作,包括9×9點積模式。 后者非常適合用于圖像處理和卷積神經網絡(CNN)。

FPGA收發器

收發器在優化FPGA成本,功耗和性能要求方面發揮著重要作用。 許多應用需要高達24個高速全雙工收發器通道。 他們還需要SerDes收發器,可以支持250 Mbps到12.7 Gbps的波特率,以覆蓋全系列的SDI,高達10Gbps的以太網,JESD204B轉換器和其他應用。 優化收發器的一個主要優勢在于降低從高端FPGA調整的更高速SerDes的性能,因為與降級的SerDes方法相比,它在所有波特率下的功耗都要低得多。

多種架構選擇有助于降低FPGA收發器功耗,從使用半速率架構實現收發器到使用高度共享的傳輸PLL架構。 理想情況下,FPGA應該具有1~6個四通道收發器,最多可以有24個SerDes通道。 許多均衡功能允許更長距離,并在印刷電路板和背板中使用低成本材料。 特殊的鎖相環(PLL)特性可為用戶提供更多靈活性,從更靈活的時鐘和波特率選擇到簡化的radiated-emission要求,以及更高的帶寬選項。

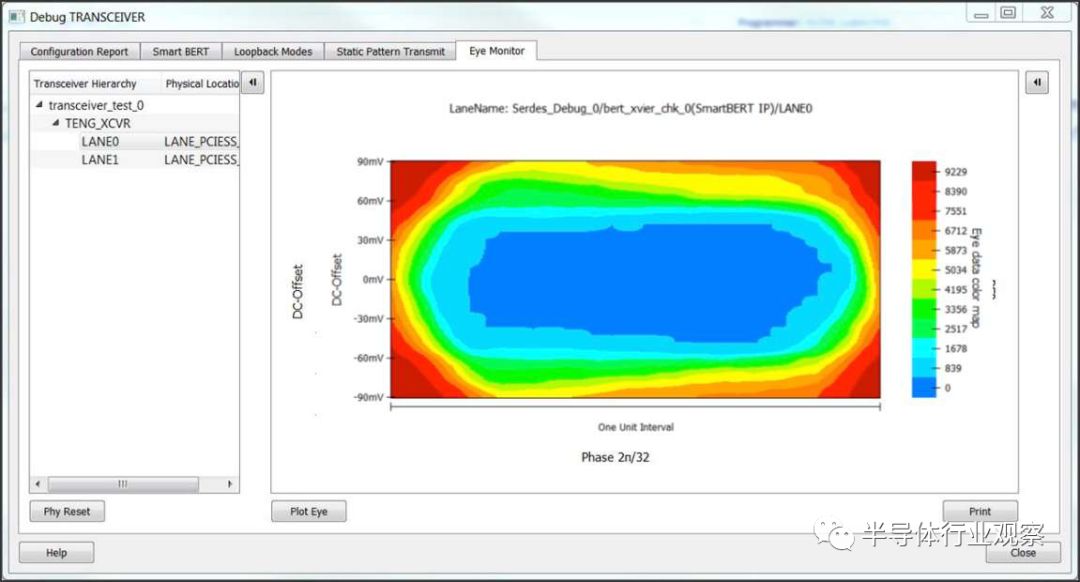

調試和測試也很重要,包括內置偽隨機二進制序列(PRBS)發生器和檢測器的可用性以及支持非直流耦合信號的IEEE 1149.6“AC JTAG”。 包括帶調試軟件支持的內置眼圖監視器,設計人員無需示波器即可調試SerDes。 人們可以實時優化DFE和CTLE參數,并調用最終產品的理想設置(參見圖2)。

圖2:SerDes眼圖監視器智能調試軟件

解決安全挑戰

目前,設計的安全性存在許多威脅。 從用戶設計IP到制造過程的所有內容都可能受到影響。

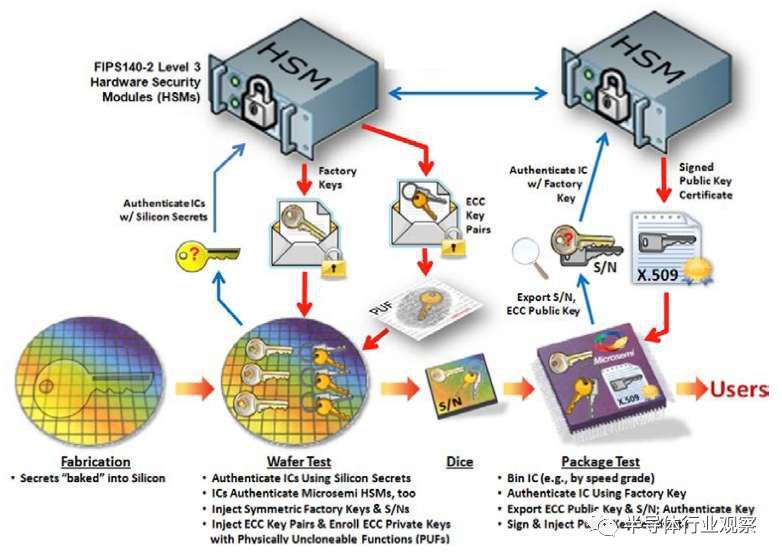

關鍵的安全技術和性能包括可信任的硬件roots,強大的加密技術以及每個階段的頂級密鑰管理,以及內置被動和主動對策以防止篡改的設備。 圖3顯示了使用唯一序列號、密鑰和X.509公鑰證書進行安全FPGA配置的最佳實現方法。

圖3:設備證書信任鏈

有了這些組件,就可以解決設計和數據安全問題。 設計安全性要求FPGA使用制造商提供的密鑰和證書,以及其他技術(從專利的差分功耗分析(DPA)對策到防止側向信道攻擊的技術),以保護用戶的IP。 另一種提高設計安全性的方法是使用物理不可克隆功能(PUF)技術來生成硬件固有密鑰。

數據安全性要求使用專用于核心NIST認證的FPGA用戶的加密處理器,以實現許多最常用的加密算法,如AES,SHA 2,ECC,RSA和DH,并包含加密級TRNG。 與向FPGA架構添加加速器相比,用戶加密處理器適用于許多應用,從而降低成本(面積、功耗和其它相關)。

市場對需要成本優化的中等規模FPGA的需求不斷增長,在通信、國防和工業市場,對密度高達500K邏輯單元(LE)的情況下,要求功率密度顯著降低。 一個新的發展路線圖已經出現,它將新的工藝技術和結構設計與重要的收發器變化和安全特性相結合,使FPGA能夠解決主流應用的成本、功耗、性能和安全要求,同時提供非易失性技術的所有優勢。

-

收發器

+關注

關注

10文章

3438瀏覽量

106077 -

存儲器

+關注

關注

38文章

7514瀏覽量

164007 -

數據中心

+關注

關注

16文章

4813瀏覽量

72225

發布評論請先 登錄

相關推薦

如何選擇滿足FPGA設計需求的工藝?

FPGA架構的功耗及影響功耗的用戶選擇方案

FPGA選擇和系統設計架構

關于Vivado時序分析介紹以及應用

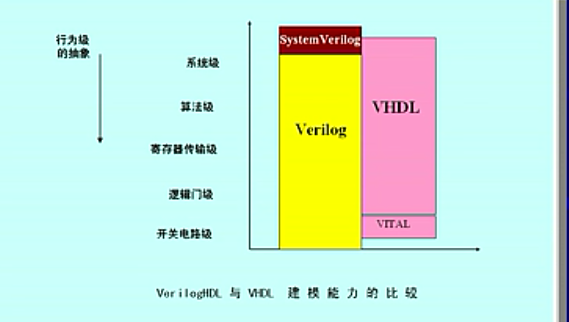

FPGA視頻教程之學習FPGA選擇verilog還是vhdl詳細資料說明

關于FPGA的新變化的分析和介紹

關于FPGA的分析和介紹以及應用

關于基于FPGA的圖像FFT濾波處理的分析和介紹

關于FPGA與GPU分析介紹

詳細介紹關于FPGA開發板內部ram是如何操作的

為FPGA選擇合適的電源穩壓模塊

關于FPGA的開源項目介紹

關于FPGA的新選擇的分析介紹

關于FPGA的新選擇的分析介紹

評論