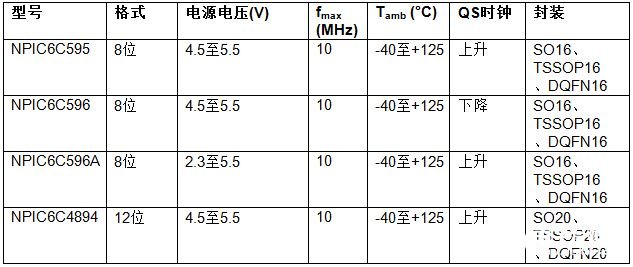

4位移位寄存器的設計與實現

使用ISE軟件設計并仿真,使用ISE軟件進行4位移位寄存器的設計與實現。

步驟

1. 編寫文本文件并編譯

2. 軟件仿真

3. 進行硬件配置

原理

1. ISE軟件是一個支持數字系統設計的開發平臺。

2. 用ISE軟件進行設計開發時基于相應器件型號的。

注意:軟件設計時選擇 的器件型號是與實際下載板上的器件型號相同。

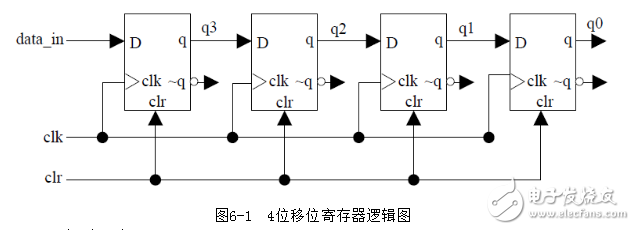

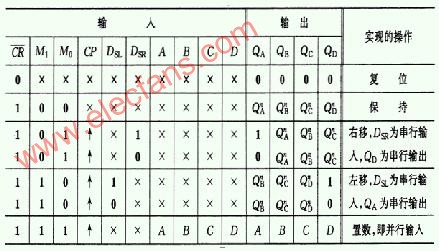

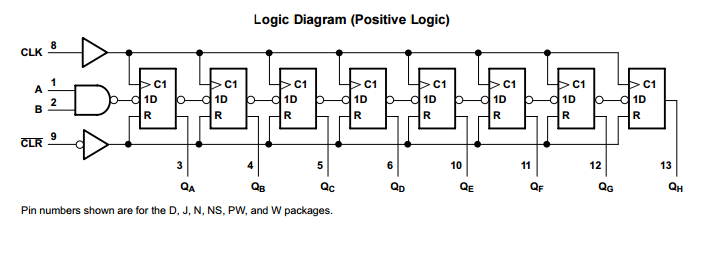

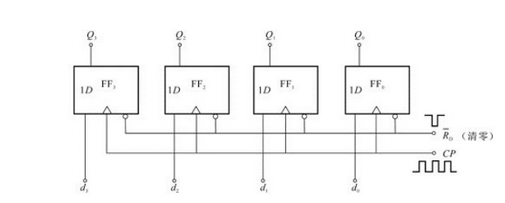

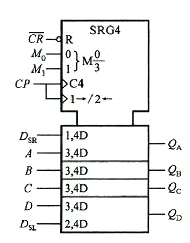

? ? ? ? 3. 圖6-1所示為4位

(1) 新建工程

雙擊桌面上“ISE Design Suite 14.7”圖標,啟動ISE軟件(也可從開始菜單啟動)。每次打開ISE都會默認恢復到最近使用過的工程界面。當第一次使用時,由于還沒有歷史工程記錄,所以工程管理區顯示空白。選擇File New--Project選項,在彈出的對話框中輸入工程名稱并指定工程路徑。

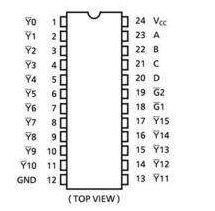

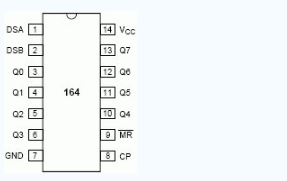

點擊Next按鈕進入下一頁,選擇所使用的芯片及綜合、仿真工具。計算機上安裝的所有用于仿真和綜合的第三方EDA工具都可以在下拉菜單中找到。在圖中我們選用了Spartan6 XC6SLX16芯片,采用CSG324封裝,這是NEXYS3開發板所用的芯片。另外,我們選擇Verilog作為默認的硬件描述語言。

再點擊Next按鈕進入下一頁,這里顯示了新建工程的信息,確認無誤后,點擊Finish就可以建立一個完整的工程了。

(2) 設計輸入和代碼仿真

在工程管理區任意位置單擊鼠標右鍵,在彈出的菜單中選擇New Source命令,選擇Verilog Module輸入,并輸入Verilog文件名。

單擊Next按鈕進入端口定義對話框。其中Module Name欄用于輸入模塊名,這里是shiftreg,下面的列表框用于端口的定義。Port Name表示端口名稱,Direction表示端口方向(可選擇為input、output或inout),MSB表示信號最高位,LSB表示信號最低位,對于單信號的MSB和LSB不用填寫。當然,端口定義這一步

我們也可以略過,在源程序中再行添加。

定義了模塊的端口后,單擊Next進入下一步,點擊Finish完成創建。這樣,ISE就會自動創建一個Verilog模塊的模板,并且在源代碼編輯區打開。簡單的注釋、模塊和端口定義已經自動生成,接下來的工作就是將代碼編寫完整。

輸入代碼后,我們還需要對模塊進行測試。在工程管理區將view設置為Simulation,在任意位置單擊鼠標右鍵,并在彈出的菜單中選擇New Source,在類型中選擇Verilog Test Fixture,輸入測試文件名,單擊下一步。這時所有工程中的模塊名都會顯示出來,我們選擇要進行測試的模塊。點擊Next ,再單擊Finish按鈕,ISE會在源代碼編輯區自動生成測試模塊的代碼。我們看到,ISE已經自動生成了基本的信號并對被測模塊做了例化。我們的工作就是在initial?end塊中的“//Add stimulus here”后面添加測試向量。

完成測試文件編輯后,確認工程管理區中view選項設置為Simulation,這時在過程管理區會顯示與仿真有關的進程。右鍵單擊其中的Simulate Behavioral Model項,選擇彈出菜單中的Process Properties項,會彈出屬性設置對話框,其中Simulation Run Time就是仿真時間的設置,可將其修改為任意時長。

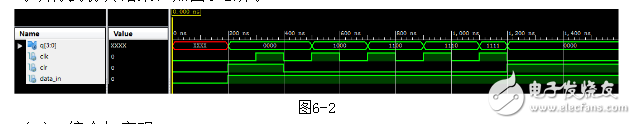

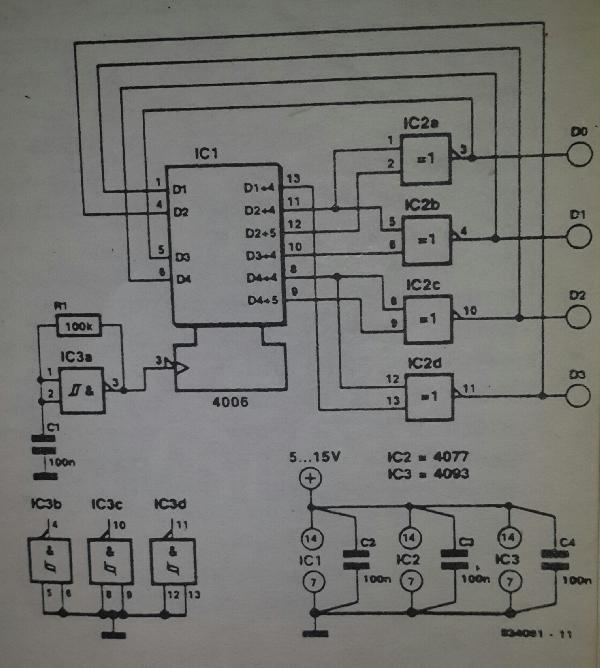

仿真參數設置完后,就可以進行仿真。首先在工程管理區選中測試代碼,然后在過程管理區雙擊Simulate Behavioral Model,ISE將啟動ISE Simulator,可以得到仿真結果,如圖6-2所示。

(3) 綜合與實現

在工程管理區的view中選擇Implementation,然后在過程管理區雙擊Synthesize-XST,就可以開始綜合過程。

另外,要實現設計,還需要為模塊中的輸入輸出信號添加管腳約束,這就需要在工程中添加UCF文件。在工程管理區單擊鼠標右鍵,點擊New Source,選擇Implementation- Constraints File,出現一個空白的約束文件,我們就可以為設計添加各種約束。如果綜合步驟沒有語法錯誤,XST能夠給出初步的資源消耗情況,點擊Design Summary,即可查看。

在過程管理區雙擊Implementation Design選項,就可以自動完成實現步驟。如果設計沒有經過綜合,就會啟動XST完成綜合,在綜合后完成實現過程。經過實現后能夠得到精確的資源占用情況。在Design Summary即可看到具體的資源占用情況。

(4) 器件配置

硬件配置是FPGA開發最關鍵的一步,只有將HDL代碼下載到FPGA芯片中,才能進行調試并最終實現相應的功能。首先我們必須生成能下載到硬件中的二進制比特文件。雙擊過程管理區的Generate Programming File,ISE就會為設計生成相應的二進制比特文件。

然后利用USB-MiniUSB纜線,來為開發板提供電源和數據下載。我們只需上網下載免費的Digilent Adept軟件,即可快速實現Nexys3開發板上FPGA的配置。用USB-MiniUSB纜線連接開發板和PC,打開開發板的電源開關,然后啟動Digilent Adept軟件。系統開始自動連接FPGA設備,成功檢測到設備后,會顯示出JTAG鏈上所用芯片。

界面上將顯示檢測到NEXYS3開發板上的器件FPGA(XC6SLX16)。這里我們對FPGA進行配置。在Browse中找到之前生成的設計的二進制比特文件,并點擊旁邊的Program按鈕,軟件就開始對FPGA進行配置。配置成功后,下面的狀態欄會顯示Programming Successful。至此,器件配置成功,我們就可以在器件上驗證預期的設計有沒有很好的得以實現。

? ? ? ?移位寄存器代碼

移位寄存器,不但可以寄存數碼,還可以在脈沖信號的作用下,寄存數碼可以根據需求發生偏移。在本次設計中使用分頻信號來充當脈沖信號,控制在人眼可視范圍內(始終頻率低于10Hz)寄存自動發生發生偏移,代碼如下:

module Design_Code(

《span style=“white-space:pre”》 《/span》input clk,《span style=“white-space:pre”》 《/span》//input by “V10”

《span style=“white-space:pre”》 《/span》input clr,

《span style=“white-space:pre”》 《/span》input data,

《span style=“white-space:pre”》 《/span》output reg [3:0] out

);

《span style=“white-space:pre”》 《/span》

reg [26:0] c;

assign mclk = c[5];《span style=“white-space:pre”》 《/span》// The Data of Simulation《span style=“white-space:pre”》 《/span》

//assign mclk = c[26];《span style=“white-space:pre”》 《/span》//Easy for person to distinguish

always @ (posedge clk)

《span style=“white-space:pre”》 《/span》begin

《span style=“white-space:pre”》 《/span》//c《= c + 1;

《span style=“white-space:pre”》 《/span》if(clr)

《span style=“white-space:pre”》 《/span》c《=0;

《span style=“white-space:pre”》 《/span》else

《span style=“white-space:pre”》 《/span》c 《= c+1‘b1;

《span style=“white-space:pre”》 《/span》end

always @ (posedge mclk or posedge clr)

《span style=“white-space:pre”》 《/span》begin

《span style=“white-space:pre”》 《/span》if(clr)

《span style=“white-space:pre”》 《/span》out 《= 4’b0;

《span style=“white-space:pre”》 《/span》else

《span style=“white-space:pre”》 《/span》out 《= {data, out[3:1]};

《span style=“white-space:pre”》 《/span》end

endmodule

在本次設計中使用到了非阻塞賦值“《=”。它與阻塞賦值“=”是有區別的。

阻塞賦值:算式y=b,一旦執行當前的賦值語句,賦值目標變量y幾顆獲得等號右邊表達式的計算值。在這里值得注意的是,如果一塊語句中含有多條阻塞賦值語句,那么當執行某一條語句時其他語句被阻塞,將禁止執行。阻塞賦值的執行有點像串行執行。

非阻塞賦值:算式y《=b,必須在語句塊結束時完成整體賦值。在執行某一條語句時,對于語句塊的其他賦值算式不進行限制,換句話說,語句塊中的非阻塞賦值算式是并行執行的。

注意:由于assign不能引導語句塊,故只能使用阻塞賦值。

注意:阻塞賦值與非阻塞賦值不可以混合使用。

測試文件:

initial begin

// Initialize Inputs

data = 1;

clr = 1;

clk = 0;

end

always

begin

#1

clk = ~clk;

end

always

begin

#100000

clr = ~clr;

end

always

begin

#500

data = ~data;

end

注意:在寫仿真部分時always與initial不能相互嵌套。使用復位信號(例如:clr)時,x先使能復位信號,一段時間后取消復位信號(避免系統一直處于復位狀態)

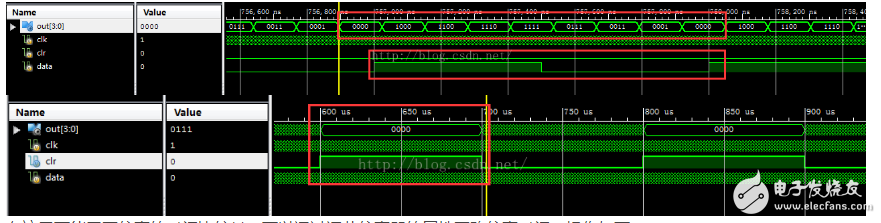

仿真結果:

在這里可能需要仿真的時間比較長,可以通過調節仿真器的屬性更改仿真時間,操作如下

電子發燒友App

電子發燒友App

評論