作者:賽普拉斯半導體存儲器產品部門 資深主任應用工程師Jayasree Nayar

對于網絡應用來說,選擇合適的同步SRAM是至關重要的,因為網絡應用需要增加帶寬來達到更好的系統性能。系統設計人員需要明白不同種同步SRAM技術的特色和優勢,從而可以為他們的應用選擇正確的同步SRAM存儲器。

選擇合適同步SRAM的重要因素包括:密度,反應時間,速度,讀寫比率,以及功耗。了解了這些因素如何影響性能,可靠性和價格,設計人員就可以為他們的應用選擇最佳的同步SRAM。

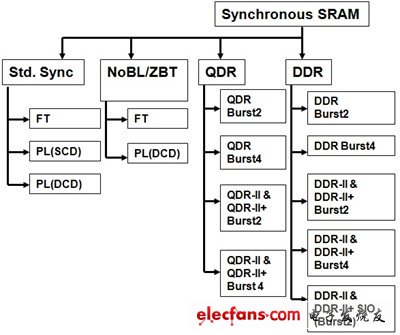

同步SRAM有如下分類:

圖1:同步SRAM種類

Std.Sync: 標準同步

FT: Flow Through

PL:Pipelined

SCD: 單周期取消片選Single Cycle Deselect

DCD: 雙周期取消片選Double Cycle Deselect

QDR: 四倍速Quad Data Rate

DDR: 雙倍速Double Data Rate

標準同步SRAM

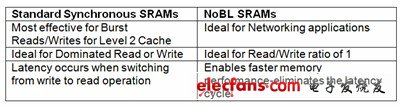

標準同步SRAM通常用于工業電子,儀器儀表,和軍事應用。其經常用作數據緩存(臨時存儲),可以通過其高速、單倍速(SDR)接口隨機存取。標準同步 Burst SRAM對于受控讀寫操作來說是很理想的。客戶可以選擇Flow-through 或Pipelined結構,線性和交叉存取burst模式,也就是SCD和DCD。

Flow-through SRAM:Flow-through器件在輸入端有一個寄存器。在時鐘上升沿,捕獲器件的地址和控制。在讀操作時,允許請求的數據流入器件輸出端,因此在第一個周期會讀出數據。在寫操作時。地址,控制和數據在同一個時鐘上升沿捕獲。

Pipelined SRAMs: Pipelined 和flow-through SRAM的區別是,pipelined器件在輸入和輸出端都有一個寄存器。在讀操作時,數據可以流入pipeline器件輸出寄存器。在下一個時鐘周期,數據鎖存在器件輸出端。這和flow-through器件有所區別,這是因為從pipelinedSRAM 出來的數據會比flow-through的晚一個周期。然而,pipeline器件可以工作在比flow-through器件更高的頻率,因為訪問會有幾個周期的中斷。pipeline器件的寫操作和flow-through器件相同。

Pipelined SRAM包括單周期取消片選(SCD)和雙周期取消片選(DCD)兩種類型。這決定了在器件取消片選以后需要多長時間使數據總線進入三態。三態定義為傳輸線設為高阻狀態。

●單周期取消片選(SCD):I/O總線在片選結束一個周期后進入三態。

●雙周期取消片選(DCD):I/O總線在片選結束兩個周期后進入三態。

總體來說,pipelined SRAM可以比flow-through SRAM工作在更高的頻率上。

在反應時間很重要的應用中,flow-through器件更合適,如果速度更重要,那么pipeline器件更合適。

如果系統的讀/寫比率為1:1,那么標準同步的Flow-through 和Pipelined SRAM就都不合適了,NoBL SRAM更合適。

NOBL/ZBT SRAM

無總線延時(NoBL- No Bus Latency) SRAM在網絡和通信系統和測試設備中很常見。和標準同步Burst SRAM極為類似,NoBL SRAM也有flow-through 和pipelined SDR(單倍速)結構。在burst模式下,設計人員可以選擇線性和交叉burst模式

NoBL Burst SRAM特別針對避免讀寫操作切換時總線浪費而設計的。這種器件還有另外一個名字-零總線轉向 (ZBT- Zero Bus Turnaround)。NoBL結構避免了讀寫之間的等待周期,從而使I/O總線利用率可以接近100%。在某些系統中,可以顯著提高帶寬。標準同步 SRAM和 NoBL SRAM都有公用I/O結構。標準同步SRAM在高速緩存或者讀寫可控應用中很有效。NoBL SRAM更適用于讀寫經常切換的情況下,因為它可以避免讀寫切換時的延時。

QDR SRAM

下面我們介紹一下QDR系列器件。這個系列包括QDR和QDRII。

QDR由QDR組織開發。這個組織制定了數據手冊,封裝,QDR性能標準,因此設計人員可以從不同的供應商購買。

QDR是指四倍速(Quad Data Rate),QDR組織定義了QDR SRAM產品,最初是為了網絡和通訊市場設計的。QDR SRAM和NoBL SRAM類似,但結構上有很大增強,例如雙倍速I/O,專門的讀寫端口可以避免總線爭用。QDR還有 HSTL電平以及可編程輸出阻抗設置。QDR有單獨并獨立的輸入和輸出,這就意味著用戶可以同時進行讀寫操作。之所以叫四倍速是因為在任何周期,都可以兩組數據讀出兩組數據讀入QDR器件。

QDR SRAM用于網絡應用,讀寫基本保持平衡,例如包緩存,靜態列表,流量狀態,日程安排。QDR SRAM最大的時鐘頻率是167MHz,1周期讀延時,現有工業級標準165 BGA封裝。

QDRII SRAM

QDRII SRAM 在操作上和QDR SRAM類似,但性能有所提升。QDRII SRAM包括兩個源同步,自由運行回應時鐘(CQ/CQ),可以很容易捕獲數據。QDRII SRAM還支持1.5V HSTL接口。應用和QDR SRAM相同。然而,QDRII SRAM速度可以達到333MHz,1.5周期讀延時,burst長度為2和4,現有工業級標準165 BGA封裝。

DDR SRAM

QDR組織還定義了DDR SRAM,其類似于傳統的同步Burst SRAM產品,但是有雙倍速I/O.和傳統同步Burst SRAM相同,他們應用于讀操作比較多的應用中,例如,網絡通信應用中的包查找,包分級。

DDRII SRAM

DDRII SRAM的操作類似于DDR SRAM,但是性能有所提升。DDRII SRAM包括兩個源同步,自由運行回應時鐘(CQ/CQ),可以很容易捕獲數據。DDRII SRAM還支持1.5V HSTL接口。應用和DDR SRAM相同。DDRII SRAM速度可以達到333MHz,1.5周期讀延時,burst長度為2和4,現有工業級標準165 BGA封裝。

DDRII SIO SRAM

DDRII SIO SRAM類似于DDRII CIO SRAM,但是有兩個獨立的端口:讀端口和寫端口都可以訪問存儲器陣列。讀端口有數據輸出支持讀操作,寫端口有數據輸入支持寫操作。DDR II SIO SRAM完全避免了公用I/O設備數據“轉向”的問題。DDR II SIO有獨立的輸入和輸出總線,因此和QDRII很類似。唯一的區別是DDRII SIO每個周期只能處理一個操作。另外,由于某個時刻只有一個總線在用,因此總線利用率為50%。

QDRII+ SRAM

QDRII+SRAM操作上和QDRII SRAM類似,但提升了性能。在QDRII+器件中沒有冗余數據輸入時鐘(C & /C),它有一個握手信號(QVLD)代替,這個握手信號當數據變為有效時會有指示,因此簡化了數據捕獲。設計人員還可選擇可編程ODT (On Die Termination)的QDRII+產品。QDRII+SRAM最大速度為550MHz,2或2.5周期讀延時,burst長度為2和4,現有工業級標準165 BGA封裝。

DDRII+ SRAM

DDRII+SRAM操作上和DDRII SRAM類似,但提升了性能。在DDRII+器件中沒有冗余數據輸入時鐘(C&/C),它有一個握手信號(QVLD)代替,這個握手信號當數據變為有效時會有指示,因此簡化了數據捕獲。設計人員還可選擇可編程ODT (On Die Termination)的DDRII+產品。ODT特性在寫周期時開啟,在讀周期時關閉,從而可以節省功耗。DDRII+SRAM最大速度為 550MHz,2或2.5周期讀延時,burst長度為2和4,現有工業級標準165 BGA封裝。

DDRII+ SIO SRAM

DDRII+ SIO SRAM類似于DDRII+ CIO SRAM,但是有兩個獨立的端口:讀端口和寫端口都可以訪問存儲器陣列。讀端口有數據輸出支持讀操作,寫端口有數據輸入支持寫操作。DDR II+ SIO SRAM完全避免了公用I/O設備數據“轉向”的問題。

QDR和QDRII/QDRII+ 可以使讀寫操作平衡的系統更優化:

●包存儲

●鏈接表

●查找表

●統計表存儲

●y

DDR 和DDRII/DDRII+ 專門應用于數據流操作或讀/寫不平衡的系統:

●2級緩存

DDRII/DDRII+ 分立I/O專門應用于1地址/時鐘2-word burst的系統中。

再次強調一下,QDR 和QDRII/II+適用于讀寫平衡的系統,例如查找表和統計表存儲。

如果需要高速緩存,DDR 和DDRII/II+更適合。

如果用戶傾向于QDR結構,但地址總線不支持QDR接口,那么DDR分立IO將是最好選擇。

存儲器選擇:關鍵因素

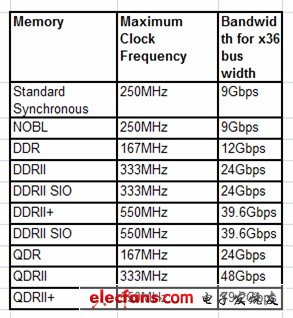

選擇同步SRAM存儲器的首要因素是數據帶寬。表一列出了上述討論過的不同種同步SRAM的帶寬。為了計算方便,使用的是最大時鐘頻率和x36總線寬度。

表 1: 同步SRAM 帶寬概覽

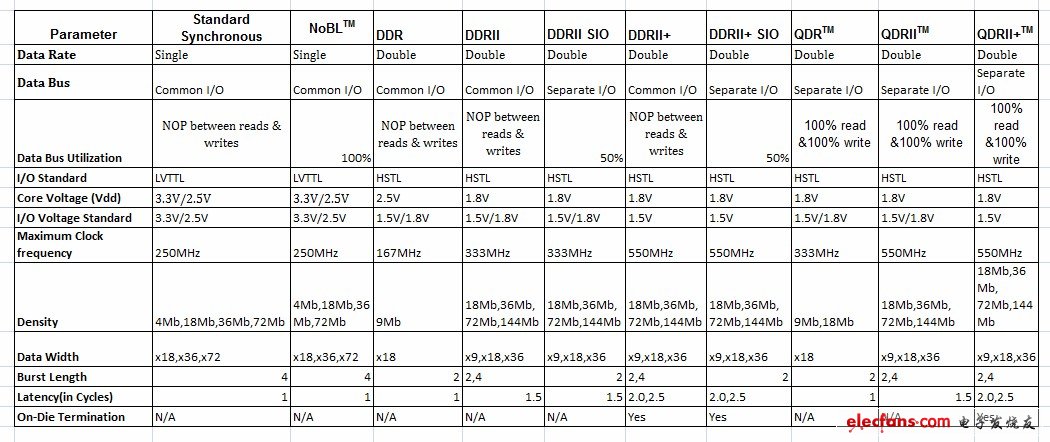

另一個同步SRAM的選擇因素是功耗。QDR/DDR器件的功率消耗比標準同步SRAM要低,因為供電電壓低。決定存儲器選擇的其他因素如表2所示:

表2:存儲器選擇概覽

注:QDRII+ 和DDRII+可以提供帶活不帶ODT (On-Die Termination)

現在有很多種同步SRAM。了解了存儲器種類之間的不同,系統設計人員就可以為他們的應用選擇恰當的同步存儲器。

電子發燒友App

電子發燒友App

評論