近幾年,云計算、5G、物聯(lián)網(wǎng)、人工智能等產(chǎn)業(yè)的迅速發(fā)展使得對內(nèi)存的需求大增。作為內(nèi)存技術(shù)的關(guān)鍵模塊,DDR PHY的市場需求也在高速增長。本文從新銳IP企業(yè)芯耀輝的角度,談?wù)凞DR PHY,以及芯耀輝在DDR PHY上的技術(shù)突破,助力服務(wù)芯片設(shè)計企業(yè)。

什么是DDR PHY

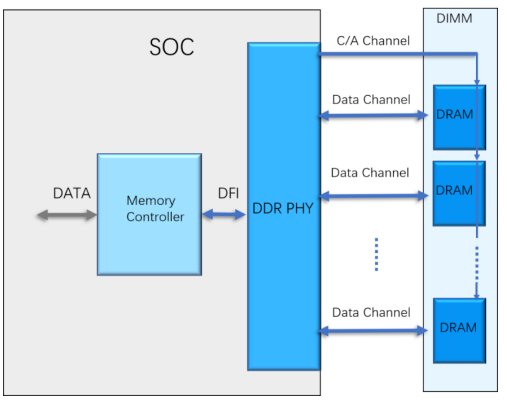

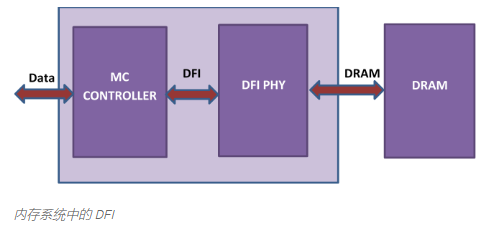

DDR PHY是DRAM和內(nèi)存控制器通信的橋梁,它負(fù)責(zé)把內(nèi)存控制器發(fā)過來的數(shù)據(jù)轉(zhuǎn)換成符合DDR協(xié)議的信號,并發(fā)送到DRAM;相反地,其也負(fù)責(zé)把DRAM發(fā)送過來的數(shù)據(jù)轉(zhuǎn)換成符合DFI協(xié)議的信號并發(fā)送給內(nèi)存控制器。DDR PHY和內(nèi)存控制器統(tǒng)稱為DDR IP,他們保證了SoC和DRAM之間的數(shù)據(jù)傳輸,如圖1所示。

圖1 DDR PHY和內(nèi)存控制器在SoC中的作用

DDR IP 市場需求強勁

作為重要的接口IP,DDR IP的市場需求強勁。據(jù)IP Nest 機構(gòu)預(yù)測,2015-2024年全球接口類IP保持 16% 的平均年復(fù)增長率。未來幾年, 在5大類接口IP(USB、PCIe、DDR、D2D&Ethernet、MIPI)市場份額上,DDR IP將持續(xù)保持前三的市場份額。

目前在DDR IP的市場上,國際廠商占據(jù)較高的市場份額,而國內(nèi)IP企業(yè)占比很小,究其原因,主要是由于DDR PHY具有較高的技術(shù)門檻,要在這類PHY上實現(xiàn)突破并不容易。

首先與其說DDR PHY是一個芯片技術(shù),不如說DDR PHY是一門系統(tǒng)工程。DDR的數(shù)據(jù)傳輸采用并行多位、單端突發(fā)的傳輸模式,對電源完整性PI(Power Integrity,電源完整性)和信號完整性SI (Signal Integrity,信號完整性)的要求很高。另一方面,DDR可以說是對訓(xùn)練(Training)要求最多的接口。各種訓(xùn)練是否獲得最佳的結(jié)果直接影響DDR工作的可靠性。對于PHY開發(fā)人員來說,既要懂物理層的設(shè)計,也要懂訓(xùn)練算法的設(shè)計,只有這樣才能開發(fā)出可靠的產(chǎn)品,然而這又無形中抬高了設(shè)計的門檻。最后,如何實現(xiàn)高速的單端信號傳輸,是DDR IO設(shè)計的一大考驗。

多點著力,攻克DDR PHY技術(shù)瓶頸

作為一家專注于半導(dǎo)體IP研發(fā)和服務(wù)的高科技公司,芯耀輝科技看準(zhǔn)了企業(yè)的需求和市場機遇,通過可靠的SI和PI分析、優(yōu)化的訓(xùn)練算法設(shè)計、高性能的IO設(shè)計等一系列技術(shù)創(chuàng)新,成功突破了DDR PHY的技術(shù)瓶頸。

關(guān)鍵技術(shù)點一:可靠的SI和PI分析指導(dǎo)

DDR數(shù)據(jù)傳輸?shù)奶攸c是:多位并行傳輸,單端數(shù)據(jù)突發(fā)模式。目前SoC可以集成多達72位(DDR4帶ECC)的DDR接口,多位并行傳輸在封裝和PCB上的布線是非常復(fù)雜的,很多走線有一定等長要求,同時還要盡量減小線間串?dāng)_,所以合格的封裝和PCB設(shè)計是一大挑戰(zhàn)。另外突發(fā)模式的傳輸,SSO(Simultaneous Switching Output)噪聲也會嚴(yán)重影響DDR的性能。所以DDR穩(wěn)定的工作需要可靠的SI和PI分析。

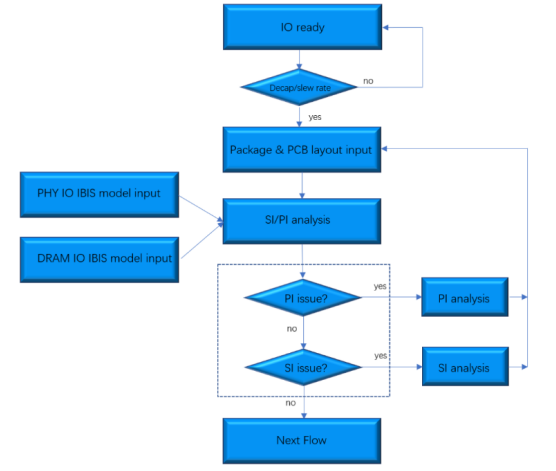

在芯片開發(fā)早期,確定好芯片的PAD規(guī)劃和封裝規(guī)劃,對于設(shè)計后期優(yōu)化DDR的SI和PI性能至關(guān)重要。芯耀輝在系統(tǒng)級芯片設(shè)計早期、IO準(zhǔn)備階段就開展SI和PI的分析,提前幫助客戶規(guī)劃,以確保集成的DDR PHY的量產(chǎn)性能。如下圖2所示為芯耀輝的SI和PI流程示意圖。

圖2 芯耀輝SI和PI流程示意圖

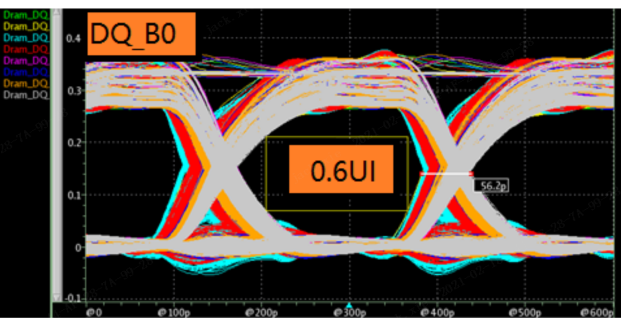

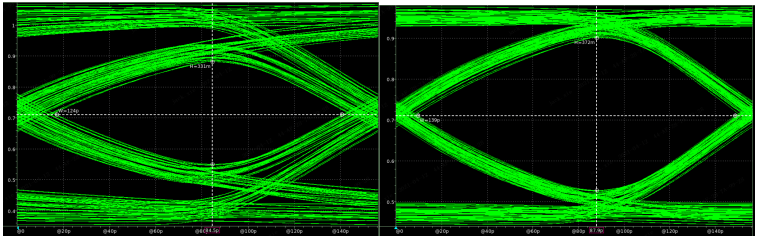

另外,芯耀輝團隊還開發(fā)出了一套特殊碼流分析技術(shù)。通過該技術(shù),在設(shè)計階段可以高效地分析封裝和PCB設(shè)計是否滿足DDR眼圖的要求,可以快速定位缺陷,并指導(dǎo)客戶優(yōu)化完善。圖3給出了一個實際合作案例,展示了系統(tǒng)設(shè)計最終完成后的眼圖質(zhì)量。

圖3 芯耀輝LPDDR4X-3733仿真寫數(shù)據(jù)眼圖

關(guān)鍵技術(shù)點二:高可靠性訓(xùn)練設(shè)計

DDR系統(tǒng)的穩(wěn)定工作離不開各種訓(xùn)練。在啟動的時候需要做初始化的CA Training,Write Leveling,Read Leveling和 Write Eye Training等一系列訓(xùn)練,對于DDR4、LPDDR4及以上的更高協(xié)議,還需要VREF的二維訓(xùn)練。基于純硬件的方式無法提供復(fù)雜的訓(xùn)練范式。例如JEDEC的DDR4協(xié)議里面規(guī)定了DRAM只能提供簡單的01010101等范式, 這對于高速DDR的訓(xùn)練是不足夠的,因為這些范式頻率單一,無法反映數(shù)據(jù)通道衰減帶來的碼間串?dāng)_(ISI)。另外,不同范式在終端的反射也會不一樣。所以如果采用JEDEC規(guī)定的簡單范式來訓(xùn)練DDR,特別是在較高速率下,不能得到一個最優(yōu)化的訓(xùn)練結(jié)果。

芯耀輝的DDR PHY采用基于固件的訓(xùn)練方法,可以設(shè)置不同的范式,如PRBS范式、特殊設(shè)計的掃頻范式等。顯然此類范式能更全面的反映數(shù)據(jù)通道特性,因為它包含了高頻、中頻、低頻信息,以及長0和長1帶來的碼間串?dāng)_等問題,可以保證獲得更優(yōu)的訓(xùn)練結(jié)果。

初始化的訓(xùn)練完成之后,芯片內(nèi)部溫度和電壓會隨著工作狀態(tài)和環(huán)境溫度的變化而變化,此溫度和電壓的變化會讓訓(xùn)練的結(jié)果偏移理想值,使得DDR的讀寫裕量減小,嚴(yán)重的情況還會造成讀寫數(shù)據(jù)錯誤。芯耀輝開發(fā)了一種可以動態(tài)檢測芯片內(nèi)部溫度和電壓變化的技術(shù),通過實時補償各種訓(xùn)練結(jié)果,保證數(shù)據(jù)的讀寫具有足夠的裕量,確保DDR工作的穩(wěn)定性。

關(guān)鍵技術(shù)點三:高性能DDR IO設(shè)計

信號碼間串?dāng)_和走線的阻抗不匹配帶來的信號反射嚴(yán)重影響數(shù)據(jù)通信。為了保證DDR數(shù)據(jù)讀寫的可靠性,在DDR IO設(shè)計中,芯耀輝采用了FFE(前向反饋均衡)和DFE(判決反饋均衡)技術(shù)。

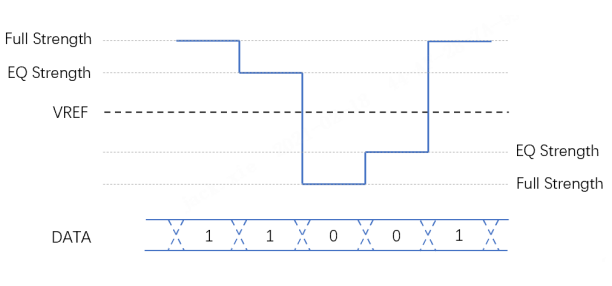

FFE 前端預(yù)均衡

FFE前端預(yù)均衡是在DDR TX端采用的技術(shù)。因為數(shù)據(jù)通道有衰減,使得信號高頻部分被抑制較大,低頻部分被抑制較小,所以在RX端看到的眼圖眼高和眼寬均比較小。FFE的思想就是減小低頻分量的能量,使得信號的高頻低頻部分在信道之后達到均衡。圖4展示了FFE原理,如果信號有0-》1的或者1-》0的變化,則輸出滿強度(Full Strength)的信號,如果信號是連續(xù)的1或者0,則輸出均衡強度的信號(EQ Strength)。

圖4 FFE前端預(yù)均衡原理示意圖

圖5 展示了在RX端,數(shù)據(jù)速率是6400Mbps時,關(guān)閉FFE和打開FFE的仿真示意圖。可以看到,打開FFE的眼圖質(zhì)量明顯好于關(guān)閉FFE的眼圖質(zhì)量。

圖5 芯耀輝仿真效果示意圖(6400Mbps),左圖沒有打開FFE,右圖打開FFE

芯耀輝采用可編程的前端預(yù)均衡方案,通過設(shè)置不同參數(shù)可以獲得不同的均衡效果,以適應(yīng)各種應(yīng)用場景的需要。

自適應(yīng)算法支持的接收端DFE(判決反饋均衡)

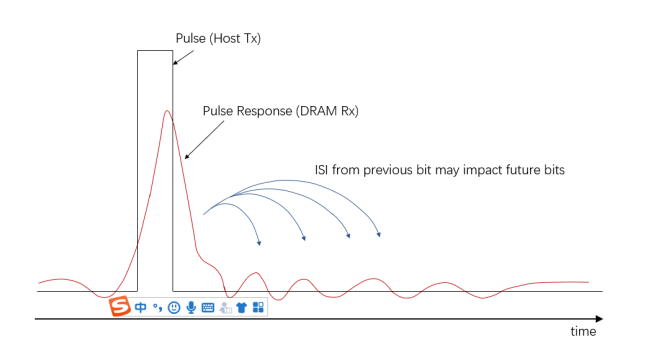

信號的碼間串?dāng)_可通過脈沖響應(yīng)(pulse response)示意圖理解,如下圖6所示。

圖6 經(jīng)過信道的脈沖響應(yīng)

當(dāng)脈沖信號經(jīng)過信道時,因為高頻衰減和信道反射,會形成一個拖尾的波形,前一個bit的信號會影響將來bit的信號質(zhì)量。DFE的原理是:判斷之前幾個bit的信號是1或者0,然后通過加權(quán)和反饋相加,減弱前bit信號的拖尾影響,以達到改善當(dāng)前bit信號質(zhì)量的目的。相比于CTLE等均衡技術(shù),DFE不會放大噪聲信號,因此固態(tài)技術(shù)協(xié)會在JEDEC79-5 規(guī)范中正式引入了DFE技術(shù),目的就是為了增強接收端的能力。

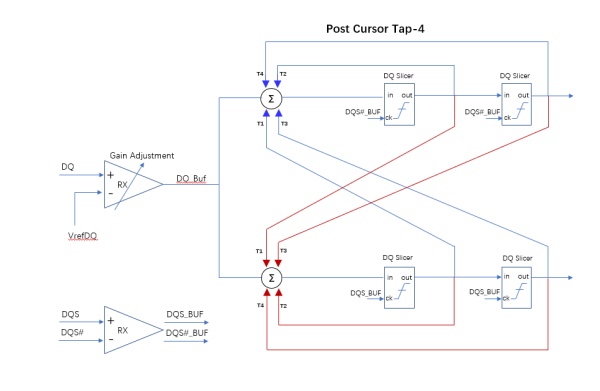

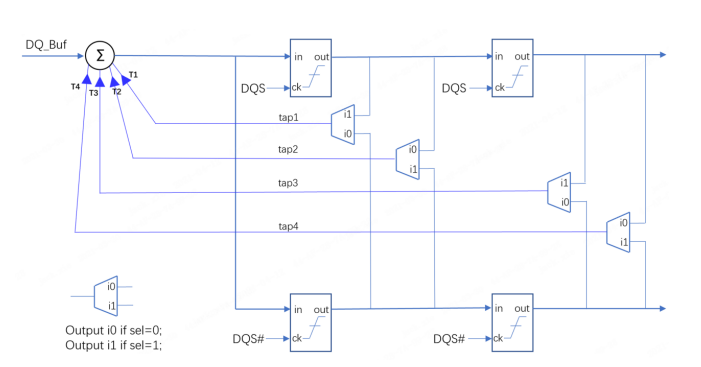

圖7是常見的4 tap DFE架構(gòu),也是JEDEC規(guī)范推薦的架構(gòu)之一。因為DQS的上升沿和下降沿均會采樣DQ,所以采樣電路分為上下兩個數(shù)據(jù)通路。兩個數(shù)據(jù)通路的4個采樣值經(jīng)過加權(quán)系數(shù)處理后會反饋到每一個數(shù)據(jù)通路對應(yīng)的求和器(∑),從而減去這4個之前信號對當(dāng)前信號的ISI影響。這種結(jié)構(gòu)采用了兩個求和器,會加大DQ_Buf端的負(fù)載。另外4個采樣值均需要直接反饋到兩個求和器,會使得芯片內(nèi)部連線比較復(fù)雜,影響高速性能。圖8是DFE的另一種架構(gòu),這種結(jié)構(gòu)通過MUX選擇兩路數(shù)據(jù)通路的采樣值,并把選擇后的值送到求和器進行EQ處理。因為只用到了一個求和器,減小了芯片內(nèi)部的連線復(fù)雜性,最重要的是減小了DQ_Buf端的負(fù)載,提升了高速性能。

圖7 常見的4-tap DFE架構(gòu)

圖8 另一種常見的4-tap DFE架構(gòu)

DFE各級tap的加權(quán)系數(shù)可以通過手動設(shè)置,前提條件是要得到信道的參數(shù),這樣做不適合產(chǎn)品的大規(guī)模量產(chǎn),因為對不同的產(chǎn)品來說,它的IO特性、信道參數(shù)是有隨機偏差的,同樣的一套設(shè)置不能保證每個產(chǎn)品都有最佳的DFE性能。通過自適應(yīng)訓(xùn)練得到DFE各級tap的系數(shù)是目前主流的方式。芯耀輝的DDR PHY提供了一套特殊的固件訓(xùn)練機制,DFE的各級tap的反饋系數(shù)可以通過訓(xùn)練快速得到,自適應(yīng)程度高,可保證每一顆芯片都有更優(yōu)的DFE性能,有效減小碼間串?dāng)_和反射造成的影響。

關(guān)鍵技術(shù)點四:支持多頻點的快速頻率切換技術(shù)實現(xiàn)低功耗設(shè)計

DDR是SoC系統(tǒng)中的功耗大戶,如何減小DDR的功耗一直是DDR技術(shù)革新的動力和方向之一。最直接的方法就是降低供電電壓,而這正是DRAM規(guī)范的演進之路。另一方面,從DDR4和LPDDR4開始,DRAM規(guī)范定義了POD IO 架構(gòu)(針對DDR4和DDR5)、LVSTL IO架構(gòu)(針對LPDDR4和LPDDR5)和數(shù)據(jù)總線倒置(DBI)技術(shù),能有效地減小IO端的功耗。

以上降低功耗的方法是JEDEC規(guī)范限定的技術(shù),芯耀輝還開發(fā)出一種動態(tài)頻率切換技術(shù),能有效降低系統(tǒng)總功耗。該技術(shù)在DRAM初始化的時候可以訓(xùn)練多達多個頻率點的配置,并保存相關(guān)訓(xùn)練結(jié)果。當(dāng)系統(tǒng)確定不需要DRAM工作在高頻率時,可以通知DDR控制器,然后DDR控制器會通知DFI,并讓DRAM進入自刷新狀態(tài),之后頻率切換就會自動在DFI和DDR PHY內(nèi)部進行,頻率切換完成之后DDR控制器則會讓DRAM退出自刷新,這樣DDR就可以切換到一個較低的工作頻率,從而降低功耗。相較于同類產(chǎn)品,該技術(shù)最大特點是整個過程無需固件接入,在新的頻率點無需重新做訓(xùn)練,從而快速穩(wěn)定地實現(xiàn)頻率切換。

總結(jié)

未來,市場對DDR PHY的需求持續(xù)增長,在先進制程上的需求更加突出。芯耀輝較早切入了基于FinFET工藝的IP開發(fā),通過不斷的技術(shù)創(chuàng)新,成為目前少數(shù)能提供先進制程、優(yōu)越性能,穩(wěn)定可靠的DDR PHY的本土企業(yè)之一。

百尺竿頭,更進一步,芯耀輝人必將以提供高性能的接口類IP,高品質(zhì)的設(shè)計服務(wù)為己任,奮發(fā)圖強,助力攜手合作廣大芯片設(shè)計公司及晶圓代工廠,推出更優(yōu)秀的產(chǎn)品,助力提升中國芯片產(chǎn)業(yè)的發(fā)展。

電子發(fā)燒友App

電子發(fā)燒友App

評論