MPPSK數字接收機位同步算法設計與實現

大小:3.43 MB 人氣:0 2017-12-21 需要積分:2

隨著社會技術和經濟的發展,迫切希望能實現多媒體數據高速傳輸,因而現代通信系統帶寬不斷增加,隨之而來的是無線頻譜資源的緊缺。高效調制技術能在單位時間內傳輸更多的信息,同時占用更窄的頻帶,因此研究高效調制技術具有重大的意義。

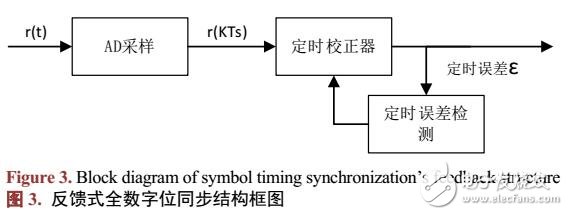

位同步又稱碼元同步,是數字通信接收機的重要組成部分。發端的消息是通過一連串碼元序列傳送的,接收時需要知道每個碼元的起始,以便在恰當的時刻進行取樣判決。所以接收端必須提供一個位定時脈沖序列,其重復頻率與碼元速率相同,相位與最佳取樣判決時刻一致,提取這種定時脈沖序列的過程稱為位同步。

本文首先介紹MPPSK調制與解調原理,再介紹數字接收機中的位同步系統。在分析傳統算法后提出雙窗實時位同步算法,介紹其實現結構,定時誤差占的計算和具體算法的實現流程。最后利用FPGA開發環境System Generator系統設計工具進行設計和仿真,介紹算法的具體Verilog實現,并與數字接收機系統聯調,驗證算法性能。

非常好我支持^.^

(0) 0%

不好我反對

(0) 0%