電子發燒友網【執行主編/莫延芬】:Cadence自1988年成立以來,一直采取積極的收購方式來獲取更多的EDA技術,截至目前共計數十余家企業納入Cadence麾下。早在2010年,Cadence便將業界知名Memory IP公司Denali收歸旗下。時至2011年,Cadence再刮并購風暴,繼IC設計和驗證方案廠商Azuro, Altos Design Automation, 及Sigrity均被Cadence買下;2013年,Cadence再度出手收購IP廠商Cosmic Circuits。

就在早前(2013年3月11日),Cadence再度以迅雷不及掩耳之勢,以3.8億美元重金收編業內快速成長中的IP黑馬——Tensilica。 那么,Cadence + Tensilica,強強聯合能否締造IP領域新機遇?若完成最終收購后,將如何進行雙方業務整合?存在哪些挑戰?FinFET技術面臨的挑戰與發展前景如何?鑒于此諸多未解之謎,我們專訪了Cadence 全球區域運營資深副總裁黃小立博士,揭開Cadence收購Tensilica內幕。

Cadence 全球區域運營資深副總裁黃小立博士指出,在高速布局的接口上已然完成后,Cadence又開始對高速數據處理有著濃厚的興趣。顯然,Tensilica就是Cadence最佳的搭配

電子發燒友網:作為全球電子設計創新的領導者,Cadence收購Tensilica是基于何種考量?此收購案最大的機遇在哪里?

黃小立:Cadence幾年前進入IP領域。從最開始,Cadence就有一個很強的理念:Cadence要做對SOC高價值、有差異化的IP。這才是最大化Cadence股東的回報和對設計者的幫助。

幾年前,也有過類似的收購,上次收購的公司在Memory接口領先,為什么Cadence會從這個接口進入呢?因為SOC處理器方面,ARM等廠家做得很好。但是SOC很多計算系統,SOC做的越來越快,核做的越來越多。因此,它和Memory接口會有一個很大的瓶頸。所以Cadence第一步就進入了DDR,Memory接口領域。此后,通過Cadence內部投資和能力,開發了更多的高速數據接口, 例如PCIe。高速數據接口SOC是一個很大的挑戰。

在春節前后,Cadence收購以一家印度小公司Cosmic Circuits,讓Cadence在MIPI和USB這兩個高速接口上又有很好的布局。

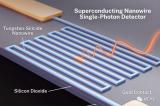

在高速布局的接口上已然成熟后,Cadence又開始對高速數據處理有著濃厚的興趣。Tensilica就是Cadence的最佳搭配。因為在任何一個SOC里面,普通的軟件可以通過通用處理器去實現,但是有很多高速低功耗要求能夠快速處理一下專用的算法和數據,如音頻、視頻和2.5G、4G和LTE方面,這是Tensilica IP的強項。

鑒于此,通過對Tensilica公司的收購,Cadence就能順理成章地進入高速數據處理領域。通過高速數據接口和高速數據處理,Cadence能夠給設計者帶來最大的效益和最大的差異化。此次收購是對Cadence IP產品組合上完整的補充。

電子發燒友網:若完成最終收購后,將如何進行雙方業務整合?存在哪些挑戰?目前為止,客戶的反應如何?如何解決目前產品的重合問題?產品路線圖是怎樣的?

黃小立:任何一個業務整合都會有一個難點。但是對于這個,Cadence正好充滿信心。因為Tensilica與Cadence重復重疊的東西很少。Cadence的IP業務剛開始幾年,急需找一些在IP領域有豐富經驗的團隊,Tensilica就是一個很好的團隊。Tensilica的IP和Cadence現有的IP完全是互補的,沒有任何的重合。所以從技術上來講,這相當于是個完美的婚姻。

當然兩個公司,Cadence作為一個幾十年的大公司、而Tensilica是一個僅有十幾年的小公司,在公司文化上還是會有一些不一樣。但是Cadence公司這些年經常會收購一些中小型的公司,Cadence有豐富的并購整合經驗。因此,Cadence對此次整合還是充滿信心的。

到目前為止,客戶反映還是很正面的。因為此次收購能給客戶帶來更好更完整的軟件和IP解決方案。Cadence雄厚的資金和技術支持,會給Tensilica將來發展Roadmap帶來了很大的信心。

Roadmap產品路線方面還沒有完全形成,具體要在并購完成以后,可能有經過1-2個月才能重新部署。但是如果像小公司力量比較單薄,如在中國覆蓋率比較少,在美國日本覆蓋率比較大。那么,Cadence就可以覆蓋更多的市場、更多產品。這是Cadence初步想法。Cadence目前不準備取消任何的Roadmap,只會更強大。

電子發燒友網:隨著時間的推移,特別是伴隨著下一代移動消費電子設備發展,我們有理由更加期待FinFET技術。然而,據相關機構預測,16nm/14nm FinFET器件的量產還需要一到兩年,并且還有許多關于FinFET器件的成本和收益的未知變數。同時也帶來了一些新的設計挑戰,它的成功,將需要大量的研發和整個半導體設計生態系統的深層次合作。請談一下FinFET技術面臨的挑戰與發展前景以及Cadence公司的有針對性的戰略部署。

黃小立:其實每一次半導體節點的更新都是一個大挑戰,而且每次挑戰都會愈加加劇。很不幸的是,每一次挑戰獲得的收益相對來說比較少,過去一個節點能夠跳一倍,較少的投入就能獲得相當的收益。但是,現在情況恰恰相反,一個節點花很多時間和金錢,但收益也不過百分之幾十。鑒于此,現在業內業者也都在討論摩爾定律遇到瓶頸的問題。這也是個不爭的事實。那么,很幸運的是,Cadence公司這幾年的業務還是做得比較順利的,有強大的資金和技術積累。如這次收購案,Cadence是用現金收購Tensilica的。其實Cadence不只花錢買IP公司、開發IP,Cadence還在EDA Solution方面花了很大的力氣。

在20納米平面型晶體管之后,是什么?

幾個月前,Cadence曾跟ARM、IBM發布了一個Test Chip,還有一個是跟三星一起發布的。這兩個很有意思。以前做Test Chip很簡單,現在做Test Chip做得相當大規模。和三星做14nm的是基于ARM Cortex-A7。在這,我想表達的是,我們是EDA Solution比較早發布14nm的ARM核的。此外,這兩個都是3個廠商共同合作的,Foundries、IP、EDA這是一個很完美的組合。過去很單一化的,Foundries把工藝做完以后,把它交給IP公司開發Library,Library開發完以后就把它交給第三家公司把這個東西做出來。現在該流程已經難以為繼,Cadence與Foundries、IP公司都有非常成熟的組合,以至于經常會出現Foundries和Process在設計上會產生分歧,最終得依靠工具廠商進行評估其良品率。當前,不僅僅看良品率好不好,還要看采取不同的生產方式對設計會產生什么效果。通過EDA去做幾個設計,然后再來看良品率、或漏電、power是不是都很好。這種合作是原來從來沒有見過的。

前年ARM發表A15的時候,正好是TSMC在做20nm的時候,所以Cadence、ARM、TSMC三方一起做了個A15 20nm的芯片。

現在的工藝不再是只是做一個簡單的電路測試就可以認為這種工藝就可以做產品。一定要把這種工藝的設想通過IP、設計工具實現了以后去做一些真正的電路,如ARM核最終能不能實現,整個過程是一個很強的優化過程。當然,Cadence不是唯一一家這樣做的EDA公司,但能夠全方位的對各個Foundries深度的投資合作,Cadence是其中之一。

電子發燒友網:剛才說到三家公司合作的方式去開發一個節點工藝,那這樣對Cadence會不會有工具上的需求?會不會促進對工具商工具的補充?

黃小立:當然,這是一定的。Foundries廠商通過使用Cadence的工具去“練兵”,能更好地改進工藝。Cadence也一樣,工藝不斷地在成熟,Cadence也需要不斷地促進工具愈發完善。就像剛說的量產時間,一般產品研發到量產是需要很長一段時間的。量產一個是良率的提高,另外一個是工具和IP的不斷完善。

電子發燒友網:到目前為止,基于三方這種創新性的合作,客戶有何評價?

黃小立:客戶都很感興趣、很關心。客戶希望產業鏈能結合在一起做出讓用戶放心的產品。

電子發燒友網:如果FinFET得到普及,那么,如何評價20納米平面型晶體管的市場價值?

黃小立:業界都有一個猜想:因為FinFET 14nm上的很快,因此可能20nm會較快地過渡到FinFET。

會有多少會做20nm,我想大家都在觀望,都在看16nm/14nm FinFET的應用快不快。個人觀點認為,過去是每個節點每個公司跳一次,現在可能是每個節點不少公司停一次。也就是說,現在做20nm的以前有些可能沒有做28nm、32nm的,也許是以前做40nm、65nm的。可能由于時間等的太長,所以就直接跳到20nm。因此,現在在做28nm、32nm的,可能也會跳過20nm。這些都取決于具體的公司現在處于什么位置以及它的競爭對手現在處于什么樣的位置,這才決定要不要跳過20nm這個節點。

其實過去這些也有過類似的情形,比如在美國的大的fabless公司,就曾跳過90nm,直接做65nm的。它們也是基于這樣的考慮。

電子發燒友網:ARM 總裁Simon Segars曾表示“Cadence收購Tensilica對整個行業來說將是一個積極舉措”,Cadence對此作何評價?

黃小立:ARM對我們這個聯盟關系很重視,同時我們也很重視。我們雙方這幾年走得很近。Cadence這幾年做的一些Test Chip,很多是和ARM一起完成的。Cadence也很珍惜這樣的合作關系。

在收購之前,Cadence也對該產業進行了深入研究。當然,從某種意義上來說,Tensilica是一個處理器,ARM也是處理器。但是我們都同意這個觀點,ARM是比較通用的程序、不需要很大的CPU的功能(如看天氣、看股票、Email等)。但是有一些東西是專用高速數據處理,包括打電話、上網、視音頻處理,這些是可以用軟件處理但功耗和時間上會比較大,所以業界就把這樣一些功能定義為“DPU”。個人以為, ARM也是出于這樣的考慮,對Cadence收購Tensilica表示支持,不會應此影響雙方的合作關系,更不會因此造成對下游客戶的影響。如果Cadence和ARM之間缺乏溝通,肯定會給客戶造成一些不好的影響。

所以Cadence希望用戶不會有這樣的疑慮,Cadence也很感激ARM出來澄清這樣的事實。

電子發燒友網:隨著智能化,SoC,FPGA+ARM核架構的應用趨勢日益明朗。Tensilica收購案對此有何互補作用?未來,我們應重點關注Cadence和ARM哪方面的合作?

黃小立:Tensilica收購案對此有較強互補作用。因為越往下走,邏輯的工藝(工藝無非是Memory、Flash和Logic)就越來越復雜。所以大家就想到不要什么東西都用邏輯工藝去做,因此就選用ARM Cortex架構。ARM Cortex有一些很專用的算法做不了,做不了的時候如果用邏輯去做的話,就不太容易調整和改動。另外,還可以用軟件在特殊的處理器上實現。將來通用處理器越跑越快,是不是就不需要專用處理器了?我個人不這么覺得。專用處理器在功耗和尺寸上永遠要比通用處理器有優勢。所以市場對這方面的需求還是永遠都會有的。

我相信Cadence和ARM會有更多緊密合作。我們雙方的合作從幾年前才剛開始,所以現在大家看到的東西還只是一些初步的合作。個人認為,雙方在建立更強的信任以后,我們將來會有更好的配合,比如Roadmaps,他們開發什么樣的IP、Library,我們就開發什么樣的工具。在經過這幾年的磨合以后,我們會有更大的合作機會。現在我們公布了在FinFET項目和IBM、ARM以及Foundry的一些合作成果。

在高集成度與IC測試/驗證難度不斷加大壓力前,很多此前具有IP設計和IC測試能力的芯片原廠現在也難以為繼,這就給EDA巨頭們帶來巨大商機,并購已然成為最直接的競爭手段

電子發燒友網:Cadence通過種種收購來不斷完善自己的產品線,會不會對ARM構成競爭威脅?

黃小立:不會,ARM對開發工具方面沒有表現出興趣。Cadence和ARM合作得很好。Cadence要做高速數據處理,ARM也作了以上表述,那就表明目前不會涉及該領域。

電子發燒友網:Cadence收購Tensilica,會以一個什么樣的模式進行管理?

黃小立:以產品線的方式進行管理。其銷售和服務將會捆綁在一起,公司內部研發將成立一個事業部。具體會在IP部門下再加一個部門。

電子發燒友網:2013年,Cadence關注的重點領域是哪些?

黃小立:Cadence這幾年在IP上很多投入將會逐漸的反應在市場上;在FinFET方面,會有更多的好消息;關于DPU,Cadence會拼力將其部署到全球各地。

專訪后記

實際上,當前隨著摩爾定律的不斷深入下探,20nm以及小于20nm先進節點的高性能IC設計與16nm/14nm FinFET、3D IC相關的先進技術涉及到從系統設計驗證、芯片實現到三維封裝設計已然非常復雜。在高集成度與IC測試/驗證難度不斷加大壓力前,很多此前具有IP設計和IC測試能力的芯片原廠現在也難以為繼。這就給EDA巨頭們帶來巨大商機,并購已然成為最直接的競爭手段。半導體相對其他產業來說仍算年輕,其中IP產業時間更短,而要走向較穩定的階段,則必然會出現整并,剩下幾個大的廠商相互競爭,而近年包括Cadence、ARM、Synopsys及Mentor等公司,都進行過幾起并購案,顯示產業正逐漸走向成熟階段。

此外,隨著增速放緩,我們相信中小型IP供應商要準備好收購與被收購,合并已成為IP供應商拓展規模立足市場的重要戰略。

黃小立博士在闡述個人觀點、公司策略及分享產業市場趨勢時,始終保持著不急不緩的語速,令聽者如沐春風,極具個人魅力的談吐更體現出黃博士儒雅穩重的處事風格,這與Cadence在市場中保持紳士風度,從而低調穩健推廣其產品戰略方式是相一致的。

電子發燒友網執行主編/莫延芬

?

電子發燒友App

電子發燒友App

評論