正文:

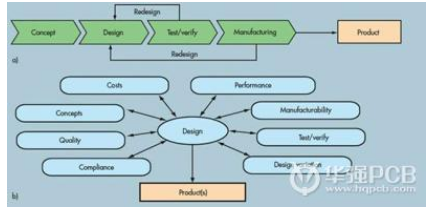

電子產(chǎn)業(yè)在摩爾定律的驅(qū)動下,產(chǎn)品的功能越來越強(qiáng),集成度越來越高、信號的速率越來越快,產(chǎn)品的研發(fā)周期也越來越短,PCB的設(shè)計也隨之進(jìn)入了高速 PCB設(shè)計時代。PCB不再僅僅是完成互連功能的載體,而是作為所有電子產(chǎn)品中一個極為重要的部件。本文從高性能PCB設(shè)計的工程實現(xiàn)的角度,全面剖析 IT行業(yè)高性能PCB設(shè)計的方方面面。實現(xiàn)高性能的PCB設(shè)計首先要有一支高素質(zhì)的PCB設(shè)計團(tuán)隊。

一、PCB設(shè)計團(tuán)隊的組建建議

自從PCB設(shè)計進(jìn)入高速時代,原理圖、PCB設(shè)計由硬件工程師全權(quán)負(fù)責(zé)的做法就一去不復(fù)返了,專職的PCB工程師也就應(yīng)運而生。

一個成熟的大、中型PCB設(shè)計團(tuán)隊的構(gòu)成應(yīng)包括以下幾個工種:

封裝庫工程師:專職建庫,熟知當(dāng)今主流板廠、貼片廠商的工藝能力、技術(shù)參數(shù),結(jié)合本公司的產(chǎn)品實際,并據(jù)此完成當(dāng)前高速高密條件下的PCB封裝建庫工作。

PCB設(shè)計工程師:設(shè)計人員必須具備廣泛的PCB周邊知識,諸如電子線路的基本知識,PCB的生產(chǎn)、貼片加工的基本常識,DFX(DFM/DFC /DFT)設(shè)計,同時還需要掌握高速PCB的層疊設(shè)計、阻抗設(shè)計、信號完整性知識、EMC知識等,綜合考慮現(xiàn)代PCB設(shè)計的各項要求,完成PCB的布局、 布線工作。

SI工程師:揭開隱藏在PCB傳輸線里的“隱性原理圖”,直面高速時代的反射、串?dāng)_、時序問題。通過前后仿真,確保信號質(zhì)量,提升產(chǎn)品的一次成功率,確保PCB穩(wěn)定、可靠的工作。

EMC工程師:作為EMC設(shè)計的源頭考慮,負(fù)責(zé)包括電路、器件、PCB相關(guān)的板級EMC設(shè)計。降低自身的對外輻射,并提高抗外界干擾的能力。

熱設(shè)計工程師:在追求精美、小巧的產(chǎn)品研發(fā)團(tuán)隊里,熱設(shè)計工程師不可或缺。通過熱源分布分析、設(shè)計合理的風(fēng)道系統(tǒng),控制系統(tǒng)的溫升,確保產(chǎn)品的穩(wěn) 定、可靠工作。很難想象一個筆記本的設(shè)計團(tuán)隊沒有熱設(shè)計工程師的參與能做出可靠、穩(wěn)定的筆記本產(chǎn)品。(注:部分公司由結(jié)構(gòu)工程師兼負(fù)PCB的熱仿真、熱設(shè) 計)。

工藝工程師:針對本公司的PCB加工廠商、貼片設(shè)備/廠商的工藝能力,制定本公司PCB設(shè)計的工藝參數(shù)。參與具體單板、PCB的設(shè)計,確保PCB的可生產(chǎn)性、可加工性。

考慮到自身交流、技術(shù)提升、人員備份的需要,以上每個工種至少不低于3人。對于自身團(tuán)隊規(guī)模有限、研發(fā)需求起伏較大的公司,適當(dāng)儲備一些復(fù)合型的多面手并根據(jù)自身需要適當(dāng)尋求外部資源是解決自身研發(fā)短木板的明智之舉。

我們來看看IT行業(yè)巨頭們的PCB設(shè)計團(tuán)隊組建歷程:

1980年,公司內(nèi)部硬件工程師兼做PCB設(shè)計;

1990年,CAD工程師作為專門的部門逐漸獨立出來;

1995年,專業(yè)的PCB DESIGN HOUSE在北美、日本開始流行

2000年,專業(yè)化分工越來越細(xì),建庫、PCB設(shè)計、SI、EMC、熱設(shè)計、工藝等工種逐漸獨立;北美、日本的PCB設(shè)計有50%以上由專業(yè)的設(shè)計公司完成;SI、EMC等工種逐漸自成體系;

2003年,一博科技為首的專業(yè)設(shè)計公司把PCB設(shè)計外包理念帶入中國;

2008年,公司內(nèi)部分工明確,工種齊全。并合理采用資源外包、錯峰設(shè)計、技術(shù)外包成為潮流。

二、高性能PCB設(shè)計的硬件必備基礎(chǔ)

自從PCB設(shè)計進(jìn)入高速時代,以傳輸線理論為基礎(chǔ)的信號完整性知識勢頭蓋過了硬件基礎(chǔ)知識。有人提出,十年后的硬件設(shè)計只有前端和后端(前端指的是 IC設(shè)計,后端指的是PCB設(shè)計)。只要有一個系統(tǒng)工程師把他們整合一下就夠了。這很容易讓人懷疑學(xué)習(xí)硬件基礎(chǔ)知識的必要性。事實上,不管是IC工程師還 是PCB工程師,都必須具備諸如R、L、C以及基本的門電路知識。

高性能的PCB設(shè)計離不開電源基礎(chǔ)知識,少不了FPGA常識。即使以傳輸線理論為基礎(chǔ)的信號完整性分析也是從研究以R、L、C為基礎(chǔ)的微元考慮。

PCB設(shè)計工程師必須具備基本的電路基本知識,如高頻、低頻、數(shù)字電路、微波、電磁場與電磁波等。熟悉并了解所設(shè)計產(chǎn)品的基本功能及硬件基礎(chǔ)知識,是完成一個高性能的PCB設(shè)計的基本條件。

三、高性能PCB設(shè)計面臨的挑戰(zhàn)和工程實現(xiàn)

PCB設(shè)計是一門沒有最好只有更好的藝術(shù),一個性能優(yōu)良的PCB設(shè)計,常常面臨以下挑戰(zhàn)。

1.研發(fā)周期的挑戰(zhàn)

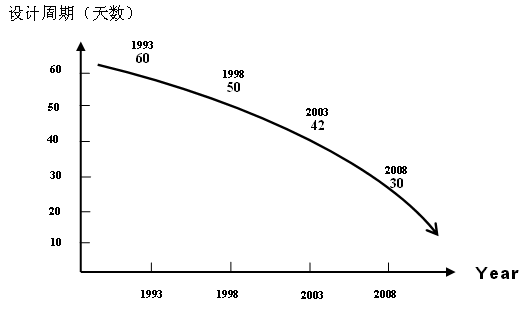

統(tǒng)計數(shù)據(jù)表明,一臺筆記本的設(shè)計,從立項到上市,一般只有半年的時間。一款手機(jī)的研發(fā),從立項到上市,平均只有3個月的時間。作為產(chǎn)品研發(fā)中的重要一環(huán),PCB設(shè)計時間也逐漸被壓縮、壓縮再壓縮。

1985年4月,東芝公司溝口哲也工程師設(shè)計出了一臺命名為T1100袖珍的機(jī)器,引領(lǐng)了計算機(jī)行業(yè)的興起。自那以后,計算機(jī)主板的研發(fā)周期也明顯加快了節(jié)奏。

圖1:計算機(jī)主板設(shè)計周期的變遷

在EDADOC,筆記本的PCB設(shè)計基本控制在三周以內(nèi),手機(jī)的PCB設(shè)計時間一般客戶的預(yù)期時間是10天。

面臨市場不斷縮短的研發(fā)預(yù)期,PCB工程師如何面臨這一挑戰(zhàn)呢?

首先,要采用一流的EDA工具軟件

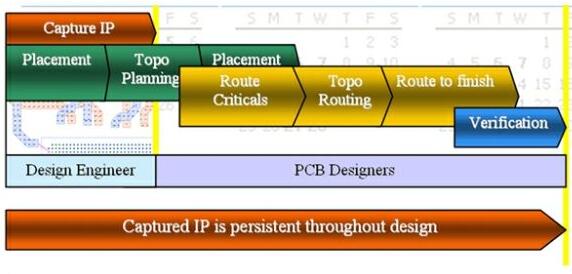

高效的EDA工具軟件帶來的不僅僅是效率的提高,更是設(shè)計理念的革命。在眾多的EDA工具軟件中,Cadence的PSD系列無疑占據(jù)著行業(yè)旗艦的角色。從10年前的單兵作戰(zhàn),到后來的“sub-drawing”,再到如今的“partition”,Cadence Allegro提供的多人并行設(shè)計把原本不可能的研發(fā)周期變成現(xiàn)實。在EDADOC,92%的PCB設(shè)計都會用到并行設(shè)計。

舉例來說,EDADOC曾在6天的時間里完成20000PIN的某XDSL單板的前后仿真、布局、布線工作,這其中,并行設(shè)計居功至偉。

以一個常規(guī)的筆記本主板PCB設(shè)計為例,我們來看看傳統(tǒng)的“單兵作戰(zhàn)”(一個PCB工程師負(fù)責(zé))以及在部分公司采納的3班倒的工作模式以及采用并行設(shè)計的工作方式下的主體PCB設(shè)計數(shù)據(jù):

工作方式單兵作戰(zhàn)3人接力3班倒并行設(shè)計

設(shè)計時間30天18天15天

優(yōu)點單人負(fù)責(zé),中途無交接,溝通成本低交期較快、多人智慧交期靈活,容易控制,多人同時工作,易于溝通。多人智慧。

缺點周期長,知識面受限工程師難以接受,夜班效率低,與周邊資源溝通不便,3次交接,傳遞效率低要求具備一定的團(tuán)隊規(guī)模,人員效率略為下降。

適用范圍適用于小型公司或簡單單板。無需與周邊資源的溝通,復(fù)雜單板,特例情況下和并行設(shè)計配合使用復(fù)雜或較復(fù)雜單板,設(shè)計周期短。廣泛應(yīng)用于大中型EDA團(tuán)隊

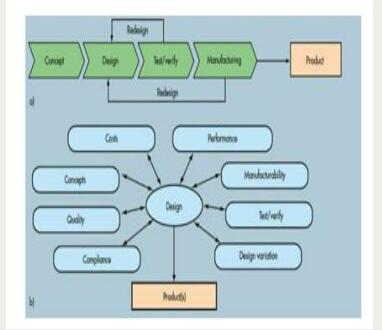

其次,提前介入產(chǎn)品研發(fā)流程,減少后續(xù)返工。

在總體方案設(shè)計階段,PCB工程師即介入研發(fā),重點參與產(chǎn)品的系統(tǒng)架構(gòu)設(shè)計、論證;在總體設(shè)計階段,開展初期PCB設(shè)計可行性評估;在詳細(xì)設(shè)計階段,同步原理方案設(shè)計,參與器件選型、結(jié)構(gòu)設(shè)計、熱設(shè)計,這樣當(dāng)研發(fā)進(jìn)入PCB設(shè)計流程后,主體工作便簡化了,同時減少了因器件體積過大、驅(qū)動能力不夠、拓?fù)浞桨覆豢尚幸约敖Y(jié)構(gòu)散熱等問題帶來的PCB設(shè)計過程中的返工。

第三,“一板成功”的設(shè)計理念

IBM的高級顧問曾指出國內(nèi)某研發(fā)團(tuán)隊存在的問題:“沒有時間把事情一次性做好,但卻有時間把事情一做再做”,在當(dāng)前的市場競爭環(huán)境下,擁有經(jīng)驗豐富的PCB設(shè)計工程師,健全設(shè)計流程,并借助各種工具軟件,力爭一板成功。節(jié)省的不僅僅是少做了一板PCB的費用,更是節(jié)省了一個全流程的研發(fā)周期。為產(chǎn)品贏得市場機(jī)會窗。不管是PCB工程師自身,還是產(chǎn)品研發(fā)主管,都必須具備PCB研發(fā)“一板成功”的理念。

最后,模塊重用,重視技術(shù)沉淀

在筆者接觸的多家國內(nèi)知名公司,他們非常重視模塊重用,在確保技術(shù)沉淀的同時,也有效的縮短了PCB設(shè)計時間。

總之,我們要在設(shè)計理念上,提前介入研發(fā),采用并行設(shè)計,采納一板成功、減少研發(fā)次數(shù)的理念,加上諸如Cadence PSD的先進(jìn)工具軟件,我們不需要過度加班,更不需要兩班乃至三班倒即可解決PCB的研發(fā)周期問題。

2.成本的挑戰(zhàn)

PCB的成本包括顯性成本和隱性成本

顯性成本主要包括PCB的生產(chǎn)、貼片成本。

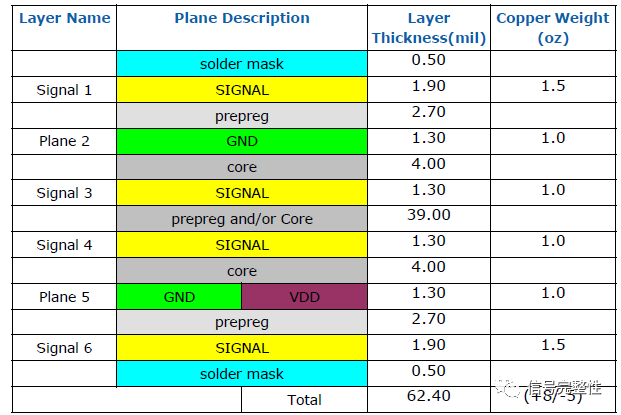

對于顯性成本的控制,我們可以通過熟悉、了解常規(guī)板廠的工藝能力、貼片設(shè)備的工藝要求,選擇合理的層數(shù)、設(shè)置合理的層疊結(jié)構(gòu)、設(shè)計參數(shù)來降低PCB設(shè)計的顯性成本。

隱性成本包括PCB設(shè)計期間的人員投入、技術(shù)風(fēng)險、時間成本尤其是上市機(jī)會窗的機(jī)會成本。

而事實上,PCB設(shè)計的隱性成本遠(yuǎn)遠(yuǎn)大于其顯性成本。

舉例來說,一般手機(jī)的市場機(jī)會窗也就是半年左右,如果因為PCB設(shè)計的問題增加一次研發(fā),對于流行時尚的手機(jī)產(chǎn)品來說帶來的不僅僅是1-2個月的時間損失,更是整個產(chǎn)品的失敗。

對于隱性成本的控制,公司高層和研發(fā)主管要具備抓緊核心、放開周邊、強(qiáng)強(qiáng)組合、一次成功的理念,在設(shè)計之初考慮成本。合理借助外部資源,解決自身研發(fā)的短木板問題,降低產(chǎn)品研發(fā)的隱性成本。

3.高速的挑戰(zhàn)

隨著信號速率的不斷提升,信號完整性不斷困擾著研發(fā)人員,包括總線驅(qū)動能力、信號的反射、串?dāng)_、過沖、振蕩、回溝、衰減等;有時也把時序劃歸到信號完整性范圍內(nèi)。Allegro中基于IBIS模型的仿真模塊Signoise,可以方便地搭建拓?fù)溥M(jìn)行仿真。

Allegro的這個仿真工具與布線平臺有良好的接口,在PCB布線完成以后,還可以從PCB板上直接提取布線參數(shù)到Signoise平臺中,進(jìn)行后仿真以驗證布線的效果。

仿真提取的布線約束可以直接導(dǎo)入到Allegro的電氣規(guī)則管理器中,這個管理器可以方便地對時序要求的等長規(guī)則進(jìn)行約束,在布線時,當(dāng)長度不符合所規(guī)定的規(guī)則時,Allegro可以實時進(jìn)行告警。

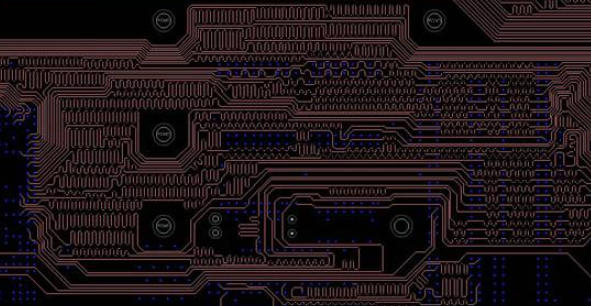

圖2:規(guī)則管理器示例(點擊圖片看大圖)

如圖所示,當(dāng)長度在預(yù)定的范圍之內(nèi)的時候,表格中相應(yīng)的區(qū)域顯示綠色;當(dāng)長度不在預(yù)定的范圍內(nèi),不管是偏短還是偏長,表格的相應(yīng)區(qū)域都顯示為紅色。

4.高密的挑戰(zhàn)

我們來看看一組數(shù)據(jù):

近年來器件封裝的變遷:

過去20年IT行業(yè)單個器件PIN數(shù)目以及單塊單板PIN總數(shù)的變遷:

圖3:單個器件PIN數(shù)目以及單塊單板PIN總數(shù)的變遷

過去20年IT行業(yè)單板層數(shù)的變遷:

圖4:單板層數(shù)的變遷

過去20年單板PIN密度(Pin density, Pins/sq in):的變遷:

圖5:單板PIN密度的變遷

上述的數(shù)據(jù)里面我們能深刻的感受到PCB設(shè)計密度越來越高的壓力,從20年前的跳線滿板飛,發(fā)展到后來的雙面板、多層板,再到器件封裝的變遷,以及近幾年手機(jī)產(chǎn)業(yè)推動的HDI技術(shù)興起,包括近期Intel推出的Menlow平臺,更是把HDI技術(shù)帶到了PC行業(yè)。

面對PCB設(shè)計的密度的不斷提升,PCB工程師必須緊跟業(yè)界前沿,了解新材料、新工藝,采用能支撐高密PCB設(shè)計的一流EDA軟件,這樣才能滿足產(chǎn)品研發(fā)過程中面臨的密度越來越高的挑戰(zhàn)。據(jù)稱,即將推出的PSD 16.2在HDI的設(shè)計上將有較大的突破,期待中。

5.電源、地噪聲的挑戰(zhàn)

電源、地平面作為信號線的參考平面、回流通道,電源、地的噪聲會直接串入以其為參考平面的信號。解決電源、地噪聲的問題,不僅僅是考慮供電電源的自身電平穩(wěn)定問題,還是解決高速信號的可靠性問題的重要因素。

高速PCB的電源設(shè)計首先要理清電源樹,分析電源通道合理性。

首先,在大電流的載流能力上,必須在考慮裕量的前提下分配恰當(dāng)?shù)牟季€寬度;同時,因為實際布線有電阻,從電源輸出端到實際負(fù)載的路線上有壓降,而高 速電路器件的電壓特別是core電壓往往很低,壓降對供電效果有直接的影響。電流的載流能力,與線寬、內(nèi)外層、銅厚度、允許溫升相關(guān)。

其次,在電源的濾波效果上,需要考慮電源的阻抗。因為電源通道實際上不是一個理想的通道,而是有電阻和阻抗的,高速電路在門電路翻轉(zhuǎn)時需要瞬間的電源供給,而電流從電源模塊給各個門電路翻轉(zhuǎn)提供能量是需要各級路徑分配的,需要時間,這可理解為一個分級充電的過程,

圖6:門電路翻轉(zhuǎn)供電路徑

可以看到,在高頻狀態(tài)下,器件管腳上的電流首先是由電源、地平面組成的平板電容來供電的,因為由他們組成的供電系統(tǒng)阻抗最低。供電速度最快,但是, 這個平板電容存儲的電量太小,他們的電荷由小的濾波電容提供,小濾波電容的電荷再由大的BULK儲能電容提供,然后開關(guān)電源通過電流通道給BULK電容充 電,之所以這樣,是因為開關(guān)電源僅在幾K的頻率下是低阻抗的、BULK電容僅在幾兆的頻率下是低阻抗的,小濾波電容僅在幾十兆到幾百兆的頻率下是低阻抗 的,電流只有通過層層充電,才能到達(dá)器件管腳,滿足瞬時供電的需要。Cadence也提供了一個PI分析模塊,來分析在不同的功耗下電源平面的阻抗,以及 濾波電容的選擇是否合理。

這個PI仿真工具的理論基礎(chǔ)是傳輸線,采用有限元的方式對電源平面進(jìn)行劃分,把電源和相應(yīng)的地平面匹配成一對平板電容,并劃分成幾個區(qū)域,如圖所示:

工具采用頻域分析的方式,板上各個小塊的阻抗進(jìn)行分析,最后得到各點的阻抗圖:

如果發(fā)現(xiàn)某個區(qū)域的點的阻抗在目標(biāo)阻抗以上,就通過重新分配電源平面,或增加濾波電容,降低這個點的目標(biāo)阻抗,增強(qiáng)對器件管腳的濾波能力。

6.EMC問題:

隨著人們生活水平的提高以及對包括電磁污染在內(nèi)的環(huán)保的關(guān)注,EMC問題成為所有電子產(chǎn)品研發(fā)中繞不過去的彎。作為一個“Black Magic”,EMC問題越來越困擾開發(fā)人員。

EMC要從源頭設(shè)計。作為產(chǎn)品EMC的源頭,單板/PCB的EMC性能愈發(fā)引起關(guān)注,在EMC眾多的指標(biāo)中,最讓硬件工程師頭痛的是RE指標(biāo)問題。

出于模型的限制,即使業(yè)界公認(rèn)的頂級EMC仿真軟件,至今也不能仿真出和實際測試數(shù)據(jù)可比擬的數(shù)據(jù)出來。其只能給出某些特定條件下的簡化了的單輻射源的輻射場分布情況,進(jìn)而提供設(shè)計參考。

EMC 設(shè)計至今主要還是靠EMC工程師/硬件工程師的經(jīng)驗來開展設(shè)計。作為工程設(shè)計,我們無需作過多的理論分析,但我們必須具備一些常規(guī)的工程設(shè)計經(jīng)驗。同時借 助一些近場探頭等輔助手段來解決EMC問題。上圖為借助近場探頭測出的RE指標(biāo)以及特定頻率的EMI物理空間分部圖。

以筆者的意見,以PCB為主的單板EMC問題,我們需要把主要精力集中在以下三個方面:

1)電源

2)時鐘(及其它強(qiáng)輻射源)

3)接口電路

提及電源,我們考慮的是電源(地)的完整性問題以及作為回流通道的電源地設(shè)計;

時鐘作為單板的主要EMI源,承擔(dān)了60%以上的主要EMI源;

疏忽任意一個接口的設(shè)計,你整個產(chǎn)品的EMC努力都有可能前功盡棄。

作為工程實現(xiàn),只要圍繞上述3點作文章,整個產(chǎn)品的EMC問題也就成功在望了。

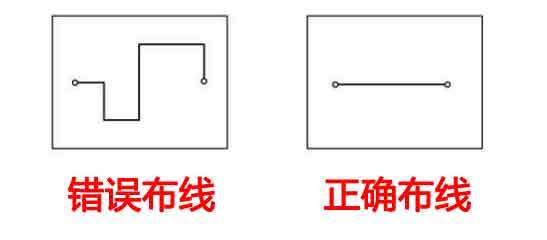

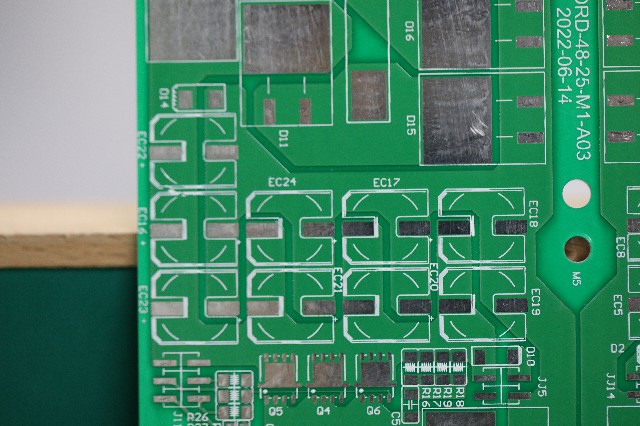

7.DFM的挑戰(zhàn)

解決DFM問題,除了單板工藝工程師制定適合本公司的工藝標(biāo)準(zhǔn)外,需要對PCB設(shè)計工程師進(jìn)行系統(tǒng)、全面的DFM常識培訓(xùn),PCB工程師需要不斷了 解業(yè)界的PCB生產(chǎn)加工能力現(xiàn)狀,結(jié)合本公司的實際情況,選擇合適的工藝路線和設(shè)計參數(shù)。在電氣性能和DFM方面的取舍上,綜合考慮。此外,在PCB的封 裝庫上,必須有專職的建庫人員,從源頭上解決DFM問題。

Allegro有一個專用的建庫模塊,可以按器件的datasheet方便地設(shè)計封裝庫,以及封裝庫的焊盤。良好的封裝設(shè)計是DFM設(shè)計的基礎(chǔ)。

作為高性能的PCB設(shè)計,這些挑戰(zhàn)有時是互相矛盾的要求,PCB設(shè)計工程師需要利用自己的全面經(jīng)驗,在這些挑戰(zhàn)面前折衷考慮,尋找一個最佳的結(jié)合點,最終完成高性能的PCB設(shè)計的工程實現(xiàn)。

四、工欲善其事,必先利其器

高性能的PCB設(shè)計離不開先進(jìn)的EDA工具軟件的支撐。Cadence的PSD系列在高速PCB設(shè)計方面的強(qiáng)大功能,其前后仿真模塊,確保信號質(zhì) 量,提升產(chǎn)品的一次成功率;其物理、電氣規(guī)則的使用,可智能化的實現(xiàn)諸如差分布線、等長控制等技術(shù)要求;支持并行設(shè)計、縮短研發(fā)時間;支持模塊重用、重視 技術(shù)沉淀,保證了設(shè)計質(zhì)量,提高設(shè)計效率。

擁有一個高性能的EDA工具軟件,配合經(jīng)驗豐富的PCB設(shè)計工程師,高性能的PCB設(shè)計實現(xiàn)也就有了切實的保證。作為擁有150余名工程師的PCB設(shè)計公司,EDADOC致力于高速、高密、高性能的PCB設(shè)計。已逐漸成為推動國內(nèi)高性能PCB設(shè)計的一支生力軍。

電子發(fā)燒友App

電子發(fā)燒友App

評論