CPLD在汽車制動性能檢測系統(tǒng)中的應(yīng)用汽車制動性是汽車主動安全的主要性能之一,是汽車行駛安全的重要保障。因此,汽車的制動性能的檢測研究為其制動性能試驗研究和生產(chǎn)檢測提供了條件,為提高制動性能提供了

2009-04-16 13:56:57

可重構(gòu)體系結(jié)構(gòu)分為哪幾種?典型動態(tài)可重構(gòu)系統(tǒng)結(jié)構(gòu)有哪幾種?動態(tài)可重構(gòu)系統(tǒng)有哪些應(yīng)用實例?

2021-04-28 06:13:00

可重構(gòu)體系的結(jié)構(gòu)是由哪些部分組成的?可重構(gòu)制造系統(tǒng)有哪些應(yīng)用?

2021-09-30 06:18:17

在天線的方向圖可重構(gòu)方面,目前的研究主要集中在采用八木形式的結(jié)構(gòu)上。即通過開關(guān)控制來改變反射器或引向器的有效諧振長度,從而實現(xiàn)反射或者引向作用,使天線的輻射方向發(fā)生變化。但是,這種方式需要多個天線

2019-07-31 08:01:51

可重構(gòu)計算技術(shù)在汽車電子領(lǐng)域的應(yīng)用前景可重構(gòu)計算技術(shù)在汽車電子領(lǐng)域面臨的問題

2021-05-12 06:40:18

可重構(gòu)計算技術(shù)概述隨著20世紀80年代中期Xilinx公司推出其第一款現(xiàn)場可編程門陣列(FPGA)以來,另一種實現(xiàn)手段——可重構(gòu)計算技術(shù)逐漸受到人們的重視,因為它能夠提供硬件功能的效率和軟件的可編程性,隨著可編程器件容量根據(jù)摩爾定律的不斷增大和自動設(shè)計技術(shù)的發(fā)展,可重構(gòu)技術(shù)正迅速地成熟起來。

2019-07-29 06:26:03

可重構(gòu)設(shè)計是指利用可重用的軟、硬件資源,根據(jù)不同的應(yīng)用需求,靈活地改變自身體系結(jié)構(gòu)的設(shè)計方法。FPGA器件可多次重復(fù)配置邏輯的特性使可重構(gòu)系統(tǒng)成為可能,使系統(tǒng)兼具靈活、便捷、硬件資源可復(fù)用等性能

2011-05-27 10:22:36

。而FPGA的編程信息需存放在外部存儲器上,使用方法復(fù)雜。⑥CPLD的速度比FPGA快,并且具有較大的時間可預(yù)測性。這是由于FPGA是門級編程,并且CLB之間采用分布式互聯(lián),而CPLD是邏輯塊級編程

2012-10-26 08:10:36

/O單元互連結(jié)構(gòu),可由用戶根據(jù)需要生成特定的電路結(jié)構(gòu),完成一定的功能.由于 CPLD內(nèi)部采用固定長度的金屬線進行各邏輯塊的互連,所以設(shè)計的邏輯電路具有時間可預(yù)測性,避免了分段式互連結(jié)構(gòu)時序不完全預(yù)測

2020-08-28 15:41:47

需要特定的基于SRAM或FLASH結(jié)構(gòu)的新型FPGA的支持。隨著其產(chǎn)品和技術(shù)的相對成熟,動態(tài)重構(gòu)FPGA的設(shè)計理論和設(shè)計方法已經(jīng)逐漸成為新的研究熱點。 根據(jù)實現(xiàn)重構(gòu)的面積不同,可重構(gòu)FPGA又可以分為

2011-05-27 10:22:59

本帖最后由 mr.pengyongche 于 2013-4-30 03:24 編輯

通用微處理器具有良好的接口功能,便于構(gòu)建可重構(gòu)系統(tǒng)。按照MPU與FPGA之間的相互關(guān)系以及在系統(tǒng)中所起的作用,主要可以分為兩類:MPU控制FPGA工作的可重構(gòu)系統(tǒng)和MPU協(xié)同F(xiàn)PGA工作的可重構(gòu)系統(tǒng)

2011-05-27 10:29:16

在列車行車特別是高速行車過程中,蛇行運動造成的振動加速度值如果太大,列車有脫軌的危險。目前,動車組上的失穩(wěn)檢測系統(tǒng)配裝有加速度傳感器,可檢測振動加速度,當(dāng)振動加速度值達到預(yù)警值時,系統(tǒng)會調(diào)整行車策略

2023-09-18 07:09:30

電子系統(tǒng)功能實現(xiàn)的模式不外硬件和軟件兩種。基于馮.諾依曼或者哈佛體系結(jié)構(gòu)的通用微處理器(MPU、MCU、DSP等)系統(tǒng)是軟件實現(xiàn)模式,其硬件電路結(jié)構(gòu)固定,通過串行執(zhí)行指令實現(xiàn)功能。軟件設(shè)計靈活、易

2019-10-15 07:28:55

的數(shù)字圖像處理平臺作為嵌入式機器人控制系統(tǒng)的一個子系統(tǒng)。我們采用一種ARM+CPLD+RAM結(jié)合的結(jié)構(gòu),在提供一定的控制能力的基礎(chǔ)上,保證了數(shù)據(jù)采集的快速和完整性。嵌入式數(shù)字圖像處理系統(tǒng)結(jié)構(gòu)圖如下:該結(jié)構(gòu)

2019-12-10 17:55:03

FPGA可重構(gòu)設(shè)計的基礎(chǔ)是什么?基于FPGA的可重構(gòu)系統(tǒng)結(jié)構(gòu)是怎樣構(gòu)成的?基于FPGA的可重構(gòu)系統(tǒng)的應(yīng)用有哪些?

2021-04-30 07:16:04

分享一款不錯的基于可重構(gòu)的可信SOPC平臺的WSN安全系統(tǒng)

2021-06-07 06:30:38

CPLD的核心可編程結(jié)構(gòu)介紹基于SRAM編程技術(shù)的PLD電路結(jié)構(gòu)設(shè)計

2021-04-08 06:51:29

逐漸呈現(xiàn)出資源浪費嚴重、實時性差的劣勢。此外,數(shù)控系統(tǒng)的開放性、模塊化和可重構(gòu)設(shè)計是目前數(shù)控技術(shù)領(lǐng)域研究的熱點,目的是為了適應(yīng)技術(shù)發(fā)展和便于用戶開發(fā)自己的功能。

2019-08-26 07:06:58

由于可重構(gòu)系統(tǒng)的研究歷史很短,目前尚未形成標(biāo)準(zhǔn)的結(jié)構(gòu)形式,在此僅根據(jù)已有的應(yīng)用做初步分析。 按重構(gòu)的粒度和方式,可重構(gòu)系統(tǒng)可以粗略地分為兩種。一種是粗粒度重構(gòu)單元的模塊級重構(gòu),即重構(gòu)時改變

2011-05-27 10:24:20

可重構(gòu)結(jié)構(gòu)是一種可以根據(jù)具體運算情況重組自身資源,實現(xiàn)硬件結(jié)構(gòu)自身優(yōu)化、自我生成的計算技術(shù)。動態(tài)可重構(gòu)技術(shù)可快速實現(xiàn)器件的邏輯重建,它的出現(xiàn)為處理大規(guī)模計算問題提供了一種兼具通用處理器靈活性

2019-07-10 07:56:06

算法是在PC機上實現(xiàn)的。隨著嵌入式微處理器技術(shù)的進步,32位ARM處理器系統(tǒng)擁有很高的運算速度和很強的信號處理能力,可以作為視覺系統(tǒng)的處理器,代替PC機來實現(xiàn)簡單的視覺處理算法。下面介紹一種基于ARM和CPLD的嵌入式視覺系統(tǒng),希望能分享嵌入式視覺開發(fā)過程中的一些經(jīng)驗。

2020-04-29 07:41:43

FPGA強大的資源和實時處理能力來快速的實現(xiàn)信號的跟蹤、鎖定和解調(diào)但是,基于硬件的實現(xiàn)方案和基于軟件的方案相比,往往存在不能迅速適應(yīng)調(diào)制樣式改變的問題。為了有效斛決這個問題,筆者通過基下FPGA部分動態(tài)町重構(gòu)技術(shù),提出了相應(yīng)的解決方案。

2019-09-05 07:08:02

可重構(gòu)技術(shù)是指利用可重用的軟硬件資源,根據(jù)不同的應(yīng)用需求,靈活地改變自身體系結(jié)構(gòu)的設(shè)計方法。常規(guī)SRAM工藝的FPGA都可以實現(xiàn)重構(gòu),那我們具體該怎么做呢?

2019-08-09 07:35:02

,智能化方向邁進。改變以往由儀器 生產(chǎn)廠家定義儀器功能、用戶只能使用的局面,使用戶可自定義儀器、根據(jù)不同測試需求對儀器進行重構(gòu),已經(jīng)成為現(xiàn)代測試技術(shù)發(fā)展的一個重要方面。由于其能夠大大減少測試設(shè)備 的維修成本、提高資源利用率,可重構(gòu)儀器技術(shù)已引起高度重視。

2019-08-15 06:57:25

怎樣去分析可重構(gòu)系統(tǒng)中軟/硬件任務(wù)間通信?什么是可重構(gòu)系統(tǒng)中消息隊列通信機制?如何對可重構(gòu)系統(tǒng)中任務(wù)間的通信機制進行模擬實驗?

2021-04-27 06:03:34

μC/OS-II的堆棧結(jié)構(gòu)如何改進μC/OS-II內(nèi)核的堆棧結(jié)構(gòu)設(shè)計?

2021-04-27 07:09:57

如何用可重構(gòu)射頻前端簡化LTE設(shè)計復(fù)雜性?

2021-05-24 07:10:08

您好,我是新手用FPGA設(shè)計可重構(gòu)硬件。我只是想了解它。誰能給我一些建議?哪些書籍文件適合我參考?網(wǎng)站或論壇也不錯。謝謝?

2020-06-11 10:05:15

一種基于NiosⅡ的可重構(gòu)DSP系統(tǒng)設(shè)計

2021-03-17 06:41:55

基于FFT算法的電力系統(tǒng)諧波檢測裝置,大多采用DSP芯片設(shè)計。DSP芯片是采用哈佛結(jié)構(gòu)設(shè)計的一種CPU,運算能力很強,速度很快;但是其順序 執(zhí)行的模式限制了其進行FFT運算的速度。

2019-11-11 07:47:00

如何降低可重構(gòu)系統(tǒng)的整體功耗?有什么方法能使可重構(gòu)系統(tǒng)的性能和功耗需求之間達到平衡?

2021-04-08 07:09:23

嵌入式系統(tǒng)軟件結(jié)構(gòu)設(shè)計

2016-09-26 13:57:25

可重構(gòu)技術(shù)具有什么優(yōu)點?怎么實現(xiàn)基于FPGA可重構(gòu)智能儀器的設(shè)計

2021-05-06 06:44:38

本文提出的通過微處理器加FPGA結(jié)合串行菊花鏈實現(xiàn)可重構(gòu)的方式,實現(xiàn)了動態(tài)可重構(gòu)FPGA結(jié)構(gòu)設(shè)計的一種應(yīng)用。

2021-05-10 06:22:19

可重構(gòu)結(jié)構(gòu)是一種可以根據(jù)具體運算情況重組自身資源,實現(xiàn)硬件結(jié)構(gòu)自身優(yōu)化、自我生成的計算技術(shù)。動態(tài)可重構(gòu)技術(shù)可快速實現(xiàn)器件的邏輯重建,它的出現(xiàn)為處理大規(guī)模計算問題提供了一種兼具通用處理器靈活性和ASIC電路高速性的解決方案。

2019-08-13 07:56:00

提出了一種可用于手持移動終真?zhèn)€可重構(gòu)天線的設(shè)計方法。該天線安裝有兩個RF-PIN開關(guān),可通過一個直流控制電路控制開關(guān)的狀態(tài),以使 線的極化方式和輻射方向圖發(fā)生變化,從而實現(xiàn)極化可重構(gòu)和方向圖可重構(gòu)。該天線結(jié)構(gòu)緊湊,易于與電路板集成在一起,在移動終端中有良好的應(yīng)用價值。

2019-09-26 07:49:45

操作系統(tǒng)結(jié)構(gòu)設(shè)計 操作系統(tǒng)有多種實現(xiàn)方法與設(shè)計思路,下面僅選取最有代表性的三種做一簡單的敘述。 1.整體式系統(tǒng)結(jié)構(gòu)設(shè)計 這是最常用的一種組織方式,它常被譽為“大雜燴”,也可說,整體式系統(tǒng)結(jié)構(gòu)

2011-09-13 10:10:56

。在當(dāng)今快速發(fā)展的市場環(huán)境條件下,產(chǎn)品是否便于現(xiàn)場升級,是否便于靈活使用無疑是產(chǎn)品能否進入市場的關(guān)鍵因素,F(xiàn)PGA的可重構(gòu)設(shè)計顯得尤為重要。目前,很多可重構(gòu)的設(shè)計方式都采用單片機、CPLD等器件直接

2019-07-31 07:15:40

什么是可重構(gòu)技術(shù)? 它有哪些優(yōu)點?可重構(gòu)智能儀器的硬件怎樣去設(shè)計?可重構(gòu)智能儀器的軟件設(shè)計怎樣去設(shè)計?

2021-04-29 06:23:17

本文基于現(xiàn)代測控系統(tǒng)的通用化結(jié)構(gòu)特征和可重構(gòu)的現(xiàn)場可編程門陣列FPGA技術(shù)的發(fā)展,提出一種可重構(gòu)測控系統(tǒng)(Reconfigurable Mo—nitoring System,RMS)的設(shè)計構(gòu)想,并給出其應(yīng)用實例。

2021-04-30 06:40:43

求大神分享一種高檔FPGA可重構(gòu)配置方法

2021-04-29 06:16:54

` 產(chǎn)品結(jié)構(gòu)設(shè)計是根據(jù)產(chǎn)品功能而進行的內(nèi)部結(jié)構(gòu)的設(shè)計,是機械設(shè)計的主要內(nèi)容之一。產(chǎn)品結(jié)構(gòu)設(shè)計內(nèi)容有零件的分件、部件的固定方式、產(chǎn)品使用和功能的實現(xiàn)方式、產(chǎn)品使用材料和表面處理工藝等。要求產(chǎn)品結(jié)構(gòu)設(shè)

2016-02-25 17:24:27

【作者】:張宇;王友仁;張砦;【來源】:《小型微型計算機系統(tǒng)》2010年03期【摘要】:目前可重構(gòu)硬件的容錯機制大多采用重新布局布線的方法,但是需要很長的重布線時間,難以滿足工程應(yīng)用的需要.為此

2010-04-24 09:01:53

蝶式五軌滑蓋結(jié)構(gòu)設(shè)計與磁動力滑蓋結(jié)構(gòu)設(shè)計的不同之處在哪?

2021-07-28 06:57:34

。 直到最近,軟件無線電仍然只是大多數(shù)通信系統(tǒng)設(shè)計人員的規(guī)劃藍圖而已,但這一局面正迅速得到改觀。隨著3G無線業(yè)務(wù)的日趨臨近,設(shè)計人員又對在基礎(chǔ)架構(gòu)設(shè)計中實現(xiàn)軟件無線電結(jié)構(gòu)產(chǎn)生了濃厚的興趣。

2019-07-26 06:09:25

高速數(shù)據(jù)采集系統(tǒng)的硬件結(jié)構(gòu)MAX7000系列CPLD及其開發(fā)平臺介紹CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

2021-04-08 06:11:56

以ARM7為核心的PDA實驗結(jié)構(gòu)設(shè)計:摘要: 以A R M為核心的嵌入式系統(tǒng), 結(jié)合了嵌入式系統(tǒng)和A R M的全部技術(shù)優(yōu)勢,得到了非常廣泛地應(yīng)用。為滿足教學(xué)需要,本文提出了以

2009-05-07 10:38:20 27

27 以ARM為核心的嵌入式系統(tǒng),結(jié)合了嵌入式系統(tǒng)和ARM的全部技術(shù)優(yōu)勢,得到了非常廣泛地應(yīng)用。為滿足教學(xué)需要,本文提出了以ARM7為核心的PDA實驗結(jié)構(gòu)設(shè)計,并給出了詳細的設(shè)計思路

2009-05-09 11:00:55 21

21 針對柔性化制造的要求,構(gòu)建了以DSP+CPLD為基礎(chǔ)的數(shù)控系統(tǒng)平臺。該平臺集成度高、穩(wěn)定性強,能實現(xiàn)生產(chǎn)過程的高速度、高精度要求,實現(xiàn)了基于CPLD的可重構(gòu)設(shè)計,提高了系

2009-06-18 09:58:25 23

23 基于CPLD 和DSP 設(shè)計了線陣CCD 檢測系統(tǒng),CCD 的時序驅(qū)動由CPLD 實現(xiàn),經(jīng)過運放后的視頻信號由TMS320F2812 進行采集和處理,此檢測系統(tǒng)已成功應(yīng)用于醫(yī)藥包裝行業(yè)的數(shù)粒機系統(tǒng),能夠可

2009-08-13 14:53:46 22

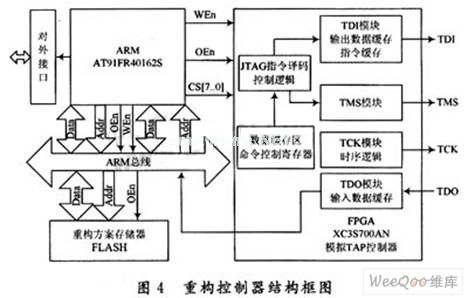

22 文章提出了一種基于ARM+CPLD 結(jié)構(gòu)的可重構(gòu)檢測系統(tǒng)的設(shè)計方法, 并采用此方法開發(fā)了一款多用途聲波檢測設(shè)備。該系統(tǒng)充分利用了ARM 芯片資源豐富、運行速度快、計算精度高、編

2009-09-15 15:40:46 8

8 本文介紹了一個由CPLD/FPGA、PAD、SoC 等組成的“通用”的嵌入式測控平臺。在闡述了嵌入式測控平臺中實現(xiàn)遠程重構(gòu)的意義、結(jié)構(gòu)和關(guān)鍵技術(shù)的基礎(chǔ)上,設(shè)計并實現(xiàn)了基于ARM 的遠

2009-09-22 11:15:09 16

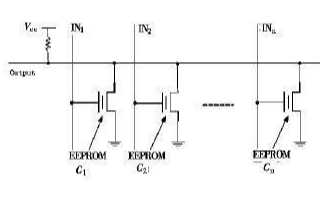

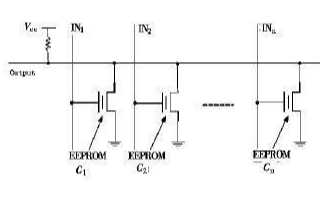

16 CPLD 相對于FPGA 更適合實現(xiàn)時序邏輯較少而組合邏輯相對復(fù)雜的功能,比如復(fù)雜的狀態(tài)機和譯碼電路等。CPLD 的EEPROM 編程技術(shù)不適合動態(tài)可重構(gòu)的應(yīng)用。本文針對 CPLD 的核心可編程結(jié)

2009-11-30 14:44:32 4

4 引擎機械振動檢測是計算機智能測控領(lǐng)域的研究熱點。論文介紹機械周期性振動測量的基本理論,對比討論不同檢測方法的效果和性能;設(shè)計基于ARM S3C44b0 振動檢測系統(tǒng)的體系結(jié)構(gòu)

2009-12-28 12:09:34 14

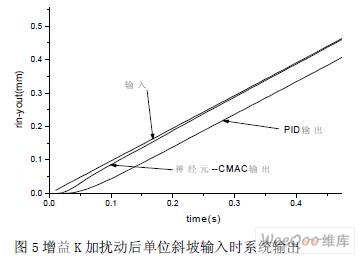

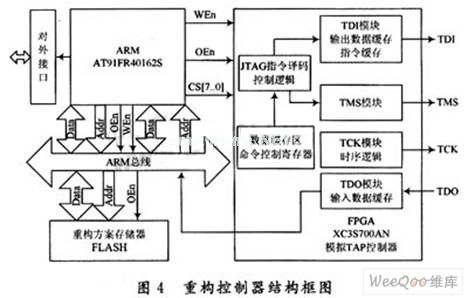

14 基于ARM+FPGA的可重構(gòu)控制器設(shè)計及其在加載系統(tǒng)中的應(yīng)用:文章提出了一種基于ARM+FPGA結(jié)構(gòu)的可重構(gòu)控制囂的設(shè)計方法.并采用此方法開發(fā)了用于加載系統(tǒng)的2通道電液伺服控制器

2010-03-02 12:03:21 29

29 針對柔性化制造的要求,構(gòu)建了以DSP+CPLD為基礎(chǔ)的數(shù)控系統(tǒng)平臺。該平臺集成度高、穩(wěn)定性強,能實現(xiàn)生產(chǎn)過程的高速度、高精度要求,實現(xiàn)了基于CPLD的可重構(gòu)設(shè)計,提高了系統(tǒng)的

2010-07-13 15:44:02 13

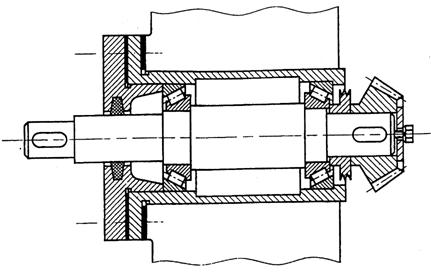

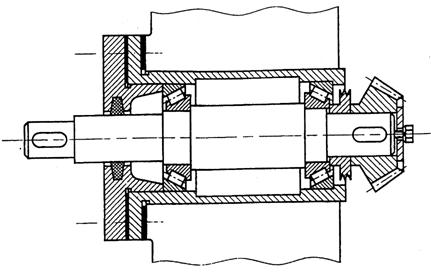

13 實驗六 軸系結(jié)構(gòu)設(shè)計實驗一、實驗?zāi)康模?熟悉并掌握軸系結(jié)構(gòu)設(shè)計中有關(guān)軸的結(jié)構(gòu)設(shè)計、滾動軸承組合設(shè)計的基本方法。

二、實

2009-03-13 19:04:06 56282

56282

采用圖像傳感器的CPLD視覺系統(tǒng)設(shè)計方法

搭建一種低成本的嵌入式視覺系統(tǒng),系統(tǒng)由CMOS圖像傳感器、CPLD、ARM7微處理器以及SRAM構(gòu)成。其中,CPLD識別

2009-03-29 15:07:51 400

400

動態(tài)可重構(gòu)系統(tǒng)的通信結(jié)構(gòu)分析

動態(tài)可重構(gòu)技術(shù)能在一定控制邏輯的驅(qū)動下,對全部或部分邏輯資源實現(xiàn)在系統(tǒng)的動態(tài)功能變換和硬

2009-03-29 15:12:52 910

910

CPLD在雙軸位置檢測系統(tǒng)中的應(yīng)用

1 引言數(shù)控機床的加T精度主要南位置檢測系統(tǒng)的精度決定,

2009-10-30 08:32:33 431

431

基于對EPCS在線編程的FPGA可重構(gòu)方法

0 引言 可重構(gòu)體系結(jié)構(gòu)已經(jīng)成為FPGA系統(tǒng)開發(fā)的研究熱點,并已有許多令人矚目的研究成果及產(chǎn)品應(yīng)用。FPGA可重構(gòu)

2009-12-08 17:22:17 1310

1310 可重構(gòu)設(shè)計的測控站監(jiān)控系統(tǒng)研究與實現(xiàn)

隨著科學(xué)技術(shù)的進步,人類對空間探索的步伐越來越大。空間任務(wù)的需求,推動地面測控系統(tǒng)的更新和發(fā)展,主要體現(xiàn)在:測

2010-01-11 23:47:06 702

702

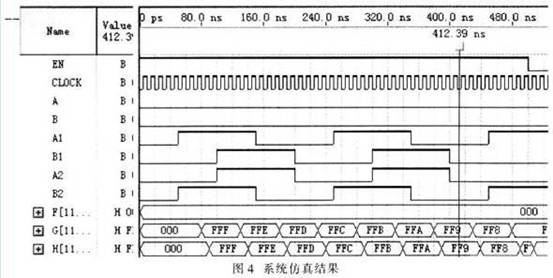

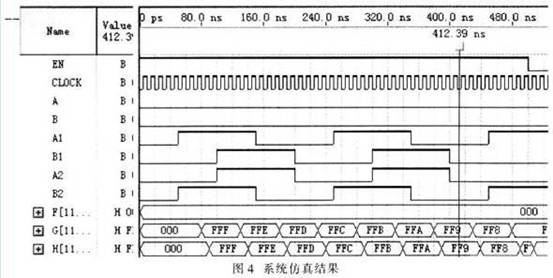

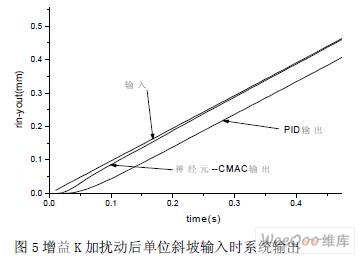

基于DSP和CPLD 可重構(gòu)數(shù)控系統(tǒng)的設(shè)計與仿真

1、前言

隨著計算機技術(shù)的高速發(fā)展,各工業(yè)發(fā)達國家投入巨資,對現(xiàn)代

2010-02-09 10:52:11 576

576

基于ARM+FPGA的重構(gòu)控制器設(shè)計

可重構(gòu)技術(shù)是指利用可重用的軟硬件資源,根據(jù)不同的應(yīng)用需求,靈活地改變自身體系結(jié)構(gòu)的設(shè)計方法。常規(guī)SRAM工藝的FPGA都可以實現(xiàn)

2010-03-02 10:58:41 719

719

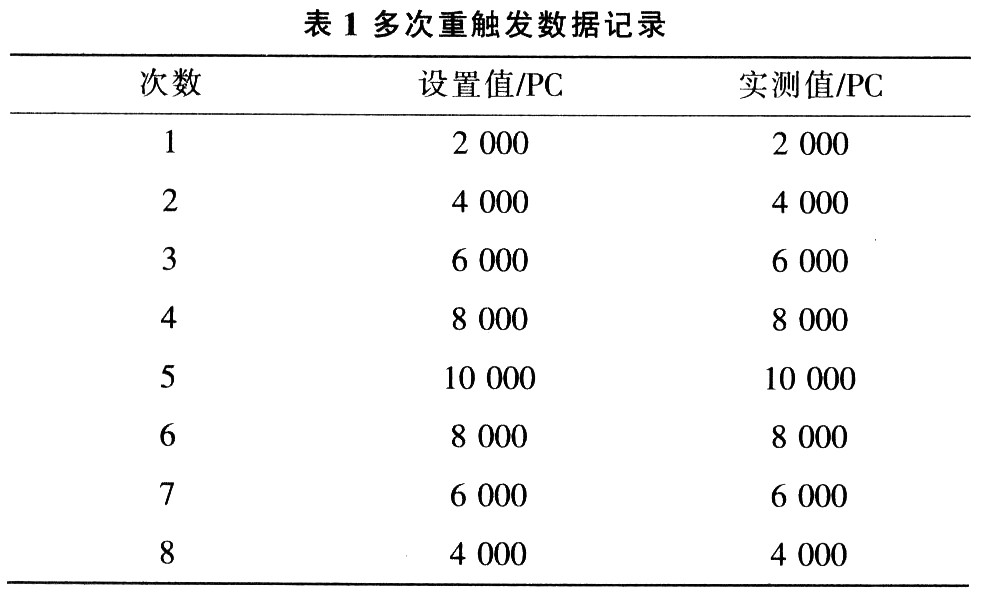

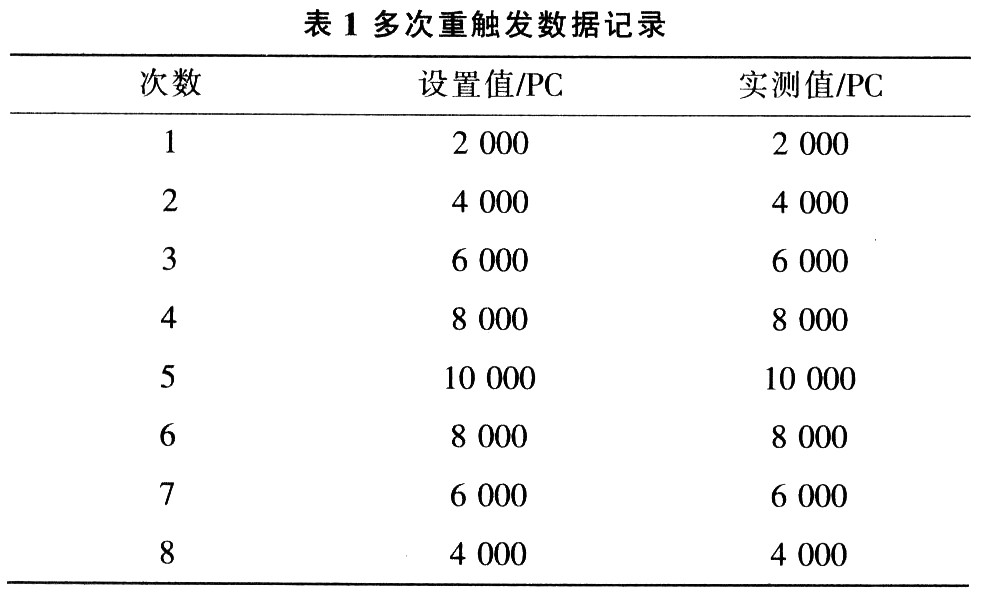

采用CPLD的多次重觸發(fā)存儲測試系統(tǒng)解決方案

概述:提出一種基于CPLD的多次重觸發(fā)存儲測試系統(tǒng)設(shè)計方案,詳細介紹系統(tǒng)硬件設(shè)計以及CPLD內(nèi)部控制

2010-03-17 11:37:51 531

531

提出了一種基于ARM7 和CPLD 架構(gòu)的數(shù)字公交站亭系統(tǒng)。系統(tǒng)通過GPRS 模塊與公交控制中心實時通信,使用CA 認證保證通信的安全性,采用兩塊SRAM 組成具有“乒乓邏輯”的高速緩存確保顯示

2011-09-21 15:26:48 1389

1389

基于ARM的嵌入式系統(tǒng)硬件結(jié)構(gòu)設(shè)計

2016-12-16 21:32:44 0

0 基于ARM和CPLD的無線內(nèi)窺系統(tǒng)設(shè)計

2017-01-24 16:15:38 19

19 驅(qū)動與檢測雙差動硅微陀螺結(jié)構(gòu)設(shè)計和分析_劉悅琛

2017-01-31 15:22:44 1

1 基于ARM和DSP的可重構(gòu)數(shù)控系統(tǒng)

2017-09-25 08:16:59 8

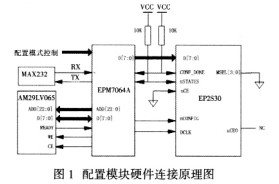

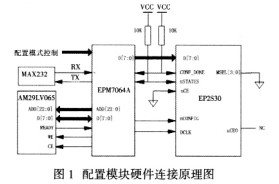

8 隨著FPGA的廣泛應(yīng)用, 其實現(xiàn)的功能也越來越多, FPGA 的動態(tài)重構(gòu)設(shè)計就顯得愈發(fā)重要。在分析Xilinx Vertex II Pro系列FPGA配置流程、時序要求的基礎(chǔ)上, 設(shè)計了基于CPLD

2017-11-22 07:55:01 937

937

FPGA的不同配置電路功能,在不同時段執(zhí)行不同的算法,實現(xiàn)了虛擬硬件可重構(gòu)計算技術(shù)。這里提出的通過微處理器加FPGA結(jié)合串行菊花鏈實現(xiàn)可重構(gòu)的方式,實現(xiàn)了動態(tài)可重構(gòu)FPGA結(jié)構(gòu)設(shè)計的一種應(yīng)用。

2017-11-25 10:20:01 12296

12296

針對傳統(tǒng)的面向應(yīng)用領(lǐng)域的多核SoC體系結(jié)構(gòu)設(shè)計方法存在系統(tǒng)結(jié)構(gòu)探索空間大、設(shè)計復(fù)雜度高等問題,提出了一種基于體系結(jié)構(gòu)模板的粗粒度可重構(gòu)SoC系統(tǒng)架構(gòu)設(shè)計方法。該設(shè)計方法以體系結(jié)構(gòu)設(shè)計為中心,體系結(jié)構(gòu)

2017-11-29 10:12:14 0

0 現(xiàn)代高速度FPGA運行時需將其配置數(shù)據(jù)加載到內(nèi)部SDRAM中,改變SDRAM里面的數(shù)據(jù),可使FPGA實現(xiàn)不同的功能,即所謂的可重構(gòu)技術(shù)。可重構(gòu)技術(shù)包括靜態(tài)系統(tǒng)重構(gòu)和動態(tài)系統(tǒng)重構(gòu)。在FPGA處于工作

2019-06-10 08:17:00 2799

2799

顯然,設(shè)計基于SRAM編程技術(shù)的CPLD可以很好解決上述應(yīng)用問題。CPLD的設(shè)計和實現(xiàn)的關(guān)鍵問題是核心可編程電路結(jié)構(gòu)的實現(xiàn)。因此,本文主要探討針對CPLD的核心可編程結(jié)構(gòu),如何設(shè)計具有相似功能且基于SRAM編程技術(shù)的電路結(jié)構(gòu),從而更好滿足動態(tài)重構(gòu)系統(tǒng)中實現(xiàn)復(fù)雜狀態(tài)機和譯碼電路的應(yīng)用。

2020-04-25 10:21:00 1686

1686

DSP中MAC的微系統(tǒng)結(jié)構(gòu)設(shè)計(高頻開關(guān)電源技術(shù)指標(biāo))-該文檔為DSP中MAC的微系統(tǒng)結(jié)構(gòu)設(shè)計總結(jié)文檔,是一份不錯的參考資料,感興趣的可以下載看看,

2021-09-22 13:24:39 3

3 在一個SoC的系統(tǒng)結(jié)構(gòu)設(shè)計中,除了硬件結(jié)構(gòu)以外,軟件結(jié)構(gòu)的設(shè)計對整個SoC的性能有很大的影響。

2023-09-25 15:14:31 548

548

電子發(fā)燒友App

電子發(fā)燒友App

評論