在科技高速發(fā)展的當(dāng)今世界,隨著電子技術(shù)和集成電路技術(shù)的不斷進(jìn)步,半導(dǎo)體工藝的迅猛發(fā)展以及人們對信息高速化、寬帶化的需求,高速電路設(shè)計(jì)已經(jīng)成為電子產(chǎn)品開發(fā)的一個(gè)必不可少的環(huán)節(jié)。

如果想設(shè)計(jì)出一款高端產(chǎn)品,就意味著需要不斷地挑戰(zhàn)電子設(shè)計(jì)的各種極限。不論你是PCB工程師、系統(tǒng)工程師,還是芯片設(shè)計(jì)工程師,都面臨著信號完整性——當(dāng)今高速電子設(shè)計(jì)的一大挑戰(zhàn)。如何高效地設(shè)計(jì)高速接口電路如DDR4、PCI Express、40G比特以太網(wǎng)接口或者SerDes接口?如何在設(shè)計(jì)過程中得到可預(yù)見的誤碼率和減少電磁干擾和串?dāng)_?如何處理由高速信號互連線引起的反射、串?dāng)_、開關(guān)噪聲等信號完整性問題,確保信號傳輸?shù)馁|(zhì)量?這些都不是簡單的工作。

高速設(shè)計(jì)有何特別?

? ? ? ?所謂能力越大,責(zé)任越大。高速設(shè)計(jì)在電子設(shè)計(jì)領(lǐng)域也帶來了自己獨(dú)特的挑戰(zhàn)。多年來,高頻信號設(shè)計(jì)部分的增加與電子系統(tǒng)性能的不斷提高緊密相連。隨著系統(tǒng)性能的提高,PCB設(shè)計(jì)師的挑戰(zhàn)開始加劇。芯片越來越小,電路板布局越來越密集,我們也在不斷尋求提供最低功耗的芯片。隨著所有這些技術(shù)的快速發(fā)展,高速設(shè)計(jì)作為優(yōu)秀高性能產(chǎn)品設(shè)計(jì)的核心,包括其所有的復(fù)雜性和解決方案便應(yīng)運(yùn)而生。

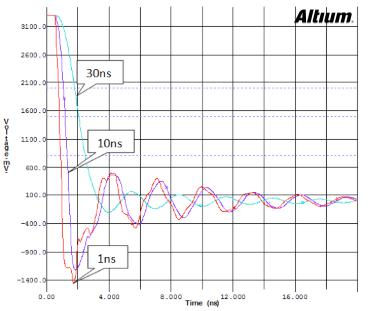

過去30年來PCB設(shè)計(jì)發(fā)生了很大的變化。 1987年,我們認(rèn)為0.5微米技術(shù)是全能的,但是今天我們發(fā)現(xiàn)22nm技術(shù)是常見的。 1985年推出的在當(dāng)時(shí)代表主流設(shè)計(jì)復(fù)雜度的邊緣速率(通常為30ns)與今天的邊緣速率(1ns)相比簡直是小巫見大巫,如下圖所示:

? ? ? ??當(dāng)涉及到高速電路設(shè)計(jì)的時(shí)候,電路的布局布線工作將不再是簡單地快速連線或者為滿足產(chǎn)品的外形尺寸去簡單的布局。工程師需要事先規(guī)劃每個(gè)處理器、內(nèi)存模塊和連接器的位置,并仔細(xì)確定它們之間的高速互連設(shè)計(jì)。完善的高速設(shè)計(jì)意味著在設(shè)計(jì)之初就制定好電路的約束和規(guī)范。確保電路板上的所有信號完美地進(jìn)行傳輸,并最大限度地降低信號相互之間的干擾。那么這里就要提到一個(gè)專業(yè)名詞信號完整性(SI)。SI就是確保瞬時(shí)跳變的數(shù)字信號通過較長的一段傳輸線后,在接收端仍能完整地被正確接收,并保證良好的電磁兼容性。SI主要涉及到延遲、反射、串?dāng)_、時(shí)序、端接策略、電流回路等問題。

信號完整性問題產(chǎn)生的根源:

數(shù)字信號開關(guān)速度不斷提高,上升沿變快,造成的信號反射、過沖、振鈴和串?dāng)_

信號的幅度不斷降低,信號/噪聲比越來越小

信號速度的提高

信號在傳輸線上的傳輸延遲

信號完整性主要問題表現(xiàn):

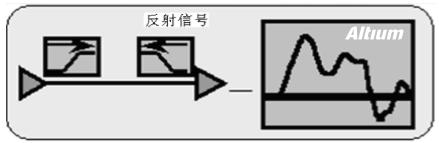

信號反射:

如果一根走線沒有被正確終結(jié)(終端匹配),那么來自于驅(qū)動(dòng)端的信號脈沖在接收端被反射,從而引發(fā)不預(yù)期效應(yīng),使信號輪廓失真。

信號反射產(chǎn)生原因:

過長的走線

未被匹配終結(jié)的傳輸線

過量電容或電感,以及阻抗失配

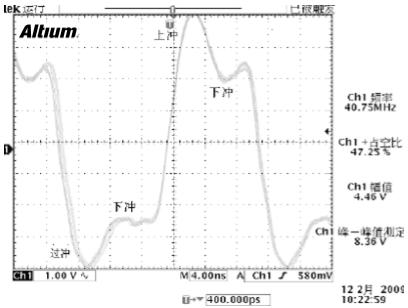

? ? ?2. 過沖與下沖

??????雖然大多數(shù)元件接收端都有輸入保護(hù)二極管保護(hù), 但有時(shí)這些過沖電平會遠(yuǎn)遠(yuǎn)超過元件電源電壓范圍,損壞元器件。

? ? ? 過沖與下沖產(chǎn)生的原因:

過長的走線

信號變化太快

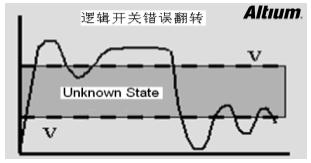

? ? ? 3. 振鈴(Ringing)

??????信號的振蕩發(fā)生在邏輯電平門限附近,多次跨越邏輯電平門限從而導(dǎo)致邏輯功能紊亂。信號如果在傳輸線上來回反射,就會產(chǎn)生振鈴。

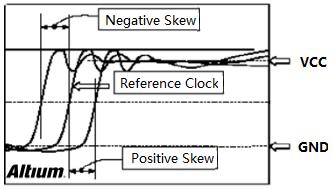

? ? ? 4. 時(shí)鐘偏移(Clock Skew)

時(shí)鐘偏移(Skew)是指不同的接收設(shè)備接收到同一時(shí)鐘驅(qū)動(dòng)輸出之間的時(shí)間差。對于參考時(shí)鐘而言,時(shí)鐘偏移有正延時(shí)和 負(fù)延時(shí)之分。時(shí)鐘偏移可引起有效時(shí)鐘周期的減小。

產(chǎn)生的原因:

由不同時(shí)鐘路徑的延時(shí)或驅(qū)動(dòng)器件不同驅(qū)動(dòng)門之間的時(shí)差所造成

由于接收端之間的閾值不同、負(fù)載電容不同、信號質(zhì)量的差異所造成

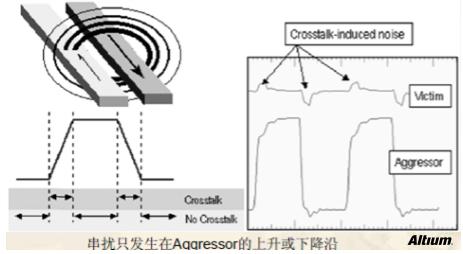

? ? ? 5. 串?dāng)_

??????串?dāng)_是指兩個(gè)不同的電性能網(wǎng)絡(luò)之間的相互作用。產(chǎn)生串?dāng)_(crosstalk) 的一方被稱作Aggressor,而收到干擾的一方被稱作Victim。通常,一個(gè)網(wǎng)絡(luò)既是入侵者,又是受害者。串?dāng)_會導(dǎo)致誤觸發(fā)。

串?dāng)_是由同一個(gè)PCB板上的兩條信號線之間互容和互感的容性耦合和感性耦合引起線上的噪聲。容性耦合引發(fā)耦合電流,而感性耦合引發(fā)耦合電壓。

影響串?dāng)_的因素:PCB板層的參數(shù)(厚度,介電常數(shù))等、信號線間距、線端接方式等。

易產(chǎn)生串?dāng)_的信號:異步信號和時(shí)鐘信號

? ? ? 串?dāng)_的解決方法?

信號線距離地線越近,線間距越大,產(chǎn)生的串?dāng)_信號就越小。因此解決串?dāng)_的方法是移開發(fā)生串?dāng)_的信號或屏蔽被嚴(yán)重干擾 的信號(包地)。

6. 電磁輻射

EMI所產(chǎn)生的問題包括過量的電磁輻射及對電磁輻射的敏感性兩個(gè)方面。當(dāng)數(shù)字系統(tǒng)加電運(yùn)行時(shí),會向周圍環(huán)境輻射電磁波, 從而干擾周圍環(huán)境中電子設(shè)備的正常工作。

電磁輻射產(chǎn)生的主要原因:

電路頻率太高

布局布線不合理,包括特性阻抗控制、線寬控制

高速設(shè)計(jì)的解決方案

??????針對上述高速設(shè)計(jì)中有關(guān)信號完整性方面常見的問題,在進(jìn)行具體的設(shè)計(jì)過程中都有哪些解決方案?

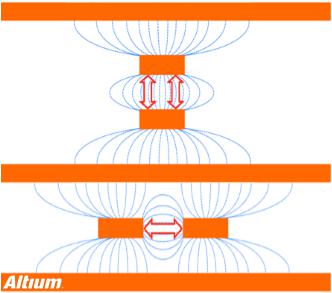

PCB分層設(shè)計(jì)

???????PCB的疊層結(jié)構(gòu)設(shè)計(jì)是進(jìn)行信號完整性的分析的基礎(chǔ), 建議采用多層設(shè)計(jì),設(shè)計(jì)的一般原則如下:

元件面的下層為地平面,以提供器件屏蔽層和為頂層布線提供參考平面

所有信號層盡可能與地平面相鄰

盡量避免兩信號層直接相鄰

主電源盡量與對應(yīng)地相鄰

兼顧層壓結(jié)構(gòu)對稱

關(guān)鍵信號與地平面相鄰,不跨分割區(qū)

??????如上圖所示,對于多層板,關(guān)鍵布線層(時(shí)鐘線、總線、接口信號線、射頻線、復(fù)位信號線、片選信號線以及各種控制信號 線等所在層)應(yīng)與完整地平面相鄰,優(yōu)選兩地平面之間。因?yàn)椋P(guān)鍵信號線一般都是強(qiáng)輻射或極其敏感的信號線,靠近地平面布線能夠使其信號回路面積減小,減小其輻射 強(qiáng)度或提高抗干擾能力。

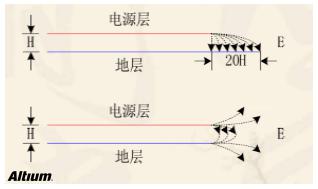

另外,多層板中,電源平面應(yīng)相對于其相鄰地平面內(nèi)縮(建議值5H~20H)。 如下圖所示,電源平面相對于其回流地平面內(nèi)縮可以有效抑制“邊緣輻射”問題。

PCB布局設(shè)計(jì)

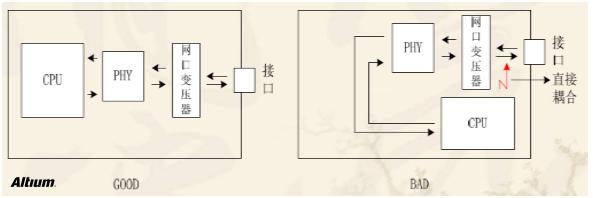

PCB布局設(shè)計(jì)時(shí),應(yīng)充分遵守沿信號流向直線放置的設(shè)計(jì)原則,盡量避免來回環(huán)繞。避免信號直接耦合,影響信號質(zhì)量。

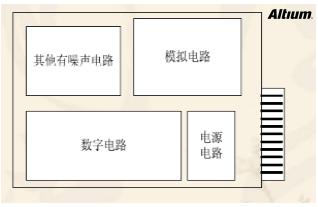

??????多種模塊電路在同一PCB上放置時(shí),數(shù)字電路與模擬電路、高速與低速電路應(yīng)分開布局。避免數(shù)字電路、模擬電路、高速電路以及低速電路之間的互相干擾。

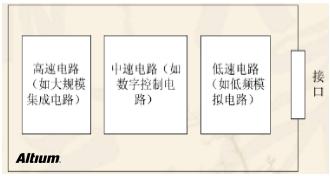

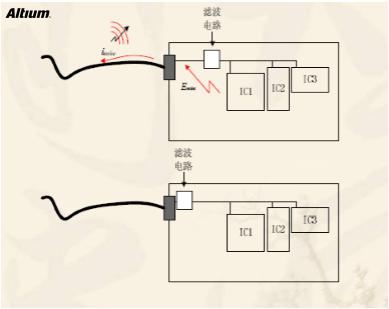

??????當(dāng)線路板上同時(shí)存在高、中、低速電路時(shí),應(yīng)該遵從下圖中的布局原則。避免高頻電路噪聲通過接口向外輻射。

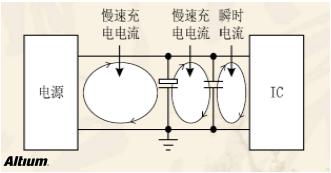

??????存在較大電流變化的單元電路或器件(如電源模塊的輸入輸出端、風(fēng)扇及繼電器)附近應(yīng)放 置儲能和高頻濾波電容。儲能電容的存在可以減小大電流回路的回路面積。

??????線路板電源輸入口的濾波電路應(yīng)應(yīng)靠近接口放置。避免已經(jīng)經(jīng)過了濾波的線路被再次耦合。

??????在PCB板上,接口電路的濾波、防護(hù)以及隔離器件應(yīng)該靠近接口放置。可以有效的實(shí)現(xiàn)防護(hù)、濾波和隔離的效果。

PCB布線設(shè)計(jì)

普通走線要注意的地方

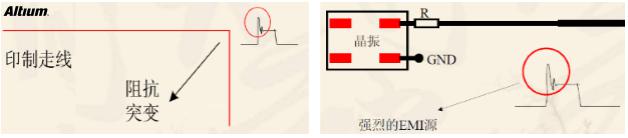

PCB走線需要避免直角走線。直角走線導(dǎo)致阻抗不連續(xù),導(dǎo)致信號發(fā)射,從而產(chǎn)生振鈴或過沖,形成強(qiáng)烈的EMI輻射。

PCB走線特別是時(shí)鐘線與總線的粗細(xì)應(yīng)保持一致。粗細(xì)不一致時(shí),走線阻抗會發(fā)生突變, 導(dǎo)致如同前頁中的問題。

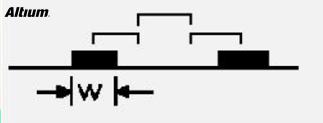

3W原則

??????為了減少線間串?dāng)_,應(yīng)保證線間距足夠大,當(dāng)線中心間距不少于3倍線寬時(shí),則可保持70%的電場不互相干擾,稱為3W規(guī) 則。如要達(dá)到98%的電場不互相干擾,可使用10W的間距。時(shí)鐘、總線、射頻線等關(guān)鍵信號走線和其他同層平行走線應(yīng)盡量滿足3W原則。避免信號之間的串?dāng)_。

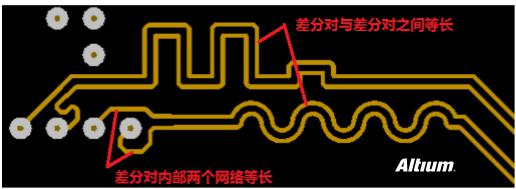

差分對布線(Differential Pairs)

??????差分信號就是利用兩根線分別傳輸正信號和負(fù)信號,接收端根據(jù)兩根線的差值就能判定接收到的比特,差分信號能夠極大緩解遠(yuǎn)距高速通信的共模信號偏移問題。成對的布線,信號相反,由于干擾對兩根走線影響相同,增強(qiáng)了抗干擾能力。良好的差分對應(yīng)當(dāng)距離足夠近,并且具有一定的絞合度以抵消空間電(磁)場的影響。所以在布線中盡量保持等長,等寬且緊密靠近。所謂盡量靠近且平行是因?yàn)殚g距會影響到差分阻抗(differential impedance)的值, 此值是設(shè)計(jì)差分對的重要參數(shù)。若兩線忽遠(yuǎn)忽近, 差分阻抗就會不一致, 就會影響信號完整性(signal integrity)及時(shí)間延遲(timing delay)。

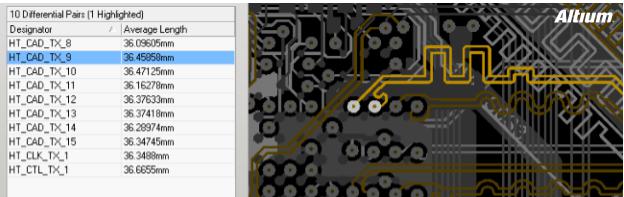

??????在Alitum Designer中,可以在原理圖設(shè)計(jì)階段就定義差分對信號。如下圖所示。

?????當(dāng)原理圖導(dǎo)入到PCB時(shí),其設(shè)計(jì)規(guī)則設(shè)置同樣一起導(dǎo)入到PCB design rule里。然后在PCB中進(jìn)行差分對布線。如下圖。

From-Tos 布線

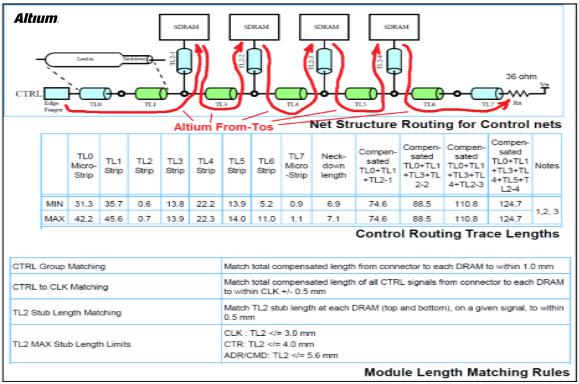

??????From-To主要是用來定義多節(jié)點(diǎn)網(wǎng)絡(luò)上的pin-to-pin管腳之間的布線長度。通過這種方式,我們可以控制一個(gè)網(wǎng)絡(luò)上某個(gè)特定管腳到另一個(gè)特定管腳之間的走線長度,以及對應(yīng)的信號傳輸延遲。這項(xiàng)設(shè)置主要在PCB設(shè)計(jì)中進(jìn)行。

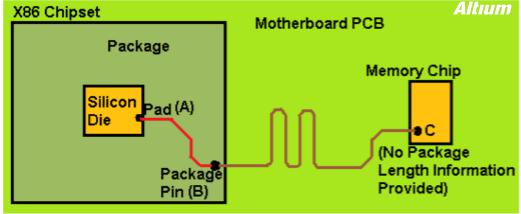

對于多節(jié)點(diǎn)網(wǎng)絡(luò),我們需要對每個(gè)重要的驅(qū)動(dòng)端-接收端的管腳對創(chuàng)建這些From-To對象。對于多節(jié)點(diǎn)網(wǎng)絡(luò)中這些驅(qū)動(dòng)端到接收端的多組From-To對象來說,最主要的目的是要控制對節(jié)點(diǎn)網(wǎng)絡(luò)中每組信號(從驅(qū)動(dòng)端某管腳到接收端另一管腳)的飛行時(shí)間。該飛行時(shí)間是指信號從驅(qū)動(dòng)端傳輸?shù)浇邮斩耍⑦_(dá)到一定的電平之間的延時(shí)。和傳輸延遲和上升時(shí)間有關(guān)。這種情況下,需要在每組驅(qū)動(dòng)端到接收端進(jìn)行網(wǎng)絡(luò)分段控制(靜態(tài)時(shí)序)。From-To用來進(jìn)行多節(jié)點(diǎn)分段控制的方法在高速設(shè)計(jì)中,對保持信號完整性非常重要。如下圖所示為From-To用于多節(jié)點(diǎn)網(wǎng)絡(luò)中各組信號傳輸?shù)臅r(shí)序考慮的例子。參考http://publish-it-online.com/publication/?i=49146 第26頁。

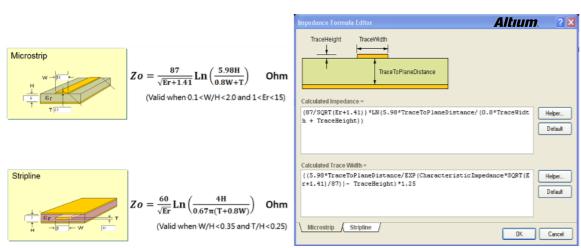

阻抗布線(Impedance control)

? ? ???阻抗控制在高速PCB設(shè)計(jì)中是非常重要的。俗話說的好,工欲善其事,必先利其器。要想板子利索的跑起來,傳輸線阻抗計(jì)算肯定不能等閑視之。

在高速設(shè)計(jì)流程里,疊層設(shè)計(jì)和阻抗計(jì)算是必須要認(rèn)真考慮的。基于精確的疊層結(jié)構(gòu)設(shè)計(jì),AItiumDesigner建立了標(biāo)準(zhǔn)的PCB微帶線和帶狀線模型,由此可以通過設(shè)計(jì)目標(biāo)阻抗來自動(dòng)控制所需的走線寬度,避免在換層走線時(shí)重新計(jì)算線寬,再人工改變走線寬度的繁瑣。如下圖所示。

??????阻抗計(jì)算方法很成熟,除了Altium Designer中內(nèi)置的阻抗計(jì)算功能之外,由于更多高速設(shè)計(jì)特定的要求不同,設(shè)計(jì)師還可以輔助外部的專門計(jì)算阻抗的軟件來計(jì)算,并綜合考慮。比如Polar Instruments的SI8000,SI9000,或Freeware的TNT-MMTL都可以。不同的軟件計(jì)算的差別很小。

阻抗的計(jì)算是相對比較繁瑣的,但我們可以總結(jié)一些經(jīng)驗(yàn)值幫助提高計(jì)算效率。對于常用的FR4,50ohm的微帶線,線寬一般等于介質(zhì)厚度的2倍;50ohm的帶狀線,線寬等于兩平面間介質(zhì)總厚度的二分之一,這可以幫我們快速鎖定線寬范圍。

除了提升計(jì)算效率,我們還要提高計(jì)算精度。因?yàn)樽杩箍刂聘圃彀鍙S的關(guān)系也很大。由于加工工藝不同,材料介電系數(shù)差異等情況,阻抗設(shè)計(jì)需要設(shè)計(jì)師與PCB制造板廠共同協(xié)作,根據(jù)經(jīng)驗(yàn)調(diào)整,才能對阻抗有一個(gè)理想的控制。

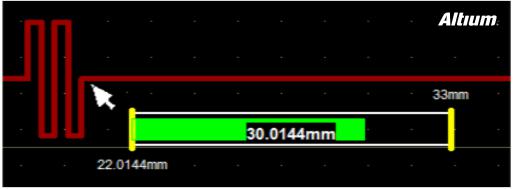

長度調(diào)整走線(Length Tuning)

??????匹配走線長度保證了時(shí)間敏感信號同時(shí)到達(dá)目標(biāo)引腳。在不違反設(shè)計(jì)規(guī)則的前提下,通過對網(wǎng)絡(luò)走線中增加蛇形線等方式,能夠動(dòng)態(tài)優(yōu)化和控制網(wǎng)絡(luò)或差分對走線長度。走線長度調(diào)整一般是為了控制時(shí)序。

比如等長線是為了減少信號相對延時(shí),常用在高速存儲器的地址和數(shù)據(jù)線上。簡單來說:等長線的作用,就是讓信號傳輸?shù)乃俣纫恢隆?a href="http://m.1cnz.cn/tags/i2c/" target="_blank">I2C總線無需畫等長線,雖然I2C信號與內(nèi)存一樣都是有相對時(shí)序要求,但由于信號頻率較低,此時(shí)由導(dǎo)線長度引起的延時(shí)不足以影響正常時(shí)序,所以無需等長。當(dāng)然如果等長也沒什么不好的。差分線也一樣,高速信號要注意等長。差分線在等長布線時(shí)要保證2根線等距平行。

走線長度調(diào)整有多種應(yīng)用。比如:

點(diǎn)對點(diǎn)網(wǎng)絡(luò)走線長度調(diào)整。如下圖所示。

??????差分對走線長度調(diào)整(差分對內(nèi)部兩個(gè)網(wǎng)絡(luò)之間走線等長,以及兩對差分對之間走線等長)。如下圖所示。

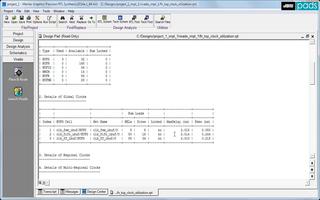

??????封裝內(nèi)管腳延遲所需要的長度調(diào)整。 比如大型BGA器件內(nèi)部到器件引腳的信號走線長度,通常沒有進(jìn)行匹配,而且各引腳的信號走線都不相同。這些芯片內(nèi)部的引腳走線數(shù)據(jù)可以從芯片的數(shù)據(jù)手冊拿到。而我們這里所講的長度匹配,就是在芯片外部進(jìn)行PCB設(shè)計(jì)走線的時(shí)候,進(jìn)行長度調(diào)整,來匹配芯片內(nèi)部到引腳的走線部分,進(jìn)行相應(yīng)的延時(shí)補(bǔ)償。如下圖所示。

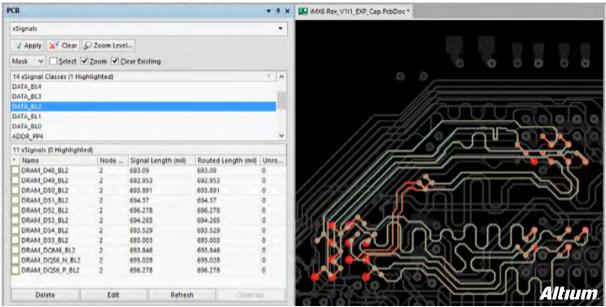

Xsignal

??????在高速布線設(shè)計(jì)時(shí),網(wǎng)絡(luò)的布線拓?fù)浣Y(jié)構(gòu)是根據(jù)這個(gè)網(wǎng)絡(luò)的腳對腳(pin-to-pin)連接方式來安排的。默認(rèn)情況下網(wǎng)絡(luò)的 pin-to-pin 連接方式是按照最小長度定義的。網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)的選擇有多種原因:

在高速設(shè)計(jì)中,我們要盡可能地減少信號的反射現(xiàn)象,所以一般選擇菊花鏈形式的網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu);

對于地網(wǎng)絡(luò),星形拓?fù)浣Y(jié)構(gòu)可以保障所有電流回到一個(gè)共同的公共點(diǎn)。

DDR2(某些情況下的DDR3),可采用平衡T(balanced-T)或支路匹配(branch matched)的拓?fù)浣Y(jié)構(gòu)。

DDR3和DDR4 中引入了飛越(fly-by)拓?fù)浣Y(jié)構(gòu)。在fly-by拓?fù)浣Y(jié)構(gòu)下,地址/控制線/時(shí)鐘信號從一個(gè)SDRAM到下一個(gè)之間依次布線,這種方式可以消除反射干擾。

所以,XSignal實(shí)際上是指設(shè)計(jì)師定義的兩個(gè)節(jié)點(diǎn)之間的信號路徑。可以是同一個(gè)網(wǎng)絡(luò)中的兩個(gè)節(jié)點(diǎn),也可以是相關(guān)的網(wǎng)絡(luò)之間(由一器件分隔開來)的兩個(gè)節(jié)點(diǎn)。一旦節(jié)點(diǎn)對被確定,即可通過相關(guān)的設(shè)計(jì)規(guī)則來設(shè)置它們的長度以及需要匹配的長度。在信號長度規(guī)則中使用 XSignal (pin pairing) ,實(shí)現(xiàn)每個(gè)支路不同的延時(shí)補(bǔ)償。

??????如上圖所示,Altium Designer可以自動(dòng)根據(jù)XSignal Wizard簡單快捷地生成XSignal,并對其進(jìn)行相應(yīng)的規(guī)則設(shè)置來進(jìn)行高速布線。

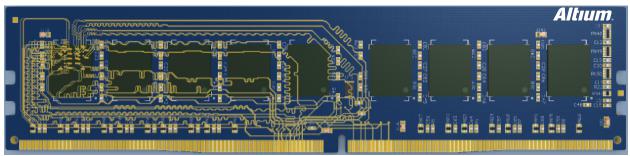

??????如上圖所示,采用XSignal對DDR4的連接方式進(jìn)行配置。在長度規(guī)則中使用 xSignals (Pin Pairs),并調(diào)整每個(gè)pin-pair 的長度達(dá)到延時(shí)要求。從金手指到第一個(gè)器件之間的總線連接長度必須相等。

電子發(fā)燒友App

電子發(fā)燒友App

評論