DDR布線在PCB設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的時(shí)序裕量。要保證系統(tǒng)的時(shí)序,線長(zhǎng)匹配又是一個(gè)重要的環(huán)節(jié)。我們來(lái)回顧一下,DDR布線,線長(zhǎng)匹配的基本原則是:地址,控制

2017-09-01 14:03:41 4392

4392

DDR布線在PCB設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的時(shí)序裕量。要保證系統(tǒng)的時(shí)序,

2017-09-26 11:39:47 6363

6363

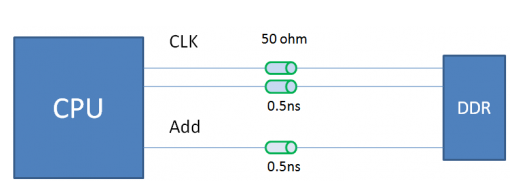

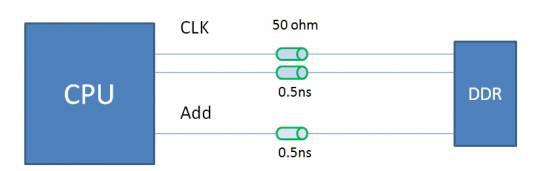

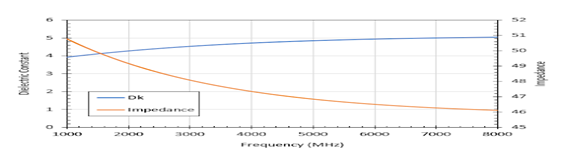

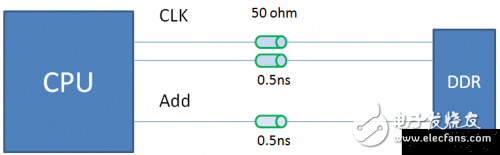

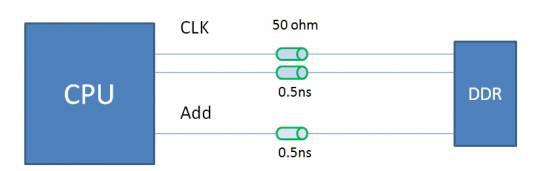

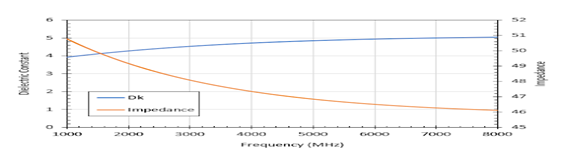

PCB設(shè)計(jì)時(shí)DDR線寬和阻抗是怎樣確定下來(lái)的呢?讓我們通一個(gè)具體的項(xiàng)目來(lái)學(xué)習(xí)一下。

2018-07-06 09:04:47 16923

16923

對(duì)PCB設(shè)計(jì)者來(lái)說(shuō),創(chuàng)建原理圖符號(hào)庫(kù)和PCB封裝庫(kù)是十分基礎(chǔ)卻又非常重要的工作。只有確保原理圖符號(hào)庫(kù)和PCB封裝庫(kù)準(zhǔn)確無(wú)誤,才能保證PCB設(shè)計(jì)工作得以順利開(kāi)展。

2022-10-27 10:37:28 706

706 上期和大家聊的電源PCB設(shè)計(jì)的重要性,那本篇內(nèi)容小編則給大家講講存儲(chǔ)器的PCB設(shè)計(jì)建議,同樣還是以大家最為熟悉的RK3588為例,詳細(xì)介紹一下DDR模塊電路的PCB設(shè)計(jì)要如何布局布線。 由于

2023-08-24 08:40:05 899

899

100M到200M的ADC在PCB設(shè)計(jì)時(shí),要進(jìn)行嚴(yán)格的阻抗匹配么?有沒(méi)有一些標(biāo)準(zhǔn)性的文檔來(lái)說(shuō)明呢

2023-12-05 06:30:10

做板載內(nèi)存的時(shí)候只需要配置好內(nèi)存SPD就可以了。控制組信號(hào)長(zhǎng)度控制要求和地址/命令組信號(hào)的要求類似,設(shè)計(jì)的時(shí)候應(yīng)該按照CPU廠家的要求來(lái)做,INTEL凌動(dòng)N450要求控制在時(shí)鐘信號(hào)0mil到正

2011-10-27 14:53:32

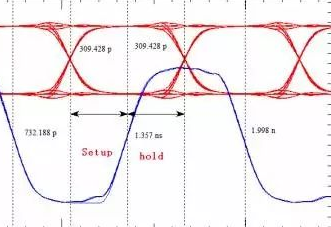

“Write leveling”技術(shù)來(lái)控制器件內(nèi)部偏移時(shí)序等有效措施。雖然在保證設(shè)計(jì)實(shí)現(xiàn)和信號(hào)的完整性起到一定作用,但要實(shí)現(xiàn)高頻率高帶寬的存儲(chǔ)系統(tǒng)還不全面,需要進(jìn)行仿真分析才能保證設(shè)計(jì)實(shí)現(xiàn)和信號(hào)質(zhì)量

2014-12-15 14:17:46

這篇帖子跟大家一起來(lái)討論下DDR3布線的那些事:DDR3的設(shè)計(jì)有著嚴(yán)格等長(zhǎng)要求,歸結(jié)起來(lái)分為兩類(以64位的DDR3為例): 數(shù)據(jù) (DQ,DQS,DQM):組內(nèi)等長(zhǎng),誤差控制在20MIL以內(nèi),組間

2016-10-28 10:25:21

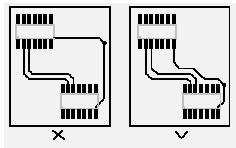

)GROUP F 中 CLK、CLKn 差分對(duì)的線長(zhǎng)誤差控制在 5mil 以內(nèi);CLK/CLKn 不能短于任意一組 DATA/DM/DQS。3.走線規(guī)則1)DDR3 的信號(hào)走線必須有完整參考面,以保證

2019-09-20 09:05:04

DDR布線在pcb設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的裕量。要保證系統(tǒng)的時(shí)序,線長(zhǎng)又是一個(gè)重要的環(huán)節(jié)。我們來(lái)回顧一下,DDR布線,線長(zhǎng)匹配的基本原則是:地址,控制/命令信號(hào)

2018-09-20 10:29:55

,這個(gè)要怎么理解?原來(lái)SDRAM在寫入或者讀取數(shù)據(jù)的時(shí)候是靠上升沿或者下降沿來(lái)觸發(fā)的,請(qǐng)注意,這里僅僅是上升沿或者下降沿,并不是上升沿和下降沿同時(shí)有效。如果時(shí)鐘頻率是800MHz,那么對(duì)應(yīng)的數(shù)據(jù)率就為

2016-11-08 16:59:51

PCB新手在PCB設(shè)計(jì)中應(yīng)該注意的問(wèn)題

2012-08-04 16:42:45

經(jīng)驗(yàn),畫(huà)過(guò)通訊、工業(yè)控制、嵌入式、數(shù)碼消費(fèi)類產(chǎn)品的高速、高密度、數(shù)模混合等PCB設(shè)計(jì)。處理高速信號(hào)很有經(jīng)驗(yàn),通過(guò)對(duì)于疊層的控制、信號(hào)的分類、拓?fù)浣Y(jié)構(gòu)的確定、微帶線帶狀線分析、阻抗的控制、時(shí)序的分析、平面

2013-03-26 14:52:54

,同時(shí)走線過(guò)細(xì)也使阻抗無(wú)法降低,那么在高速(>100MHz)高密度PCB設(shè)計(jì)中有哪些技巧? 在設(shè)計(jì)高速高密度PCB時(shí),串?dāng)_(crosstalk interference)確實(shí)是要特別注意

2012-03-03 12:39:55

平面。特征阻抗控制在50~60 Ω。信號(hào)線寬參考具體設(shè)計(jì)實(shí)施細(xì)則。信號(hào)組與其他非DDR信號(hào)間距至少保持在20 mil以上。組內(nèi)信號(hào)應(yīng)該與DDR時(shí)鐘線長(zhǎng)度匹配,差距至少控制在25 mil內(nèi)。串聯(lián)匹配

2017-10-16 15:30:56

阻抗匹配。串行電阻的阻值為20~75Ω,阻值大小與信號(hào)頻率成正比,與PCB走線寬度和長(zhǎng)度成反比。在嵌入式系統(tǒng)中,一般頻率大于20M的信號(hào),PCB走線長(zhǎng)度大于5cm時(shí)都要加串行匹配電阻,例如系統(tǒng)中的時(shí)鐘信號(hào)

2019-02-14 14:50:45

布線在設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的時(shí)序裕量。要保證系統(tǒng)的時(shí)序,線長(zhǎng)匹配又是一個(gè)重要的環(huán)節(jié)。我們來(lái)回顧一下,布線,線長(zhǎng)匹配的基本原則是:地址,控制/命令信號(hào)與時(shí)鐘

2018-09-20 10:59:44

有過(guò)孔,因?yàn)檫^(guò)孔將增加走線的阻抗變化和信號(hào)的反射。其次,如果必須用內(nèi)層來(lái)布設(shè)時(shí)鐘,那么上下層應(yīng)該使用地平面來(lái)減小延遲。再次,如果電源平面上不幸引入時(shí)鐘噪聲會(huì)增加PLL抖動(dòng),那么在修改PCB設(shè)計(jì)時(shí)可以創(chuàng)建一個(gè)

2019-09-11 16:55:26

端接,以緩和對(duì)時(shí)序與信號(hào)完整性的影響。 關(guān)于PCB設(shè)計(jì)中的阻抗匹配問(wèn)題 問(wèn):在高速PCB設(shè)計(jì)時(shí)為了防止反射就要考慮阻抗匹配,但由于PCB的加工工藝限制了阻抗的連續(xù)性而仿真又仿不到,在原理圖的設(shè)計(jì)時(shí)

2012-07-21 14:42:35

能力,是因?yàn)槎鄠€(gè)時(shí)鐘負(fù)載造成。采用時(shí)鐘驅(qū)動(dòng)芯片,將一個(gè)時(shí)鐘信號(hào)變成幾個(gè),采用點(diǎn)到點(diǎn)的連接。選擇驅(qū)動(dòng)芯片,除了保證與負(fù)載基本匹配,信號(hào)沿滿足要求(一般時(shí)鐘為沿有效信號(hào)),在計(jì)算系統(tǒng)時(shí)序時(shí),要算上時(shí)鐘在驅(qū)動(dòng)

2013-12-27 09:47:22

電流所產(chǎn)生的噪聲便會(huì)出現(xiàn)在模擬電路區(qū)域內(nèi)。28、在高速PCB設(shè)計(jì)原理圖設(shè)計(jì)時(shí),如何考慮阻抗匹配問(wèn)題? 在設(shè)計(jì)高速PCB電路時(shí),阻抗匹配是設(shè)計(jì)的要素之一。而阻抗值跟走線方式有絕對(duì)的關(guān)系,例如是走在表面

2017-01-03 15:10:49

PCB設(shè)計(jì)相關(guān)經(jīng)驗(yàn)分享及PCB新手在PCB設(shè)計(jì)中應(yīng)該注意的問(wèn)題

2015-03-08 21:25:46

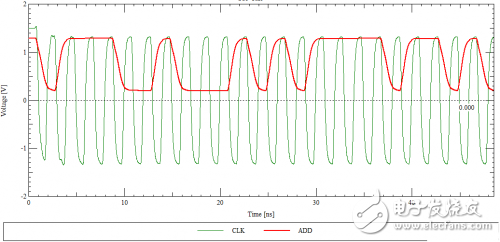

等長(zhǎng)是PCB設(shè)計(jì)的時(shí)候經(jīng)常遇到的問(wèn)題。存儲(chǔ)芯片總線要等長(zhǎng),差分信號(hào)要等長(zhǎng)。什么時(shí)候需要做等長(zhǎng),等長(zhǎng)約束條件是什么呢?首先,等長(zhǎng)的作用。由于信號(hào)在PCB走線上存在延時(shí),正比于信號(hào)線的長(zhǎng)度。假設(shè)PCB

2014-12-01 11:00:33

Ω,差分線控制80Ω~100Ω。 當(dāng)阻抗數(shù)值種類較多時(shí),需要考慮阻抗兼容問(wèn)題。 DDR3芯片本身可配置內(nèi)阻為40Ω,某些主芯片的DDR3接口內(nèi)阻也是按照40Ω設(shè)計(jì)阻抗的。 那么在PCB設(shè)計(jì)時(shí)

2023-04-12 15:12:13

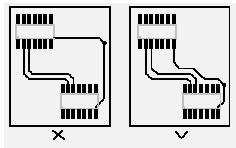

華秋DFM幫你忙,每日解決一個(gè)PCB設(shè)計(jì)問(wèn)題【今日問(wèn)題:孔到線】1、在PCB布局中,孔線之間的間距是極為重要的一環(huán);2、怎么樣的間距才是最安全的距離?3、需要注意什么規(guī)范才能保證PCB的良好運(yùn)行?4

2021-05-14 18:00:01

給大家分享一個(gè)在快點(diǎn)PCB學(xué)院看到的一篇經(jīng)驗(yàn)總結(jié);非常不錯(cuò)。 應(yīng)該是一個(gè)PCB設(shè)計(jì)高手的分享。 1、PCB板各層的含義是什么? Topoverlay ----頂層器件名稱, 也叫 top

2021-02-05 16:36:39

(芯板)的選擇可以是1.2MM也可以是1.0MM,只要層壓出來(lái)的板厚控制在一定范圍內(nèi),即可滿足成品板厚要求。另外就是板厚公差問(wèn)題,PCB設(shè)計(jì)人員在考慮產(chǎn)品裝配公差的同時(shí)要考慮PCB加工后板厚公差,影響成

2017-06-20 11:08:34

一名程序設(shè)計(jì)工程師時(shí),我記得,我們花太多的時(shí)間在代碼設(shè)計(jì)的檢視。但現(xiàn)在回頭看,我不得不承認(rèn),它們真的是這個(gè)過(guò)程中非常重要的一部分,這種重要性在PCB設(shè)計(jì)時(shí)也是一樣。雖然你可能認(rèn)為你的設(shè)計(jì)是完美無(wú)瑕的,且犯錯(cuò)

2018-09-17 17:43:59

PCB設(shè)計(jì)的可制造性分為哪幾類?PCB設(shè)計(jì)時(shí)考慮的內(nèi)容有哪些?

2021-04-21 06:16:30

在pcb設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的時(shí)序裕量。要保證系統(tǒng)的時(shí)序,線長(zhǎng)匹配又是一個(gè)重要的環(huán)節(jié)。我們來(lái)回顧一下,,線長(zhǎng)匹配的基本原則是:地址,控制/命令信號(hào)與時(shí)鐘做

2018-09-19 16:21:47

在DDR的PCB布線中提到,數(shù)據(jù)線可以分組等長(zhǎng),各組之間可以不等長(zhǎng),那怎樣保證32位數(shù)據(jù)的時(shí)序呢?

2023-04-10 16:49:54

在DDR的PCB布線中提到,數(shù)據(jù)線可以分組等長(zhǎng),各組之間可以不等長(zhǎng),那怎樣保證32位數(shù)據(jù)的時(shí)序呢?

2023-04-11 17:36:23

在PCB設(shè)計(jì)時(shí),如何設(shè)置不同大小的過(guò)孔并可以保存,然后在布線放置過(guò)孔時(shí)能夠在之前設(shè)置的過(guò)孔大小中隨意切換?求解,謝謝。

2016-10-13 08:43:45

在進(jìn)行PCB設(shè)計(jì)時(shí),需要遵守哪些原則?在設(shè)計(jì)RF布局時(shí),需要滿足哪些原則?

2021-04-21 06:50:45

HDMI接口PCB設(shè)計(jì),應(yīng)該怎么辦呢?小編認(rèn)為,在掌握PCB設(shè)計(jì)的基礎(chǔ)上,你至少需要滿足一次具有如下條件的項(xiàng)目實(shí)戰(zhàn):l以真實(shí)HDMI設(shè)計(jì)項(xiàng)目的實(shí)際案例作為實(shí)戰(zhàn)對(duì)象l該PCB設(shè)計(jì)項(xiàng)目代表的業(yè)務(wù)邏輯一定

2019-09-16 14:36:01

LTM4630電源模塊在多路并聯(lián)時(shí)在pcb設(shè)計(jì)時(shí)需要注意那些細(xì)節(jié)

比如在3路或者4路并聯(lián)時(shí)在畫(huà)pcb時(shí)走線需要注意那些地方,要加入對(duì)稱設(shè)計(jì)和阻抗匹配嗎,

如何才能做到并聯(lián)均流效果最好,

請(qǐng)大家提出一些建議和指導(dǎo),謝謝。

2024-01-05 08:07:28

存儲(chǔ)器控制器用戶指南列出了數(shù)據(jù),地址,控制和時(shí)鐘信號(hào)的長(zhǎng)度匹配要求。給出的數(shù)字是否必須補(bǔ)償FPGA和DDR2封裝內(nèi)的鍵合線長(zhǎng)度?如果是這樣,我在哪里可以找到這些長(zhǎng)度?謝謝,TL以上來(lái)自于谷歌翻譯以下

2019-03-15 10:06:16

我用esp8266 01模塊設(shè)計(jì)了一個(gè)電路。在我的最終設(shè)計(jì)中,我只想使用 esp8266ex 芯片和天線,不包括模塊中的閃光燈和晶體。我需要天線設(shè)計(jì)方面的幫助。天線的阻抗匹配應(yīng)該怎么做?請(qǐng)幫忙。

2023-05-30 08:10:22

的PCB里,這個(gè)就顯得不是完全的可行性,由于其信號(hào)線是靠近電源平面的,這就使得信號(hào)的返回路徑是由它們之間的耦合程度來(lái)決定的。所以,在4層的PCB設(shè)計(jì)時(shí),為符合電源完整性(power integrity

2019-07-30 07:00:00

使用Cadence仿真工具進(jìn)行信號(hào)完整性分析獲得端接匹配最優(yōu)方式,通過(guò)時(shí)序分析獲得PCB設(shè)計(jì)等長(zhǎng)約束。進(jìn)行電源完整性分析優(yōu)化電源布線布局優(yōu)化約束。配合熱仿真調(diào)整優(yōu)化PCB布局。在板材選型,使用背鉆技術(shù)等方面讓整個(gè)系統(tǒng)

2012-04-27 16:01:01

與負(fù)載基本匹配,信號(hào)沿滿足要求(一般時(shí)鐘為沿有效信號(hào)),在計(jì)算系統(tǒng)時(shí)序時(shí),要算上時(shí)鐘在驅(qū)動(dòng)芯片內(nèi)時(shí)延。3、2G以上高頻PCB設(shè)計(jì),走線,排版,應(yīng)重點(diǎn)注意哪些方面?2G以上高頻PCB屬于射頻電路設(shè)計(jì),不在

2018-03-20 21:38:26

在PCB設(shè)計(jì)中,布線是完成產(chǎn)品設(shè)計(jì)的重要步驟,可以說(shuō)前面的準(zhǔn)備工作都是為它而做的。在整個(gè)PCB設(shè)計(jì)中,布線的設(shè)計(jì)過(guò)程限定最高,技巧最細(xì),工作量最大。PCB布線分為單面布線,雙面布線以及多層布線3種

2018-12-07 22:50:21

元器件一般情況下盡量集中放置,可以減小線長(zhǎng),降低噪聲。但如果是有時(shí)序要求限制的信號(hào)布線,則需要根據(jù)線長(zhǎng)和結(jié)構(gòu)進(jìn)行布局的調(diào)整,具體應(yīng)該通過(guò)仿真來(lái)確定。旁路電容需要盡量靠近芯片電源引腳放置,尤其是高頻電容,在電源接口附近可以放置大容量(如47uF)的電容,以保持電源穩(wěn)定,降低低頻噪聲的干擾。

2019-09-12 14:47:17

%-50%的成功率。本次給大家介紹在PCB設(shè)計(jì)過(guò)程中電源平面處理應(yīng)該考慮的基本要素。1、做電源處理時(shí),首先應(yīng)該考慮的是其載流能力,其中包含 2 個(gè)方面。a)電源線寬或銅皮的...

2021-12-28 06:21:13

電源平面的處理,在PCB設(shè)計(jì)中占有很重要的地位。在一個(gè)完整的設(shè)計(jì)項(xiàng)目中,通常電源的處理情況能決定此次項(xiàng)目30%-50%的成功率,本次給大家介紹在PCB設(shè)計(jì)過(guò)程中電源平面處理應(yīng)該考慮的基本要素。 1

2021-12-31 07:17:08

它在時(shí)鐘觸發(fā)沿的上、下沿都能進(jìn)行數(shù)據(jù)傳輸,所以即使在133MHz 的總線頻率下的帶寬也能達(dá)到2.128GB/s。它的地址與其它控制介面與SDRAM 相同,DDR不支持3.3V 電壓的LVTTL,而是支持

2012-09-17 21:15:33

` 在PCB設(shè)計(jì)中,布線是完成產(chǎn)品設(shè)計(jì)的重要步驟,可以說(shuō)前面的準(zhǔn)備工作都是為它而做的。在整個(gè)PCB設(shè)計(jì)中,布線的設(shè)計(jì)過(guò)程限定最高,技巧最細(xì),工作量最大。PCB布線分為單面布線,雙面布線以及多層布線3

2018-11-23 16:07:58

和地層之間的EMC環(huán)境較差,應(yīng)避免布置對(duì)干擾敏感的信號(hào)。5. 有阻抗控制要求的網(wǎng)絡(luò)應(yīng)布置在阻抗控制層上。6. 進(jìn)行PCB設(shè)計(jì)時(shí)應(yīng)該遵循的規(guī)則1) 地線回路規(guī)則:環(huán)路最小規(guī)則,即信號(hào)線與其回路構(gòu)成的環(huán)面

2008-07-08 19:31:09

完整的地和電源平面。

3、為了防止串?dāng)_,本組內(nèi)信號(hào)不能和數(shù)據(jù)信號(hào)在同一個(gè)電阻排內(nèi)。

DDR信號(hào)等長(zhǎng)約束,由于DDR工作頻率高,對(duì)信號(hào)等長(zhǎng)有更嚴(yán)格的要求,實(shí)際的PCB設(shè)計(jì)中,對(duì)所有信號(hào)都進(jìn)行等長(zhǎng)控制是不太

2023-12-25 14:02:58

完整的地和電源平面。

3、為了防止串?dāng)_,本組內(nèi)信號(hào)不能和數(shù)據(jù)信號(hào)在同一個(gè)電阻排內(nèi)。

DDR信號(hào)等長(zhǎng)約束,由于DDR工作頻率高,對(duì)信號(hào)等長(zhǎng)有更嚴(yán)格的要求,實(shí)際的PCB設(shè)計(jì)中,對(duì)所有信號(hào)都進(jìn)行等長(zhǎng)控制是不太

2023-12-25 13:58:55

大家好,我正在研究我的第一個(gè)Kintex7 DDR3接口。為了實(shí)現(xiàn)RAM,我想在PCB上包含長(zhǎng)度匹配的封裝走線長(zhǎng)度。要獲取包延遲信息,我使用了命令(在Vivado中)link_design

2020-08-12 10:17:19

反射、串?dāng)_、信號(hào)延遲和時(shí)序錯(cuò)誤。1、反射:信號(hào)在傳輸線上傳輸時(shí),當(dāng)高速PCB上傳輸線的特征阻抗與信號(hào)的源端阻抗或負(fù)載阻抗不匹配時(shí),信號(hào)會(huì)發(fā)生反射,使信號(hào)波形出現(xiàn)過(guò)沖、下沖和由此導(dǎo)致的振鈴現(xiàn)象。過(guò)沖

2018-07-31 17:12:43

在高速PCB設(shè)計(jì)時(shí)為了防止反射就要考慮阻抗匹配,但由于PCB的加工工藝限制了阻抗的連續(xù)性而仿真又仿不到,在原理圖的設(shè)計(jì)時(shí)怎樣來(lái)考慮這個(gè)問(wèn)題?另外關(guān)于IBIS模型,不知在那里能提供比較準(zhǔn)確的IBIS

2012-03-03 12:41:55

的長(zhǎng)度數(shù)值如最后小結(jié)一下,在高速PCB設(shè)計(jì)中,隨著信號(hào)速率的逐步提高,時(shí)序等長(zhǎng)變得尤為重要。這要求快點(diǎn)PCB工程師在設(shè)計(jì)時(shí)不僅僅要考慮到PCB板內(nèi)信號(hào)的走線長(zhǎng)度,也要考慮到IC以及連接器(如DIMM

2016-11-09 11:15:00

、Stub、信號(hào)匹配(1)時(shí)序:總線一般會(huì)有傳輸延時(shí)、總線間時(shí)序關(guān)系(相對(duì)延時(shí))的要求,在PCB設(shè)計(jì)實(shí)現(xiàn)時(shí)需要考慮:從驅(qū)動(dòng)器到接收器的PCB走線長(zhǎng)度、一組總線的PCB布線等長(zhǎng)設(shè)計(jì);(2)Stub:通俗的說(shuō)

2016-10-14 16:53:15

我主要感興趣的方向是單片機(jī),開(kāi)關(guān)電源,還有PCB設(shè)計(jì)。我應(yīng)該怎么做來(lái)打好基礎(chǔ)?我不是電子系出身,但屬于工科。

2012-10-16 17:29:11

保持在20 mil以上。組內(nèi)信號(hào)應(yīng)該與DDR時(shí)鐘線長(zhǎng)度匹配,差距至少控制在25 mil內(nèi)。串聯(lián)匹配電阻RS值為O~33 Ω,并聯(lián)匹配電阻RT值應(yīng)該在25~68 Ω。本組內(nèi)的信號(hào)不要和數(shù)據(jù)信號(hào)組在同一個(gè)

2015-10-21 10:37:10

阻抗匹配阻抗匹配是指在能量傳輸時(shí),要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時(shí)的傳輸不會(huì)產(chǎn)生反射,這表明所有能量都被負(fù)載吸收了。反之則在傳輸中有能量損失。在高速PCB設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)

2014-12-01 10:38:55

我看了有些人的板在ddr2地址線加匹配電阻,數(shù)據(jù)線不加。有的人在數(shù)據(jù)線加匹配電阻地址線不加,到底應(yīng)該在那里加的,是參考DDR芯片的手冊(cè)還是參考TMS320C6748的手冊(cè)來(lái)做?

2019-01-21 13:50:55

我們定義了傳輸線效應(yīng)發(fā)生的前提條件,但是如何得知線延時(shí)是否大于1/2驅(qū)動(dòng)端的信號(hào)上升時(shí)間? 一般地,信號(hào)上升時(shí)間的典型值可通過(guò)器件手冊(cè)給出,而信號(hào)的傳播時(shí)間在PCB設(shè)計(jì)中由實(shí)際布線長(zhǎng)度決定。下圖為信號(hào)

2015-05-05 09:30:27

范圍,而不是等長(zhǎng)。又因?yàn)轱w行時(shí)間的最小時(shí)序要求一般都可以滿足,也就是第二個(gè)公式在很多場(chǎng)合可以忽略不計(jì),帶給PCB設(shè)計(jì)的要求就是符合第一個(gè)公式,結(jié)論就是走線越短越好。任何因?yàn)椴⒉淮嬖?b class="flag-6" style="color: red">時(shí)序要求而做的整個(gè)總線繞等長(zhǎng),而又為了繞等長(zhǎng)而導(dǎo)致這個(gè)總線的布線度增加,串?dāng)_增加,這樣的設(shè)計(jì)是錯(cuò)誤的,失敗的例子非常多。

2014-10-21 09:35:50

Ω。信號(hào)線寬參考具體設(shè)計(jì)實(shí)施細(xì)則。信號(hào)組與其他非DDR信號(hào)間距至少保持在20 mil以上。組內(nèi)信號(hào)應(yīng)該與DDR時(shí)鐘線長(zhǎng)度匹配,差距至少控制在25 mil內(nèi)。串聯(lián)匹配電阻RS值為O~33 Ω,并聯(lián)匹配電阻RT

2017-10-27 10:48:26

阻抗匹配阻抗匹配是指在能量傳輸時(shí),要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時(shí)的傳輸不會(huì)產(chǎn)生反射,這表明所有能量都被負(fù)載吸收了。反之則在傳輸中有能量損失。在高速PCB設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)的質(zhì)量?jī)?yōu)劣。

2019-05-31 08:12:33

。 問(wèn):在高速PCB設(shè)計(jì)中,串?dāng)_與信號(hào)線的速率、走線的方向等有什么關(guān)系?需要注意哪些設(shè)計(jì)指標(biāo)來(lái)避免出現(xiàn)串?dāng)_等問(wèn)題? 答:串?dāng)_會(huì)影響邊沿速率,一般來(lái)說(shuō),一組總線傳輸方向相同時(shí),串?dāng)_因素會(huì)使邊沿速率變慢

2019-01-11 10:55:05

是。給需要的網(wǎng)絡(luò)賦予該規(guī)則,在工作薄頂端就是Match Group組。以上便是PCB設(shè)計(jì)中約束管理器的匹配群組建立,上圖為完整的DDR數(shù)據(jù)組Match Group。

2017-07-27 11:06:26

數(shù)字系統(tǒng)對(duì)時(shí)序要求嚴(yán)格,為了滿足信號(hào)時(shí)序的要求,對(duì)PCB上的信號(hào)走線長(zhǎng)度進(jìn)行調(diào)整已經(jīng)成為PCB設(shè)計(jì)工作的一部分。調(diào)整走線長(zhǎng)度包括兩個(gè)方面:相對(duì)的和絕對(duì)的。 所謂相對(duì)的就是要求走線長(zhǎng)度保持一致

2018-11-27 15:22:54

PCB設(shè)計(jì)時(shí),注意控制走線時(shí)的阻抗控制,往往可以做到很好的匹配。 對(duì)于通常的聚酯膠片PCB 來(lái)說(shuō),傳輸線的長(zhǎng)度和微帶線 Stub 效應(yīng)是需要考慮的, 在本設(shè)計(jì)指南里面,主要是針對(duì) 4 層的 1080+2116 聚酯膠片PCB 進(jìn)行相關(guān)的阻抗匹配控制。

2019-05-17 10:40:14

挑戰(zhàn)。

在高速PCB設(shè)計(jì)中,阻抗匹配顯得尤為重要,為減少在高速信號(hào)傳輸過(guò)程中的反射現(xiàn)象,必須在信號(hào)源、接收端以及傳輸線上保持阻抗的匹配。

一般而言,單端信號(hào)線的阻抗取決于它的線寬以及與參考平面之間

2023-05-26 11:30:36

介紹采用Protel99 SE進(jìn)行射頻電路PCB設(shè)計(jì)的流程。為保證電路性能,在進(jìn)行射頻電路PCB設(shè)計(jì)時(shí)應(yīng)考慮電磁兼

2006-04-16 22:17:22 1352

1352 PCB設(shè)計(jì)時(shí)應(yīng)該遵循的規(guī)則

1) 地線回路規(guī)則:

環(huán)路最小

2007-12-12 14:48:15 1096

1096

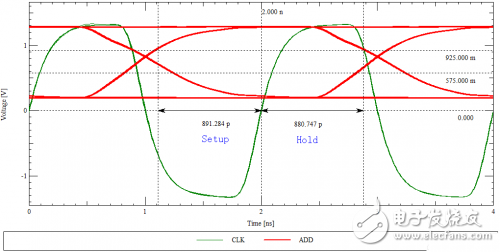

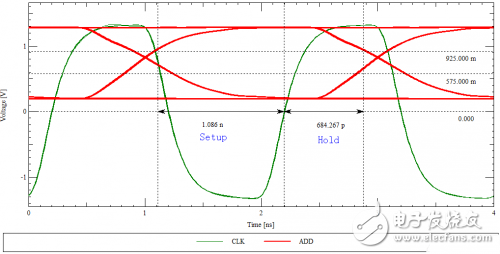

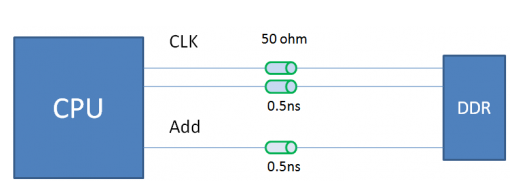

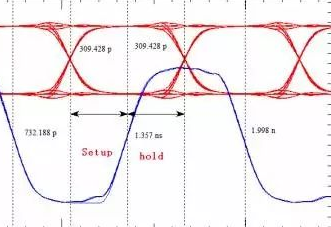

對(duì)于廣大PCB設(shè)計(jì)工程師而言,提到時(shí)序問(wèn)題就感覺(jué)比較茫然。看到時(shí)序圖,更是一頭霧水,感覺(jué)時(shí)序問(wèn)題特別深?yuàn)W。其實(shí)在平常的設(shè)計(jì)中最常見(jiàn)的是各種等長(zhǎng)關(guān)系,網(wǎng)上流傳的Layout Gu

2012-10-22 11:51:56 4104

4104

PCB設(shè)計(jì)相關(guān)經(jīng)驗(yàn)分享及PCB新手在PCB設(shè)計(jì)中應(yīng)該注意的問(wèn)題

2013-09-06 14:59:47 0

0 DDR4 PCB設(shè)計(jì)規(guī)范&設(shè)計(jì)要點(diǎn),DDR4 PCB設(shè)計(jì)規(guī)范&設(shè)計(jì)要點(diǎn)

2016-07-26 14:09:33 0

0 詳細(xì)介紹PCB設(shè)計(jì)時(shí)需要遵守的規(guī)則

2017-09-18 14:08:17 0

0 DDR布線在PCB設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的時(shí)序裕量。要保證系統(tǒng)的時(shí)序,線長(zhǎng)匹配又是一個(gè)重要的環(huán)節(jié)。我們來(lái)回顧一下,DDR布線,線長(zhǎng)匹配的基本原則是:地址,控制

2017-11-28 11:34:58 0

0 DDR布線在PCB設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的時(shí)序裕量。要保證系統(tǒng)的時(shí)序,線長(zhǎng)匹配又是一個(gè)重要的環(huán)節(jié)。我們來(lái)回顧一下,DDR布線,線長(zhǎng)匹配的基本原則是:地址,控制/命令信號(hào)與時(shí)鐘做等長(zhǎng)。

2018-09-27 09:56:00 6660

6660

本文檔的主要內(nèi)容詳細(xì)介紹的是Allegro PCB設(shè)計(jì)時(shí)等長(zhǎng)設(shè)置的一些方法與技巧解析。以DDR3(4pcs,fly-by 結(jié)構(gòu))為例,講述一下在allegro 中如何添加電氣約束(時(shí)序等長(zhǎng))。

2018-11-27 16:02:57 0

0 時(shí)序問(wèn)題最為重要,目前PCB設(shè)計(jì)者基本上采用核心芯片廠家現(xiàn)成方案,因此PCB設(shè)計(jì)中主要一部分工作是如何保證PCB能夠符合芯片工作要求時(shí)序。,目前國(guó)內(nèi)用戶基本沒(méi)有掌握時(shí)序問(wèn)題。少數(shù)SQ用戶會(huì)采用

2019-04-22 13:54:36 2984

2984 在高速PCB設(shè)計(jì)時(shí)為了防止反射就要考慮阻抗匹配,但由于PCB的加工工藝限制了阻抗的連續(xù)性而仿真又仿不到,在原理圖的設(shè)計(jì)時(shí)怎樣來(lái)考慮這個(gè)問(wèn)題?

2019-06-21 17:03:47 6432

6432 安規(guī)是產(chǎn)品認(rèn)證中對(duì)產(chǎn)品安全的要求,包括產(chǎn)品從設(shè)計(jì)到銷售到終端用戶整個(gè)過(guò)程。在PCB設(shè)計(jì)上,布線應(yīng)該滿足爬電距離與電氣間隙的要求,布線寬度也應(yīng)該具備足夠的通流能力。以下是PCB設(shè)計(jì)中的一些安規(guī)考慮。

2019-07-06 11:38:04 8346

8346 PCB設(shè)計(jì)時(shí)記住148個(gè)檢查項(xiàng)目,提升你的效率!

2019-08-20 08:42:08 3177

3177 為了保證線路板設(shè)計(jì)時(shí)的質(zhì)量問(wèn)題,在PCB設(shè)計(jì)的時(shí)候,要注意PCB圖布線的部分是否符合要求。

2019-09-02 10:12:36 2190

2190 數(shù)據(jù)信號(hào)與DQS做等長(zhǎng)。為啥要做等長(zhǎng)?大家會(huì)說(shuō)是要讓同組信號(hào)同時(shí)到達(dá)接收端,好讓接收芯片能夠同時(shí)處理這些信號(hào)。

2020-01-06 15:23:00 1414

1414 DDR布線在pcb設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的裕量。要保證系統(tǒng)的時(shí)序,線長(zhǎng)又是一個(gè)重要的環(huán)節(jié)。

2020-01-14 14:46:10 1188

1188 如果您閱讀了許多PCB設(shè)計(jì)指南,尤其是有關(guān)并行協(xié)議和差分對(duì)布線的指南,則將看到很多關(guān)于走線長(zhǎng)度匹配的內(nèi)容。當(dāng)您需要進(jìn)行跡線長(zhǎng)度匹配時(shí),您的目標(biāo)是最大程度地減少串行協(xié)議中的差分對(duì),并行協(xié)議中的多個(gè)

2021-01-05 10:56:22 3656

3656

在高速PCB設(shè)計(jì)時(shí)為了防止反射就要考慮阻抗匹配,但由于PCB的加工工藝限制了阻抗的連續(xù)性而仿真又仿不到,在原理圖的設(shè)計(jì)時(shí)怎樣來(lái)考慮這個(gè)問(wèn)題?

2020-11-12 17:09:06 4684

4684 點(diǎn)擊上面藍(lán)色字體,關(guān)注我們! PCB設(shè)計(jì)時(shí)DDR線寬和阻抗是如何確定下來(lái)的呢? 讓我們通一個(gè)具體的項(xiàng)目來(lái)學(xué)習(xí)一下。

2020-12-07 12:23:02 8681

8681 本文章主要涉及到對(duì)DDR2和DDR3在PCB設(shè)計(jì)時(shí),考慮信號(hào)完整性和電源完整性的設(shè)計(jì)事項(xiàng),這些是具有相當(dāng)大的挑戰(zhàn)性的。 文章重點(diǎn)是討論在盡可能少的PCB層數(shù),特別是4層板的情況下的相關(guān)技術(shù),其中

2021-03-25 14:26:01 3864

3864

為什么PCB設(shè)計(jì)時(shí)要考慮熱設(shè)計(jì)? PCB(Printed Circuit Board)設(shè)計(jì)是指通過(guò)軟件將電路圖轉(zhuǎn)化為PCB布局圖,以導(dǎo)出一個(gè)能夠輸出到電路板的文件。在進(jìn)行電路設(shè)計(jì)時(shí),我們需要考慮到

2023-10-24 09:58:27 331

331 什么是阻抗匹配?高速PCB設(shè)計(jì)為什么要控制阻抗匹配? 阻抗匹配是指在電路傳輸信號(hào)時(shí),控制電路中信號(hào)源、傳輸線和負(fù)載之間的阻抗相等的過(guò)程,從而確保信號(hào)的完整性和可靠性。在高速PCB設(shè)計(jì)中,阻抗匹配

2023-10-30 10:03:25 924

924 PCB設(shè)計(jì)時(shí)銅箔厚度,走線寬度和電流的關(guān)系

2022-12-30 09:20:39 15

15 PCB設(shè)計(jì)時(shí)銅箔厚度,走線寬度和電流的關(guān)系

2023-03-01 15:37:46 13

13 pcb板阻抗控制是指什么?pcb怎么做阻抗? PCB板阻抗控制是指在PCB(印刷電路板)設(shè)計(jì)和制造過(guò)程中,通過(guò)優(yōu)化電氣特性和信號(hào)完整性,確保設(shè)計(jì)滿足特定的阻抗要求。在高速數(shù)字和模擬電路中,阻抗控制

2024-01-17 16:38:04 722

722

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論