兩岸的IC設計公司在先進制程節點晶片設計和其復雜度的進展令全球半導體界矚目。于此同時,對領先EDA工具的需求也持續上升。

Cadence在今年上半年推出了Innovus設計實現系統,稱其為新一代的實體設計實現解決方案,使系統開發人員能夠在先進的16/14/10奈米FinFET制程以及其他成熟的制程節點上交付最佳功耗、性能和面積(PPA)指標的設計。

2015年10月中旬,我拜訪了Cadence位于美國矽谷的總部,與Cadence公司設計實作產品事業部的產品管理總監Vinay Patwardhan就如何進一步加速IC上市并同時提高PPA指標進行了面對面的交流。

Patwardhan于2013年加入Cadence,他積極參與了為市場帶來新的Signoff及數位實現工具的工作。在加入Cadence之前,他曾在Synopsys、Magma、Sun Microsystems以及Texas Instruments任職,擔任支援并設計高性能微處理器和ASIC的不同管理角色。

為什么Cadence要投資新的數字實現工具?

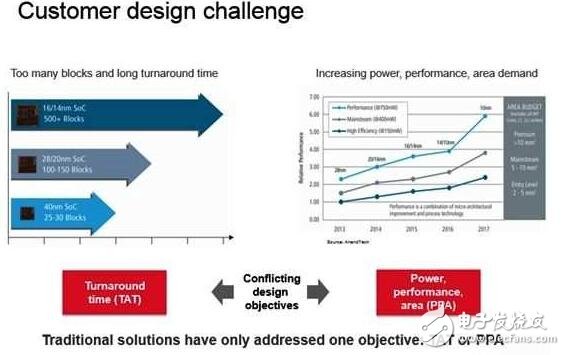

在過去的4~5年里,我們見證了產業中數位IC技術的巨大變化。關于周轉時間(turnaround time)、功耗、性能和面積最佳化都具有更嚴峻的挑戰,而這些挑戰使設計EDA工具變得越來越復雜。

我們收到一些客戶的回饋,他們很努力的在尋找解決方案以說明其設計新的晶片系統。Cadence已經具有一些基礎架構的工具,我們如何才能真正的創新并且把其發展到下一個解決客戶實際需求的工具?這對我們確實是個挑戰。

我們看到對資料中心、物聯網、汽車、通訊設備、尤其是行動運算領域的晶片需求在不斷增長。為了適應上述市場的變化,我們把開發工具在應用環境和技術上作了改進,來解決諸如周轉時間、面積和功耗方面的挑戰。同樣的,晶片在制造環節的每個技術節點變得越來越小也是一個挑戰,必須關注每一個不同制程節點的設計。

這就是Cadence為什么要開發新的數位實現軟體工具的原因。因為在這個過程中我們看到了市場在不斷擴大,并且我們的解決方案可以真正的服務我們的客戶。Cadence傳統上有一系列很好的模擬設計工具,投資于數位實現技術使得我們得以強化這些模擬工具,并且提供一套完整的解決方案來因應那些挑戰。

采用FinFET設計的晶片規模會很大,Cadence將如何應付更大、更復雜的晶片設計?

幾年前,工程師在設計IC時會用2,000至3,000萬閘(gate)。現在如果使用FinFET,尺寸會變得更小,速度變得更快,能夠放在一個晶片上的配置顯著增加。現在,SoC設計已進入到1億至1.2億閘的時代。當采用FinFET制程時,設計規模將變得更大。

以前,一個分區模組(partition)的容量通常為0.7百萬到1百萬的閘。但是現在,在晶片整體具有1.2億閘的情況下,你需要上百個分區模組,而且管理也變得非常復雜。所以我們需要更大的容量,以及能夠承載更大容量的先進技術。

我們要做的就是設計一個能夠大規模平行運算的架構使它能夠處理盡可能多的分區模組或閘,并且將它們聚集到至少一個分區模組里以同步運作。晶片變得越來越智慧并且需求量越來越大,我們有技能、技術和多種方式來處理容量很大的分區模組。

我們必須在核心演算法上做改變,因為這些FinFET晶片的特性跟以前大不相同,比如閘的結構、密度等。為了運算功率或FinFET晶片的面積,以前的一些核心演算法也增加它的功能來支持平行運算。

平行運算需要多執行緒、多核心和分布處理能力。其中,分散式處理(distributed parallel solution)可以采用不同的計算設備,可具備數百個CPU,我們就可以同時處理大量的分區模組。實際上,我們看到一些客戶正在推動5百萬以上instance的分區模組。事實上,Cadence已可以支援具有16個CPU、分區密度達1千萬 instance的模組。這就是我們所介紹的核心技術以及其的主要不同點。

FinFET制程也許可以推動PPA。那么,Cadence的工具又如何提升PPA?在動態功耗方面又如何最佳化?

通常來說,當制程由平面轉移到FinFET時,你必須最佳化PPA中的功耗性能和面積。而FinFET元件本身就有面積優勢以及更快更好的轉換速率。

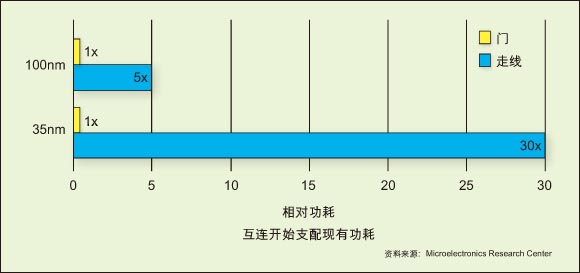

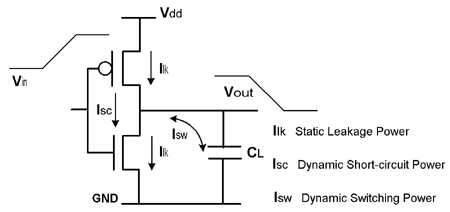

最初推出FinFET的動機有兩個:一是節省晶片30%的功耗,二是減小面積,進而提高性能。所以FinFET晶片的功耗最佳化跟以往的平面制程晶片有顯著的差別。以前我們必須要最佳化兩個部分:動態功耗和漏電功耗,尤其是漏電功耗,因為溝道變得越來越小。但現在FinFET本身就解決了漏電功耗的問題,動態功耗就變成一個非常重要的問題。

易用性高的設備有多種多樣的模式。比如手機有待機模式,那時漏電功耗就成為主要的問題,而當動態功耗變得越來越重要時,它就成為最主要的模式。所以,現在不能再僅僅只是最佳化動態功耗或者漏電功耗,你必須要最佳化整個功耗。

當最佳化整個功耗時你需要一些智慧工具來識別晶片的狀態,然后才能做出最佳化動態功耗或者漏電功耗的正確決定。

動態功耗對于FinFET變得十分重要。我們在Innovus數位工具中特別提供一個平滑的節點控制(node control)來最佳化漏電,同時最佳化動態功耗,并貫穿整個過程。這就是Innovus采用的功耗最佳化技術。

上面提到了功耗部分。就性能和面積而言,Cadence也有一些特別的產品。功耗最佳化是一方面,另一方面Innovus和Genus合成解決方案可分享一個共同的布局引擎(GigaPlace engine)。同時,slack可用來驅動布局引擎以改善PPA。另外,slack驅動布線演算法(slack driven routing)能盡早處理訊號完整性并改善布線前后的關聯性。這些布線引擎是全新重寫的,并且可以同時應用于Innovus和Genus。

Genus是一個RTL合成和實體合成工具。結合Genus的工作,Innovus已經有一個非常好的起點,設計人員可以在Innovus中更好地進行布線工作。這時,由于前期已做了很多的決策,就對后端的布線、最佳化等工作帶來巨大的益處。

除了功耗最佳化和布線技術以外,第三個提升PPA的關鍵新技術是時脈同步最佳化(CCOpt)。它所做的工作是同步最佳化時脈和資料通路,這是一個十分關鍵的時序技術。對于FinFET和更先進的制程節點來說,相關性變得非常重要。這項技術將會?明你提升晶片上不同Process Corner的時序性能,改善PPA中的功耗和面積性能。

作為一個總結,Innovus以及Genus等工具的特性包括它們可以共用引擎與緊密相關。

同時,對比市場上其他工具,透過結合使用前面提及的三個主要新技術,Innovus可以提供10%至20%的PPA性能提升。

Cadence將如何更好地幫助兩岸的半導體公司?

在過去的3~4年里,據我所知,在行動設備和IoT設備領域里,兩岸的半導體公司取得了顯著的進步,這些應用對控制功耗、面積的經驗都有非常高的要求,比如手機核心、處理器等,也需要能夠解決提升晶片PPA的工具。

Cadence與眾多晶圓代工廠緊密合作。晶圓代工廠對工具的認可具有嚴格的要求,我們與晶圓廠有標準的確認程式。理想情況下,IC設計公司在需要使用一款工具之前,Cadence已經和晶圓廠完成了工具的認證工作和參考設計流程。

我們和晶圓廠合作夥伴擁有共同的客戶。我們確定半導體公司,尤其是兩岸的半導體公司,透過這些工具能獲取一些更有價值的資訊和經驗,并且在短期內可以生產出具有競爭力的產品。我想我們與兩岸的IC設計公司一樣正在面對一些相似的問題:合并在不斷發生,有能力的公司變得更加強大,一些初創公司就面臨著要在短期內迅速發開出有競爭力的產品的挑戰。Cadence的工具,無論從類比、數位以及先進的技術,都適用于新公司或已成熟的公司。

我們期望從現在到2020年,Cadence會更多地與兩岸的IC設計公司合作,尤其在行動運算和IoT領域。

Cadence在今年上半年推出了Innovus設計實現系統,稱其為新一代的實體設計實現解決方案,使系統開發人員能夠在先進的16/14/10奈米FinFET制程以及其他成熟的制程節點上交付最佳功耗、性能和面積(PPA)指標的設計。

2015年10月中旬,我拜訪了Cadence位于美國矽谷的總部,與Cadence公司設計實作產品事業部的產品管理總監Vinay Patwardhan就如何進一步加速IC上市并同時提高PPA指標進行了面對面的交流。

Patwardhan于2013年加入Cadence,他積極參與了為市場帶來新的Signoff及數位實現工具的工作。在加入Cadence之前,他曾在Synopsys、Magma、Sun Microsystems以及Texas Instruments任職,擔任支援并設計高性能微處理器和ASIC的不同管理角色。

作者與Vinay Patwardhan在Cadence美國總部

為什么Cadence要投資新的數字實現工具?

在過去的4~5年里,我們見證了產業中數位IC技術的巨大變化。關于周轉時間(turnaround time)、功耗、性能和面積最佳化都具有更嚴峻的挑戰,而這些挑戰使設計EDA工具變得越來越復雜。

我們收到一些客戶的回饋,他們很努力的在尋找解決方案以說明其設計新的晶片系統。Cadence已經具有一些基礎架構的工具,我們如何才能真正的創新并且把其發展到下一個解決客戶實際需求的工具?這對我們確實是個挑戰。

我們看到對資料中心、物聯網、汽車、通訊設備、尤其是行動運算領域的晶片需求在不斷增長。為了適應上述市場的變化,我們把開發工具在應用環境和技術上作了改進,來解決諸如周轉時間、面積和功耗方面的挑戰。同樣的,晶片在制造環節的每個技術節點變得越來越小也是一個挑戰,必須關注每一個不同制程節點的設計。

這就是Cadence為什么要開發新的數位實現軟體工具的原因。因為在這個過程中我們看到了市場在不斷擴大,并且我們的解決方案可以真正的服務我們的客戶。Cadence傳統上有一系列很好的模擬設計工具,投資于數位實現技術使得我們得以強化這些模擬工具,并且提供一套完整的解決方案來因應那些挑戰。

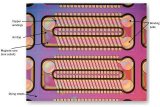

設計挑戰引發對新工具的需求

采用FinFET設計的晶片規模會很大,Cadence將如何應付更大、更復雜的晶片設計?

幾年前,工程師在設計IC時會用2,000至3,000萬閘(gate)。現在如果使用FinFET,尺寸會變得更小,速度變得更快,能夠放在一個晶片上的配置顯著增加。現在,SoC設計已進入到1億至1.2億閘的時代。當采用FinFET制程時,設計規模將變得更大。

以前,一個分區模組(partition)的容量通常為0.7百萬到1百萬的閘。但是現在,在晶片整體具有1.2億閘的情況下,你需要上百個分區模組,而且管理也變得非常復雜。所以我們需要更大的容量,以及能夠承載更大容量的先進技術。

我們要做的就是設計一個能夠大規模平行運算的架構使它能夠處理盡可能多的分區模組或閘,并且將它們聚集到至少一個分區模組里以同步運作。晶片變得越來越智慧并且需求量越來越大,我們有技能、技術和多種方式來處理容量很大的分區模組。

我們必須在核心演算法上做改變,因為這些FinFET晶片的特性跟以前大不相同,比如閘的結構、密度等。為了運算功率或FinFET晶片的面積,以前的一些核心演算法也增加它的功能來支持平行運算。

平行運算需要多執行緒、多核心和分布處理能力。其中,分散式處理(distributed parallel solution)可以采用不同的計算設備,可具備數百個CPU,我們就可以同時處理大量的分區模組。實際上,我們看到一些客戶正在推動5百萬以上instance的分區模組。事實上,Cadence已可以支援具有16個CPU、分區密度達1千萬 instance的模組。這就是我們所介紹的核心技術以及其的主要不同點。

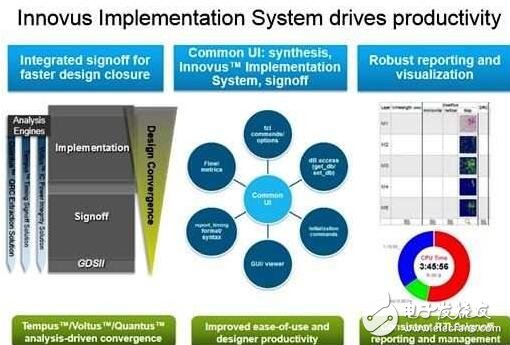

Innovus系統概念圖

FinFET制程也許可以推動PPA。那么,Cadence的工具又如何提升PPA?在動態功耗方面又如何最佳化?

通常來說,當制程由平面轉移到FinFET時,你必須最佳化PPA中的功耗性能和面積。而FinFET元件本身就有面積優勢以及更快更好的轉換速率。

最初推出FinFET的動機有兩個:一是節省晶片30%的功耗,二是減小面積,進而提高性能。所以FinFET晶片的功耗最佳化跟以往的平面制程晶片有顯著的差別。以前我們必須要最佳化兩個部分:動態功耗和漏電功耗,尤其是漏電功耗,因為溝道變得越來越小。但現在FinFET本身就解決了漏電功耗的問題,動態功耗就變成一個非常重要的問題。

易用性高的設備有多種多樣的模式。比如手機有待機模式,那時漏電功耗就成為主要的問題,而當動態功耗變得越來越重要時,它就成為最主要的模式。所以,現在不能再僅僅只是最佳化動態功耗或者漏電功耗,你必須要最佳化整個功耗。

當最佳化整個功耗時你需要一些智慧工具來識別晶片的狀態,然后才能做出最佳化動態功耗或者漏電功耗的正確決定。

動態功耗對于FinFET變得十分重要。我們在Innovus數位工具中特別提供一個平滑的節點控制(node control)來最佳化漏電,同時最佳化動態功耗,并貫穿整個過程。這就是Innovus采用的功耗最佳化技術。

上面提到了功耗部分。就性能和面積而言,Cadence也有一些特別的產品。功耗最佳化是一方面,另一方面Innovus和Genus合成解決方案可分享一個共同的布局引擎(GigaPlace engine)。同時,slack可用來驅動布局引擎以改善PPA。另外,slack驅動布線演算法(slack driven routing)能盡早處理訊號完整性并改善布線前后的關聯性。這些布線引擎是全新重寫的,并且可以同時應用于Innovus和Genus。

Genus是一個RTL合成和實體合成工具。結合Genus的工作,Innovus已經有一個非常好的起點,設計人員可以在Innovus中更好地進行布線工作。這時,由于前期已做了很多的決策,就對后端的布線、最佳化等工作帶來巨大的益處。

Innovus所采用技術的總結

除了功耗最佳化和布線技術以外,第三個提升PPA的關鍵新技術是時脈同步最佳化(CCOpt)。它所做的工作是同步最佳化時脈和資料通路,這是一個十分關鍵的時序技術。對于FinFET和更先進的制程節點來說,相關性變得非常重要。這項技術將會?明你提升晶片上不同Process Corner的時序性能,改善PPA中的功耗和面積性能。

作為一個總結,Innovus以及Genus等工具的特性包括它們可以共用引擎與緊密相關。

同時,對比市場上其他工具,透過結合使用前面提及的三個主要新技術,Innovus可以提供10%至20%的PPA性能提升。

Cadence將如何更好地幫助兩岸的半導體公司?

在過去的3~4年里,據我所知,在行動設備和IoT設備領域里,兩岸的半導體公司取得了顯著的進步,這些應用對控制功耗、面積的經驗都有非常高的要求,比如手機核心、處理器等,也需要能夠解決提升晶片PPA的工具。

Cadence與眾多晶圓代工廠緊密合作。晶圓代工廠對工具的認可具有嚴格的要求,我們與晶圓廠有標準的確認程式。理想情況下,IC設計公司在需要使用一款工具之前,Cadence已經和晶圓廠完成了工具的認證工作和參考設計流程。

我們和晶圓廠合作夥伴擁有共同的客戶。我們確定半導體公司,尤其是兩岸的半導體公司,透過這些工具能獲取一些更有價值的資訊和經驗,并且在短期內可以生產出具有競爭力的產品。我想我們與兩岸的IC設計公司一樣正在面對一些相似的問題:合并在不斷發生,有能力的公司變得更加強大,一些初創公司就面臨著要在短期內迅速發開出有競爭力的產品的挑戰。Cadence的工具,無論從類比、數位以及先進的技術,都適用于新公司或已成熟的公司。

我們期望從現在到2020年,Cadence會更多地與兩岸的IC設計公司合作,尤其在行動運算和IoT領域。

電子發燒友App

電子發燒友App

評論