本文提出一個(gè)基于FPGA的SPI Flash讀寫硬件實(shí)現(xiàn)方案,該方案利用硬件對(duì)SPI Flash進(jìn)行控制,能夠非常方便地完成Flash的讀寫、擦除、刷新及預(yù)充電等操作,同時(shí)編寫的SPI Flash控制器IP核能夠進(jìn)行移植和復(fù)用,作為SOC芯片的功能模塊。SPI Flash控制器采用VHDL語(yǔ)言進(jìn)行編寫,在Modelsim 6.5g上通過功能仿真,并且在XUPV5-LX110TFPGA開發(fā)板上通過硬件測(cè)試,實(shí)現(xiàn)結(jié)果表明方案的可行性。

1.引言

Flash是一種具有電可擦除的可編程ROM,按接口可以分為兩大類:并行Flash和串行 Flash.并行Flash存儲(chǔ)量大,速度快;而串行Flash存儲(chǔ)量相對(duì)較小,但體積小,連線簡(jiǎn)單,可減小電路面積,節(jié)約成本。SPI Flash是內(nèi)嵌SPI總線接口的串行Flash,它比起傳統(tǒng)的并行總線接口Flash,節(jié)省了很多的I/O口資源,從而為系統(tǒng)功能的擴(kuò)展提供了更多的可能。

隨著SPI Flash越來越多地應(yīng)用到各種領(lǐng)域,其傳統(tǒng)讀寫方式中讀寫速度不夠快、占用CPU資源以及操作不夠簡(jiǎn)便靈活的缺點(diǎn)表現(xiàn)得更為突出,如何解決以上問題成為大家關(guān)注的焦點(diǎn)。利用硬件對(duì)SPI Flash進(jìn)行控制,能夠非常方便地完成Flash的讀寫、擦除、刷新及預(yù)充電等操作,且不占用CPU資源,同時(shí)編寫的SPI Flash控制器IP核能夠進(jìn)行移植和復(fù)用,作為SOC芯片的功能模塊。因此提出了一種基于FPGA的SPI Flash控制器的設(shè)計(jì)方案,并用VHDL實(shí)現(xiàn)。編寫的SPI Flash控制器IP核在Modelsim 6.5g上進(jìn)行了功能仿真,在FPGA開發(fā)板上進(jìn)行了測(cè)試驗(yàn)證,可作為功能模塊應(yīng)用于SOC芯片設(shè)計(jì)。

2.SPI Flash控制器設(shè)計(jì)

2.1 SPI Flash芯片選擇

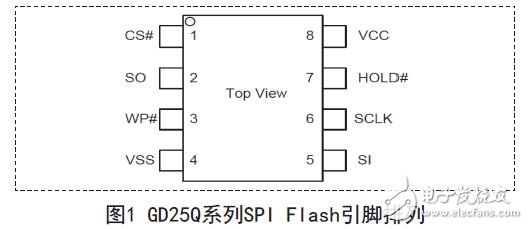

本方案SPI Flash芯片采用GigaDevice公司的GD25Q系列,GD25Q系列SPI Flash包括4Mbit的GD25Q40,2M bit的GD25Q20,1M bit的GD25Q10以及521K bit的GD25Q512,這里將采用512K bit的GD25Q512.圖1為GD25Q系列SPIFlash(SOP8封裝)引腳排列圖。其中VCC和VSS分別為電源和地,其他6個(gè)引腳均可直接與F P G A的I / O引腳相連;寫保護(hù)引腳W P #和HOLD#掛起引腳用于數(shù)據(jù)保護(hù)和空閑模式的低功耗運(yùn)行,若不使用可將其置為高電平;CS#為片選信號(hào),低電平時(shí)表示器件被選中,反之工作在待機(jī)狀態(tài);SO為串行數(shù)據(jù)輸出,數(shù)據(jù)在時(shí)鐘的下降沿輸出到Flash器件;SI為串行數(shù)據(jù)輸入,包括傳輸指令、地址和輸入數(shù)據(jù),輸入信號(hào)在時(shí)鐘的上升沿鎖存到 Flash器件中。SCLK為串行時(shí)鐘,由FPGA提供。

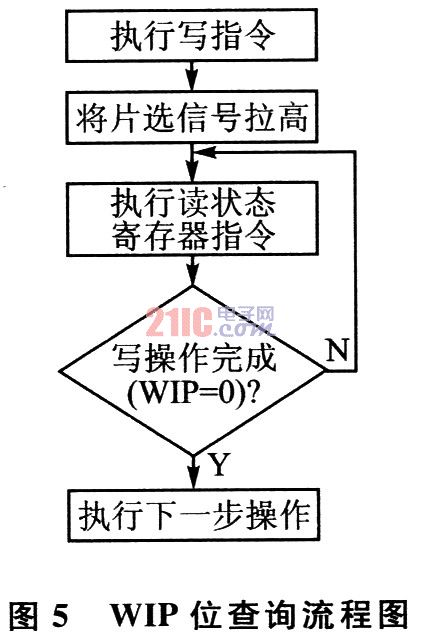

2.2 SPI Flash指令操作

GDQ25系列SPI Flash指令較多,所有指令都是8位,操作時(shí)先將片選信號(hào)CS#拉低選中器件,然后輸入8位操作指令字節(jié),串行數(shù)據(jù)在片選信號(hào)CS#拉低后的第一個(gè)時(shí)鐘的上升沿被采樣,SPI Flash啟動(dòng)內(nèi)部控制邏輯,自動(dòng)完成相應(yīng)操作。有些操作在輸入指令后需要輸入地址字節(jié)和偽字節(jié),最后操作完成后再將片選信號(hào)拉高。

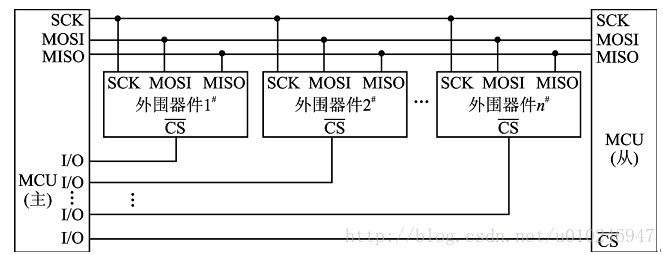

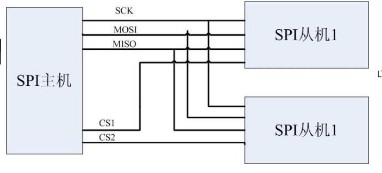

2.3 SPI Flash控制器設(shè)計(jì)原理

SPI Flash控制器必須能夠產(chǎn)生SPI Flash芯片執(zhí)行各操作(如寫使能、刷新、預(yù)充電、讀芯片ID、讀取狀態(tài)寄存器、寫狀態(tài)寄存器、扇區(qū)擦除、塊擦除、整體擦除、讀取數(shù)據(jù)、快速讀取數(shù)據(jù)、頁(yè)面編程)時(shí)所需指令時(shí)序,用戶只需要輸入對(duì)應(yīng)操作的8位指令值及對(duì)應(yīng)的操作地址值,SPI接口與SPI Flash的數(shù)據(jù)傳輸將由SPI Flash控制器內(nèi)部狀態(tài)機(jī)控制執(zhí)行。

3.SPI Flash控制器實(shí)現(xiàn)

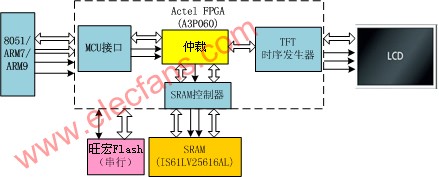

3.1 SPI Flash測(cè)試系統(tǒng)

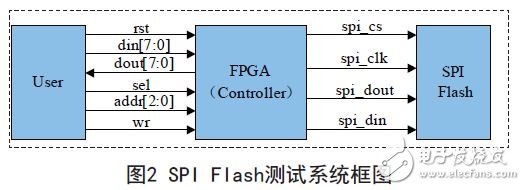

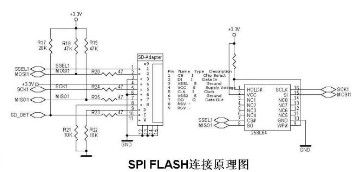

本文設(shè)計(jì)的SPI Flash測(cè)試系統(tǒng)由用戶端、FPGA和SPI Flash構(gòu)成,系統(tǒng)框圖如圖2所示,其中FPGA選用Xilinx公司Virtex5系列芯片(Virtex-5 XC5VLX110T),SPI Flash芯片采用GigaDevice公司的GD25Q系列512K bit容量的GD25Q512.

SPI Flash控制器由VHDL編寫,主要為SPIFlash芯片提供串行時(shí)鐘,將從用戶端輸入的數(shù)據(jù)(包括指令字節(jié)、地址字節(jié)和數(shù)據(jù)字節(jié))寄存起來并在串行時(shí)鐘的控制下通過spi_dout信號(hào)線逐位輸出到SPI Flash芯片中,同樣將從SPI Flash芯片中讀出的串行數(shù)據(jù)轉(zhuǎn)換成并行數(shù)據(jù)送給用戶端。此外,SPI Flash控制器還必須在用戶通過sel、addr以及wr組合發(fā)出的操作命令下產(chǎn)生一系列的控制信號(hào),并在這些控制信號(hào)的作用下根據(jù)狀態(tài)機(jī)的轉(zhuǎn)換方向進(jìn)行動(dòng)作并且輸出相應(yīng)的結(jié)果。

3.2 SPI Flash控制器控制狀態(tài)機(jī)

由于SPI Flash操作命令較多,并且很多操作命令之間存在相同的操作步驟,所以利用狀態(tài)機(jī)進(jìn)行控制能夠準(zhǔn)確有條理地完成對(duì)SPI Flash的操作。分析GDQ25系列SPI Flashdatasheet,可將SPI Flash控制器的工作狀態(tài)劃分為空閑狀態(tài)(IDLE)、傳輸指令狀態(tài)(TxCMD)、傳輸高字節(jié)地址狀態(tài)(TxADD_H)、傳輸中間字節(jié)地址狀態(tài)(TxADD_M)、傳輸?shù)妥止?jié)地址狀態(tài)(TxADD_L)、傳輸偽字節(jié)狀態(tài)(TxDummy)、傳輸數(shù)據(jù)狀態(tài)(TxDATA)和接收數(shù)據(jù)狀態(tài)(RxDATA)。除此以外,由于所有接收到的指令值都寄存在指令寄存器內(nèi),當(dāng)一條指令執(zhí)行完畢時(shí)需要將指令寄存器清空,以便接收下一條用戶指令,所以設(shè)定一個(gè)清除指令狀態(tài)(CLR_CMD)作為每一操作完成后的收尾狀態(tài)。當(dāng)狀態(tài)機(jī)進(jìn)入CLR_CMD狀態(tài)后,表示當(dāng)前操作已經(jīng)完成,正將指令寄存器指令值清空;當(dāng)狀態(tài)機(jī)進(jìn)入IDLE狀態(tài)時(shí),用戶可輸入下一操作指令,對(duì)SPI Flash進(jìn)行下一操作。考慮到SPI Flash的響應(yīng)時(shí)間,在以上工作狀態(tài)中間插入了一些等待狀態(tài)(WAIT)。

4.SPI Flash控制器驗(yàn)證

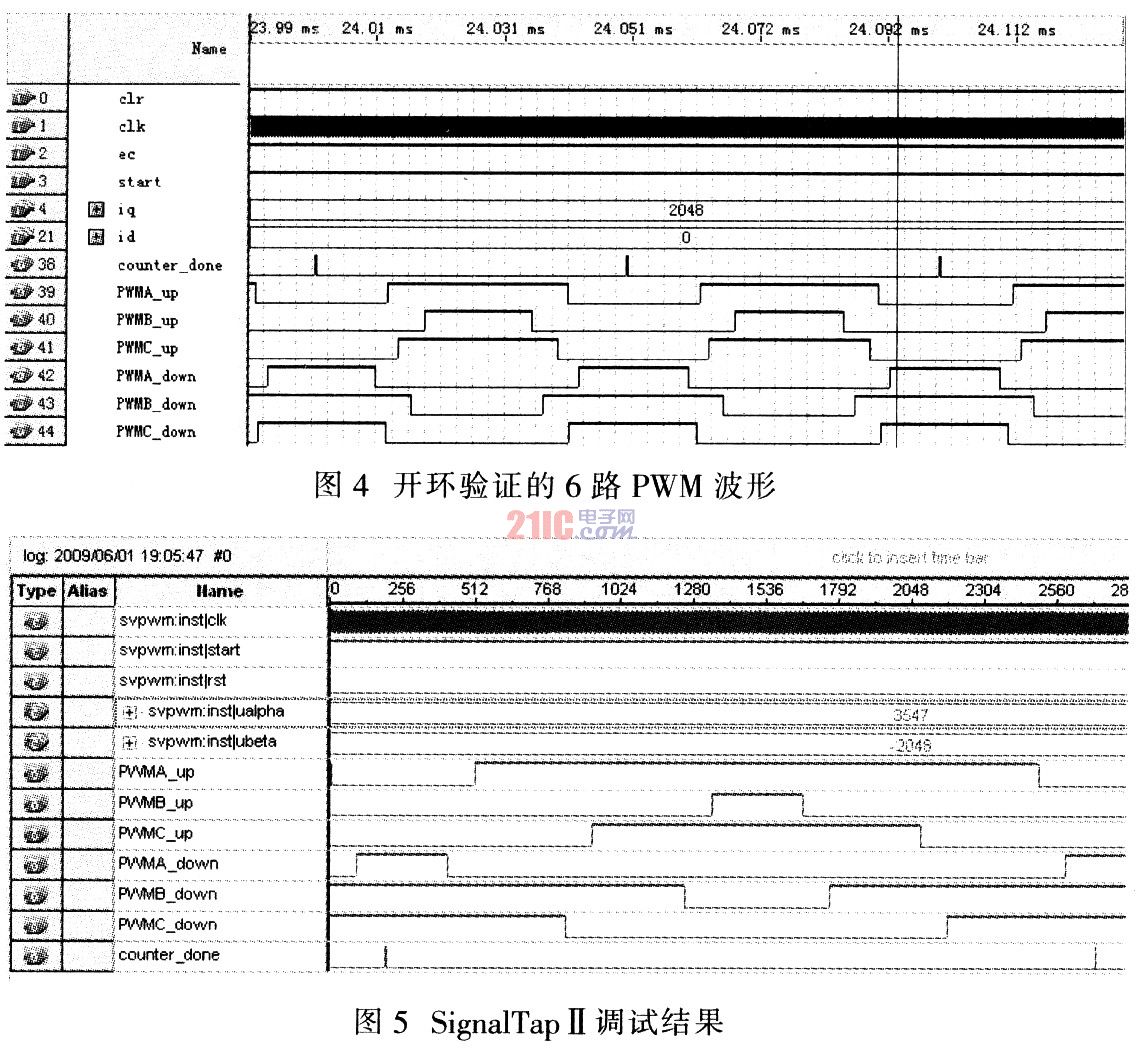

SPI Flash控制器IP核在Modelsim 6.5g上能夠通過功能仿真,下面分析一下SPI Flash頁(yè)面編程操作及數(shù)據(jù)讀取操作的功能仿真。

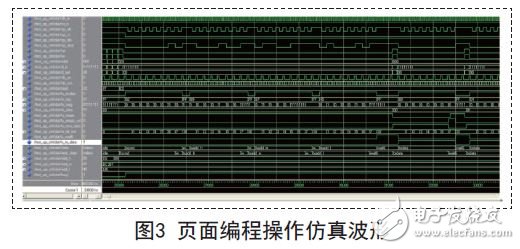

4.1 頁(yè)面編程操作

頁(yè)面編程操作仿真波形如圖3所示,圖中截取輸入00H和01H數(shù)據(jù)的波形,最多可連續(xù)輸入一頁(yè) 256字節(jié)數(shù)據(jù)。當(dāng)用戶輸入頁(yè)面編程指令02H,狀態(tài)機(jī)進(jìn)入txcmd狀態(tài),頁(yè)編程指令02H通過spi_dout傳輸給SPI Flash.當(dāng)tx_bit_cnt計(jì)數(shù)到8時(shí),指令傳輸完畢,狀態(tài)機(jī)在等待后進(jìn)入txadd_h狀態(tài),同時(shí)tx_bit_cnt被清零,需寫入數(shù)據(jù)的對(duì)應(yīng)存儲(chǔ)空間的起始地址高字節(jié)值89H被傳輸。當(dāng)tx_bit_cnt計(jì)數(shù)到8時(shí),高字節(jié)地址值89H被傳輸完畢,狀態(tài)機(jī)在等待后進(jìn)入txadd_m狀態(tài),同時(shí)tx_bit_cnt被清零,同上,地址中間字節(jié)67H和45H被傳輸。當(dāng)add_h、add_m和add_l寄存器的值依次傳輸完畢,狀態(tài)機(jī)進(jìn)入 wait6狀態(tài),等待用戶輸入需寫入SPI Flash的數(shù)據(jù)。當(dāng)用戶設(shè)定{sel,addr,wr}為10001b,狀態(tài)機(jī)進(jìn)入txdata狀態(tài),同時(shí)tx_new_data被置高,表示要傳輸新寫入的數(shù)據(jù)。在txdata狀態(tài)下,控制器將傳輸寫入的第1字節(jié)數(shù)據(jù)00H,當(dāng)tx_bit_cnt計(jì)數(shù)到8時(shí),第1字節(jié)數(shù)據(jù)00H被傳輸完畢,tx_new_data被拉低,tx_empty被拉高,表示當(dāng)前沒有可傳輸?shù)臄?shù)據(jù),狀態(tài)機(jī)進(jìn)入wait6狀態(tài),等待新數(shù)據(jù)寫入。直到用戶再次設(shè)定 {sel,addr,wr}為10001b,狀態(tài)機(jī)再次進(jìn)入txdata狀態(tài),同時(shí)tx_new_data被置高,表示寫入的第2字節(jié)數(shù)據(jù)01H將要傳輸。當(dāng)tx_bit_cnt計(jì)數(shù)到8,第2字節(jié)數(shù)據(jù)傳輸完畢,tx_new_data被拉低,tx_empty被拉高,狀態(tài)機(jī)進(jìn)入wait6狀態(tài)。由于 GDQ25系列SPI Flash頁(yè)面編程一次最多可寫入256字節(jié)數(shù)據(jù),所以用戶在寫入數(shù)據(jù)時(shí),應(yīng)注意最多寫入256次數(shù)據(jù),否則超過的數(shù)據(jù)將覆蓋開始的數(shù)據(jù)。當(dāng)狀態(tài)機(jī)處于 wait6狀態(tài)而用戶想結(jié)束頁(yè)面編程時(shí),可向控制器輸入NOP指令強(qiáng)制結(jié)束當(dāng)前頁(yè)面編程操作。狀態(tài)機(jī)在接收到NOP指令后將進(jìn)入clr_cmd狀態(tài)和 idle空閑態(tài),等待下一條指令的到來。當(dāng)頁(yè)面編程操作還沒結(jié)束時(shí),busy將一直被置高。

4.2 數(shù)據(jù)讀取操作

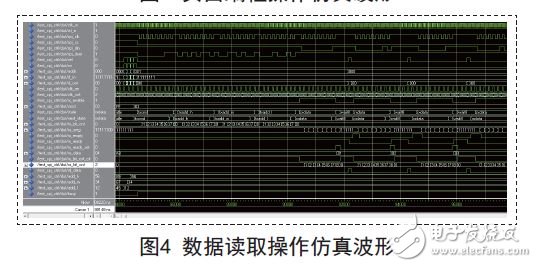

讀數(shù)據(jù)指令仿真波形如圖4所示。當(dāng)用戶輸入讀數(shù)據(jù)指令03H,狀態(tài)機(jī)進(jìn)入txcmd狀態(tài),讀數(shù)據(jù)指令通過spi_dout傳輸給SPI Flash。

當(dāng)tx_bit_cnt計(jì)數(shù)到8時(shí),指令傳輸完畢,狀態(tài)機(jī)等待后進(jìn)入txadd_h狀態(tài),傳輸要讀出數(shù)據(jù)所在存儲(chǔ)空間起始地址的高字節(jié),同時(shí)tx_bit_cnt清零,以為下一個(gè)傳輸作準(zhǔn)備。地址高字節(jié)寄存器add_h數(shù)值56H通過spi_dout 傳輸給SPI Flash,當(dāng)tx_bit_cnt計(jì)數(shù)到8時(shí),狀態(tài)機(jī)進(jìn)入txadd_m狀態(tài),傳輸?shù)刂分虚g字節(jié),同理,控制器在狀態(tài)txadd_m和狀態(tài) txadd_l狀態(tài)下完成傳輸?shù)刂分虚g字節(jié)34H和地址低字節(jié)12H.當(dāng)24位地址傳輸完畢,狀態(tài)機(jī)在等待后進(jìn)入rxdata狀態(tài),接收從spi_din 輸入的第一字節(jié)數(shù)據(jù)01H.當(dāng)rx_bit_cnt計(jì)數(shù)到8時(shí),控制器完成第1字節(jié)數(shù)據(jù)的接收,rx_data顯示為01H,狀態(tài)機(jī)狀態(tài)轉(zhuǎn)換為wait8 狀態(tài),等待用戶設(shè)定{sel,addr,wr}以接收第2字節(jié)。當(dāng)用戶設(shè)定{sel,addr,wr}為10000b時(shí),狀態(tài)機(jī)再次進(jìn)入rxdata狀態(tài),接收從spi_din輸入的第2字節(jié)數(shù)據(jù)02H,同時(shí)rx_ready被拉低,rx_empty被拉高,rd_data被拉高,表示將要讀出新輸入的數(shù)據(jù)。當(dāng)rx_bit_cnt計(jì)數(shù)到8時(shí),第2字節(jié)數(shù)據(jù)接收完畢,rx_ready被拉高,rx_empty為低,rd_data顯示新接收的字節(jié)數(shù)據(jù) 02H,狀態(tài)機(jī)經(jīng)等待后重新進(jìn)入wait8狀態(tài),等待用戶再次設(shè)定{sel,addr,wr}值,接收第3字節(jié)數(shù)據(jù)值,同理,可讀出SPI Flash內(nèi)部所有數(shù)據(jù)。

當(dāng)狀態(tài)機(jī)處于wait8狀態(tài)而用戶想退出讀數(shù)據(jù)操作時(shí),可向控制器輸入NOP指令強(qiáng)制結(jié)束當(dāng)前讀數(shù)據(jù)操作。狀態(tài)機(jī)在接收到NOP指令后將進(jìn)入clr_cmd狀態(tài)和idle空閑態(tài),等待下一條指令的到來。當(dāng)讀數(shù)據(jù)操作還沒結(jié)束時(shí),busy將一直置高。

5.結(jié)語(yǔ)

目前SPI Flash控制器IP核已經(jīng)在XUPV5-LX110T FPGA開發(fā)板上通過硬件測(cè)試,并且將作為功能模塊應(yīng)用于SOC芯片設(shè)計(jì)。實(shí)踐證明,基于FPGA的SPI Flash控制器能夠簡(jiǎn)化SPI Flash讀寫操作流程,從而提高SPI Flash的讀寫速度,而操作時(shí)不占用CPU資源的特點(diǎn),將使SPIFlash的讀寫更有優(yōu)勢(shì)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論