汽車信息娛樂應用中PLD管理圖像數據 - 全文

?

信息娛樂系統能在幫助司機安全前往目的地的同時娛樂乘客,而且這已不再是高檔車輛的專利:現在新興的汽車輔助駕駛系統正進入主流市場。前面的液晶顯示器需要動態地從GPS顯示器切換到許多攝相機中的一個,甚至是由車輛周圍的幾架照攝相機拍攝的圖像的組合。后面攝相機的圖像協助平行停車,確保離開停車位和安全駕駛在車道上,并避免與迎面而來的車輛碰撞。為了擴大司機在繁忙的十字路口的視野,前置攝像頭(兩個前輪上方的車身上安裝的兩個攝相機)可以顯示圖像。一些車輛能夠提供“查看周圍的圖像”,這基本上是一個圍繞車身的虛擬的360度視野,它們來自前面(尖端的引擎蓋),后部和兩邊(側鏡)的攝相機拍攝的圖像。對于不同尺寸的液晶顯示屏,這些圖像可能需要縮放(大小),調整和增強以提高圖像質量。

管理圖像數據需要新的IC。專用集成電路非常昂貴并具有風險,而ASSP又不靈活。可編程邏輯器件(PLD)克服了這些缺點,但用于圖像數據面臨著接口的挑戰,這往往需要很高的性能,而且可編程邏輯器件的使用成本高。然而這種情況正在改變。現已推出新一代低成本具有高性能IO緩沖器的可編程邏輯器件。這些低成本的可編程邏輯器件提供高效的傳輸、處理,操作和數字數據的顯示,同時使產品差異化,幫助實現產品上市時間和成本效益的目標。

傳送圖像數據

采用了各種方法在車輛上傳輸圖像數據。一種常見的方法是使用LVDS來建立源同步接口。

一種適用于視頻應用的流行技術是采用7:1 LVDS(低壓差分信號)接口。通道連接,攝相機連接,平面顯示器連接和FlatLink是這種方法的變種。LVDS是一種高速、低功耗,通用接口標準。它采用一對產生大小相等且方向相反的電流的差分信號,這也有助于降低總的輻射。此外,LVDS使用電流模式驅動,限制了功耗。美國國家半導體公司開發了基于LVDS的通道連接和FPD連接(平板顯示連接)技術,作為平板顯示器的解決方案,支持從圖形控制器到LCD面板的數據傳輸。該技術后來被擴展為一個通用數據傳輸方式。攝相機連接是一個基于7:1 LVDS的標準,使用多達28位的數據,時鐘頻率可達85Gpbs,總吞吐量為2.38兆赫。德州儀器公司的FlatLink提供21:3或28:4的配置,支持4位、6位或8位RGB。

用低成本可編程邏輯器件挑戰實現LVDS7:1

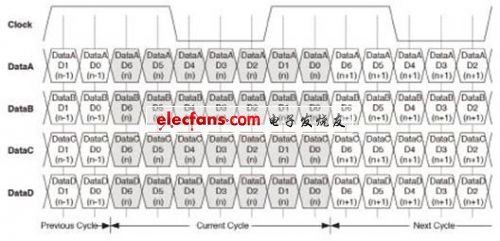

7:1 LVDS接口通常使用的三到五個LVDS數據通道和一個LVDS時鐘通道。更高分辨率的顯示器會使用四或五個LVDS數據通道。在一個時鐘周期或周期中,在每個數據通道有7個串行位,如圖1所示。

?

圖1 7:1 LVDS接口的時序

用低成本的可編程邏輯器件實現LVDS接口7:1的挑戰包括高速LVDS緩沖器和用于產生解串時鐘的PLL,能夠捕獲輸入的數據,具有高效,準確的匹配和數據格式化。

高速LVDS緩沖器:必須能夠以相對較高的速度接收或發送數據和時鐘至或來自可編程邏輯器件。準確的速度取決于分辨率、幀速率和顯示器使用的顏色深度。例如,針對60赫茲到75赫茲的刷新率,800×600到1024×768的顯示器需要LVDS數據發送從40兆赫至78.5兆赫的頻率。這轉換成LVDS數據速率為280Mbps至549Mbps。更高分辨率的顯示器,如1280×1024、60赫茲,要求數據必須與一個108MHz的時鐘一起傳輸。對于這些系統,數據以756 Mbps傳輸。

時鐘發生器:通常的方法是接收輸入時鐘和使用一個鎖相環,對每個數據位7倍于時鐘頻率。實際上,這是相當困難的,因為時鐘運行速度極快。由于典型的顯示接口的時鐘速率為60MHz~100MHz或更高,乘以7產生420MHz到700MHz的頻率。以這些時鐘速率工作,任何圖像控制和處理就不可能用一個低成本的PLD來實現。

數據采集,匹配及格式化:緊隨LVDS輸入緩沖器的寄存器必須準確地捕捉到數據。嚴格的時鐘和數據關系的控制是很重要的,以捕獲送入的高速數據流。這也是必要的匹配(減少)前面傳遞到PLD的數據速度。如果輸入捕捉電路只運行在一個時鐘的邊沿,應該生成七個低速時鐘的相移,用七個不同寄存器捕獲輸入數據。時鐘產生和分配的挑戰阻礙了用PLD來實現。時鐘必須具有相對較低的抖動,因為其抖動必須計算在整個時序預算中。同樣,在任何時序分析之中,必須考慮用于提供該時鐘輸入或輸出寄存器的時鐘分配網絡的偏移。

在MachXO2 器件中實現7:1 LVDS的實例

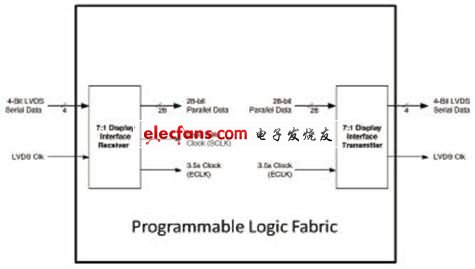

可編程邏輯器件MachXO2具有特定功能的架構,支持7:1 LVDS接口。這些特性包括高性能的LVDS I/O緩沖器、雙數據速率(DDR)I/O寄存器,匹配邏輯和具有專用3.5時鐘分頻器的高精度鎖相環。這些特性和功能提供了一套完整的解決方案。MachXO2器件提供了多達21個數據通道。圖2顯示了接收器和發送器的四個數據通道。

?

圖2 在MachXO2中的接收器和發送器

在此圖中,MachXO2器件的接收模塊接收四個數據通道,以及通過LVDS I/O緩沖器的時鐘。這些緩沖器可以運行高達303兆赫(606 Mbps),支持高分辨率,顯示刷新速率高達85 MHz的像素速率(SXGA)。 PLL是用3.5乘以時鐘。然后通過一個低偏移邊緣的時鐘網至DDR捕獲寄存器來分配較快的移相時鐘(ECLK)。LVDS的數據送入具有7:1匹配功能的DDR寄存器。這個匹配使得I/O數據與高速EDGE時鐘(ECLK)解多路復用,然后至較慢速度的FPGA時鐘頻率(SCLK)。

這個7:1 LVDS的解決方案包括自動對齊PLL輸出時鐘到最佳位置,用于對輸入LVDS數據流采樣,為自動對齊可編程邏輯器件的時鐘至輸入數據字添加邏輯。這些“軟”的邏輯與“硬”資源相呼應,提供完整的顯示接口解決方案。

MachXO2 PLD的發送模塊接收28位并行數據和快速的DDR時鐘(ECLK)。并行數據送入到具有7:1匹配功能的顯示I / O邏輯單元。匹配功能使得具有低速系統時鐘(SCLK)的輸入數據復用至更高速度的DDR輸出邊緣時鐘速率(ECLK)。

總結

用許多圖像源(幾個攝像機)來增加數字內容,后座顯示屏和導航系統正在進入主流市場。

在圖像應用方面,由于成本和功耗的優勢,預計7:1 LVS接口將依然流行,例如車載信息娛樂系統。

MachXO2器件可以部署在汽車輔助駕駛系統來管理來自攝像機的圖像的顯示和操作(縮放,旋轉等)。MachXO2器件可以從一臺攝像機到其他攝像機顯示圖像之間進行動態切換,或將兩者組合在一起。

- 第 1 頁:汽車信息娛樂應用中PLD管理圖像數據

- 第 2 頁:LVDS的實例

本文導航

非常好我支持^.^

(0) 0%

不好我反對

(0) 0%

相關閱讀:

- [電子說] 可配置混合信號芯片 2023-10-18

- [PCB設計] 用于系統級測試和PCB配置的拓撲結構 2023-10-17

- [電子說] 單片機_DSP_PLD/EDA的比較和分析 2023-10-15

- [電子說] java如何處理圖片水印 2023-10-09

- [電子說] 利用FPGA設計基于LVDS的圖像數據采集傳輸系統 2023-09-28

- [電子說] 基于ARM和FPGA設計高速圖像數據采集傳輸系統 2023-09-27

- [可編程邏輯] 什么叫可編程邏輯器件 可編程邏輯器件有哪些特征和優勢? 2023-09-14

- [可編程邏輯] 深度解析CPLD和FPGA內部結構和原理 2023-08-29

( 發表人:葉子 )