數(shù)字控制振蕩器,數(shù)字控制振蕩器電路原理分析

數(shù)字控制振蕩器,數(shù)字控制振蕩器電路原理分析

在實(shí)際的通信系統(tǒng)中,攜帶數(shù)字信息的信號(hào)通常是由某種類型的載波調(diào)制方式發(fā)送的,傳送信號(hào)的帶寬限制在以載波為中心的一個(gè)頻段上,如雙邊帶調(diào)制,或在鄰近載波的頻段上,如單邊帶調(diào)制。無論何種調(diào)制方式,在發(fā)送端均需要一個(gè)高頻載波將信息調(diào)制上去,以減小信號(hào)衰落,相干解調(diào)時(shí)在接收端也需要一個(gè)與發(fā)送端同頻同相的高頻載波將信息從高頻上解調(diào)下來。為了產(chǎn)生這個(gè)高頻載波,在數(shù)字電路中是采用數(shù)控振蕩器(NCO),也稱為直接數(shù)字頻率合成器〔DDS),它的輸出頻率和相位可以受人為控制,從而滿足各種需要。

基本原理:

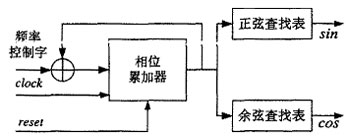

下圖為NCO的工作原理框圖:

數(shù)控振蕩器一般由基準(zhǔn)時(shí)鐘(fclk)、相位字寄存器、相位累加器以及幅度/相位轉(zhuǎn)換電路等部分組成。在基準(zhǔn)時(shí)鐘的作用下,每一個(gè)時(shí)鐘周期存貯在相位字寄存器里的值都由相位累加器進(jìn)行累加,相位果加器的輸出作為查找表的輸人,從而得到相對(duì)應(yīng)的幅度值。根據(jù)奈奎斯特采樣定律,輸出信號(hào)的頻率應(yīng)小于基準(zhǔn)時(shí)鐘的1/2。

相位累加器輸出(△Ф)的數(shù)值和系統(tǒng)的頻率(fclk)決定了輸出頻率(fout),它門的關(guān)系如下:

![]()

N是相位寄存器的位數(shù),N值的大小決定了頻率分辨率(fres ),有

![]()

在這里假設(shè),fclk=128MHz, N=32,可以計(jì)算出NCO的頻率分辨率fres=0.0298Hz

相位累加器是決定NCO電路性能的一個(gè)關(guān)鍵部分。我們可以采用了Altera的加法器宏功能模塊形成一個(gè)32bit的累加器,它以流水線處理方式進(jìn)行工作。

相位/幅 度轉(zhuǎn)換電路是NCO電路中的另一個(gè)關(guān)鍵部分,在設(shè)計(jì)中面臨的主要問題就是資源的開銷。

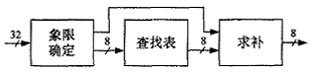

一般電路采用ROM結(jié)構(gòu),相位累加器的輸出是一種數(shù)字式鋸齒波,通過取它的若干位作為ROM的地址輸人,而后通過查表和運(yùn)算,ROM就能輸出所需波形的量化數(shù)據(jù)。

在APEX器件中,ROM由EAB實(shí)現(xiàn),ROM表的尺寸隨著地址位數(shù)或數(shù)據(jù)位數(shù)的增加成指數(shù)遞增關(guān)系,因此在滿足信號(hào)性能的前提條件下,如何減少資源的開銷就是一個(gè)重要的問題。

在實(shí)際設(shè)計(jì)時(shí),要充分利用信號(hào)周期內(nèi)的對(duì)稱性和算術(shù)關(guān)系來減少EAB的開銷。

上圖為產(chǎn)生正弦信號(hào)的相位/幅度轉(zhuǎn)換電路,相位累加器累加值的最高位(MSB )和次最高位(MSB-1)的組合作為象限確定模塊的輸人,由此來確定輸出信號(hào)所在的相平面和極性符號(hào),如表所示。

正弦查找表存貯了1/4周期的正弦幅度數(shù)據(jù),通過象限確定模塊就可以完成完整的正弦波的形成。這里采用了一個(gè)256 x 8的ROM宏模塊。地址線和數(shù)據(jù)線輸出均為8bit, 8bit地址分別對(duì)應(yīng)相位累加器的30-23bit的輸出數(shù)據(jù)。正弦查找表的輸出是無符號(hào)的8bit數(shù)據(jù),并不能代表正弦波形。求補(bǔ)模塊根據(jù)象限確定模塊的輸出符號(hào)位的極性來對(duì)查找表輸出數(shù)據(jù)進(jìn)行求補(bǔ),并把此符號(hào)位和正弦查找表輸出的高7bit組合作為最終正弦波輸出信號(hào)。

非常好我支持^.^

(4) 20%

不好我反對(duì)

(16) 80%

相關(guān)閱讀:

- [電子說] 全志R128應(yīng)用開發(fā)案例—獲取真隨機(jī)數(shù) 2023-10-24

- [控制/MCU] 單片機(jī)學(xué)習(xí)筆記 2023-10-24

- [電子說] 運(yùn)算放大器反相輸入端電壓高于同相輸入端會(huì)怎樣?輸出是什么樣子? 2023-10-24

- [電子說] 經(jīng)典的簡(jiǎn)單型晶體測(cè)試儀電路圖講解 2023-10-24

- [電子說] 基于555芯片的振蕩器電路分析 2023-10-24

- [電子說] MLCC的結(jié)構(gòu)、特點(diǎn)、應(yīng)用及發(fā)展趨勢(shì) 2023-10-23

- [電子說] 提高支付體驗(yàn):YXC揚(yáng)興科技 有源晶振 YSO110TR高精度刷卡器 2023-10-23

- [模擬技術(shù)] 談?wù)勲p三極管驅(qū)動(dòng)LED的多諧振蕩器 2023-10-23

( 發(fā)表人:admin )