PCIe標準自從推出以來,1代和2代標準已經在PC和Server上逐漸普及,用于滿足高速顯卡、高速存儲設備對于高速數據傳輸的要求。出于支持更高總線數據吞吐率的目的,PCI-SIG組織在2010年制定了PCIe 3.0,即PCIe 3代的規范,數據速率達到8Gbps。

2023-02-13 15:01:02 3217

3217

泰克公司日前宣布,在4月10日--11日于北京中國國家會議中心舉辦的2013英特爾信息技術峰會(IDF)上展示業界最完整、最靈活的高速串行信號測試解決方案,為高速數據設計人員解決USB 3.0、PCIe Gen3/4、SATA等高速串行信號測試帶來的挑戰,并大幅縮短測試和調試時間。

2013-04-10 11:17:54 1152

1152 業界領先的串行高速連接、信號調節和時頻解決方案供應商百利通半導體公司(Pericom,納斯達克股票市場代碼:PSEM)日前宣布:面向移動和相關應用中最新CPU芯片組的先進連接需求,推出全新轉換器和電源管理產品。

2013-04-11 16:09:32 1140

1140 業界領先的高速連接、信號調節和時頻解決方案供應商百利通半導體公司(Pericom Semiconductor Corporation,納斯達克股票市場代碼:PSEM)今日宣布:推出一個全新的帶有溫度

2013-05-08 10:24:20 1585

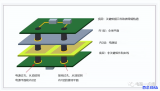

1585 時鐘信號是由PCIE主機給到PCIE從機的,所以信號流向是指向左下角的。而此時的信號回流路徑包含包地路徑和地平面路徑。

2020-11-19 15:26:00 3513

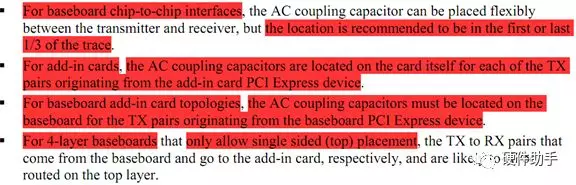

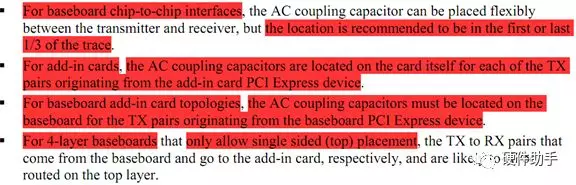

3513 本篇主要介紹PCIe總線的AC耦合電容、總線的去加重等高速信號調整技術。 AC耦合電容可以參考之前的文章《邏輯電平之差分互連AC耦合電容(7)》,本文主要針對PCIe接口介紹AC耦合電容的實際使用

2020-12-22 16:54:15 10606

10606

信號完整性仿真重點分析有關高速信號的3個主要問題:信號質量、串擾和時序。對于信號質量,目標是獲取具有明確的邊緣,且沒有過度過沖和下沖的信號。

2023-04-03 10:40:07 889

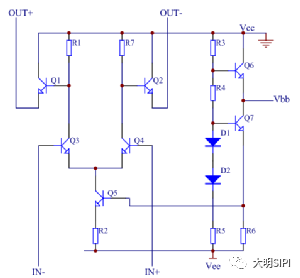

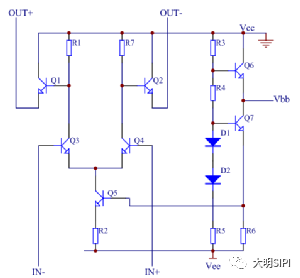

889 差分信號在高速電路設計中的應用越來越廣泛,電路中最關鍵的信號往往都要采用差分結構設計,比如PCIe、Ethernet、USB、HDMI等。

2023-06-14 14:22:39 7901

7901

網絡搜索“什么是高速信號”或“低速信號與高速信號的區別”,出現一堆解釋,例如:

2023-12-01 17:44:41 750

750

電子發燒友網報道(文/周凱揚)隨著每代PCIe單通道速度的翻倍提高,電路板上的PCIe信號覆蓋范圍其實是在減小的,所以現在的服務器都開始用上了PCIe信號增強器。在PCIe 3.0時代,主要用于放大

2023-01-18 01:18:00 5673

5673 電子發燒友網報道(文/周凱揚)隨著每代PCIe單通道速度的翻倍提高,電路板上的PCIe信號覆蓋范圍其實是在減小的,所以現在的服務器都開始用上了PCIe信號增強器。在PCIe 3.0時代,主要用于放大模擬信號的redriver芯片往往就能解決問題,實現更長的線纜長度。

2023-01-29 08:00:00 6169

6169 。PCIe高速采集存儲系統由數據采集模塊、高速數據存儲模塊、GPU實時處理模塊、便攜式工控機等部分組成。可以實現信號的實時采集存儲,并且通過調用Window API的方式實現了比一般方式更快的數據存儲速度。二

2016-03-29 10:53:40

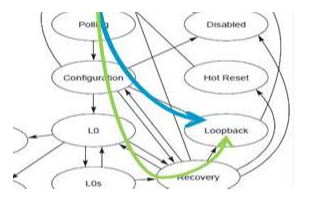

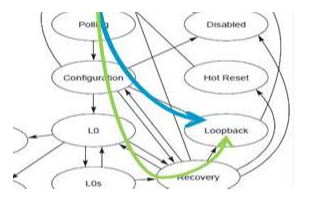

一、接收機測試及環回工作模式(Loopback ) 隨著信號速率的不斷提升,只對高速信號的發送端物理層測試已經不能夠完全反應系統的特性,因此接收機測試也已成為了高速信號的必測項目,尤其是對于

2018-09-26 17:33:30

描述 這款經驗證的參考設計是一款 PCIe Gen-3 高速前端卡設計,旨在擴展 PCIe 子系統的 PCB 線跡距離。該電路板適合安裝在主板與 PCIe Gen3 插卡之間的 x16 通道寬度

2022-09-21 07:43:27

”,簡寫PCIe。2、AC耦合電容:高速差分信號電氣規范要求PCIe發送端串聯一個電容,進行耦合。3、鏈路類型與差分信號數量:X1:1對時鐘差分信號,1對收發差分信號,單面pin數18pi...

2021-11-11 08:05:11

Pericom是一家Fabless芯片設計公司,致力于高速串行互聯芯片設計,產品涵蓋PCIe、USB3.0 、SAS、SATA、XAUI、HDMI。公司成立于1990年,1997年在納斯達克上市

2011-02-22 17:55:54

高速信號的電源完整性分析在電路設計中,設計好一個高質量的高速PCB板,應該從信號完整性(SI——Signal Integrity)和電源完整性 (PI——Power Integrity )兩個方面來

2012-08-02 22:18:58

形式:芯片級系統SOC、板級系統SOB、封裝系統SOP。電子產品的互連有四個層次:芯片內互連、芯片封裝、PCB 及系統級互連。它們正在嚴重地影響著信號、數據和電源的質量。 &

2010-04-21 17:11:35

Agilent Acqiris高速模擬信號平均器可提高oaTOFMS的質量準確度和動態范圍

2019-10-29 07:39:14

查過mini pcie的信號引腳定義,有52個信號(大多引腳無用),X1 LANE 的情況,查看飛思卡爾或INTEL處理器的設計資料,關于這個應用除了主要 的差分收、發和差分時鐘信號之外還需要額外

2017-11-29 11:50:51

伺服驅動器編碼器輸出信號接到ni pcie6351板卡上,怎么用,有那幾個步驟。沒經驗,搞不好。大神前來指點一二。

2018-05-26 16:55:45

UD PCIe-404全國產化信號處理模塊為標準PCIe全高的結構,對外支持PCIe3.0×8通信,也可以采用千兆以太網(RJ45連接器)、萬兆以太網(或RapidIO、Aurora,QSFP+

2023-05-21 18:27:41

標準精心設計, DDR3芯片可以穩定跑到400MHz(FPGA采用-3等級),FPGA與USB3.0芯片以及FPGA跟外部IO之間的PCB連線采用等長設計,有效保證高速信號的可靠傳輸。通過兩個80Pin

2018-10-12 11:38:37

是接收端使用。那么在此想要請教下各位大神,所謂的均衡器技術就是指補償所接收到的信號,如果在這里我的EQ增益過大會不會影響信號輸出的質量,或者是說在特定情況下增益不夠,使用級聯,又因為EQ主要是補償接收

2017-04-11 16:52:03

通過cyu***3014傳輸信號源發出的圖像到pc,圖像為LVDS傳輸,用的max9248,信號源為max9247.只有在pcie轉u***3.0的擴展卡上能正常工作,streamer跑通,速度

2019-04-19 18:14:57

在設計中,通常總是優先處理光口、PCIE等高速信號、或者是音頻等模擬信號。規劃使用最優的層,最優的通道,阻抗、延時、串擾等細節也被優化到極致。然而剩下的低速信號往往不被重視。但是有些低速信號表示自己也是要面子的,你不重視我,我就給你顏色看。

2019-07-31 08:02:19

年,USB 2.0增加了高速(HS)模式,數據傳輸速率達到480 Mbps,并向下兼容低速和全速模式。2008年11月公布的USB 3.0規范支持USB 2.0的所有模式(HS、FS、LS)和全新

2018-12-12 09:51:26

。誤區二:有了仿真軟件平臺就可以做好高速 PCB 設計? EDA 設計軟件平臺集成了高速信號仿真功能,這對于高速 PCB 設計的規則制定與執行,信號質量仿真與評估都有很大的幫助。 但是,在 PCB 實際

2022-04-28 16:21:41

哪里可以做信號完整性測試,信號質量測試,USB2.0測試,3.0測試,眼圖測試等等

2019-11-08 13:28:01

一、PCB設計時高速信號和低速信號區分在高速PCB電路設計過程中,經常會遇到信號完整性問題,導致信號傳輸質量不佳甚至出錯。那么如何區分高速信號和普通信號呢?很多人覺得信號頻率高的就是高速信號,實則

2021-11-11 07:59:58

如何去測量數字傳輸信號的質量?如何保證數字視頻信號的質量?

2021-06-01 06:16:39

解決高速PCB設計信號問題的全新方法

2021-04-25 07:56:35

并不理想。本文將討論如何使用一個多點信號來分配PCIe時鐘,而且仍滿足PCIe第二代規范嚴格的抖動要求。

2019-09-26 07:56:41

一塊帶有PCIE接口的FPGA,一塊PCIE轉USB3.0板卡,想通過FPGA控制PCIE轉USB3.0板卡,實現USB3.0讀入數據,經過FPGA高速處理,不需要經過電腦CPU。請問各位專家:1.

2014-12-25 22:54:58

添加測試點會不會影響高速信號的質量?

2009-09-06 08:40:20

問:添加測試點會不會影響高速信號的質量?答:至于會不會影響信號質量就要看加測試點的方式和信號到底多快而定。基本上外加的測試點(不用線上既有的穿孔(via or DIP pin)當測試點)可能加在

2019-08-30 00:45:16

客戶端量產狀況,成功設計USB 3.0模塊主要有三個要點。保持高速信號的完整性信號的質量關系到數據的傳輸是否完整或U盤的可靠性。根據信號完整性制定出電路板的設計規范及組件的擺放位置,差動傳輸線阻抗控制

2019-05-15 10:56:56

二:有了仿真軟件平臺就可以做好高速 PCB 設計?EDA 設計軟件平臺集成了高速信號仿真功能,這對于高速 PCB 設計的規則制定與執行,信號質量仿真與評估都有很大的幫助。但是,在 PCB 實際

2020-11-30 09:51:58

`產品編號:1501001高性能6U VPX高速信號處理平臺( B-VPX6-6678 )數據手冊( Data Sheet )Version 1.0 清華大學設備儀器廠智能計算研發中心

2016-03-02 13:52:47

`產品編號:1501001高性能6U VPX高速信號處理平臺( B-VPX6-6678 )數據手冊( Data Sheet )Version 1.0 清華大學設備儀器廠智能計算研發中心

2016-03-09 10:12:15

`產品編號:1501001高性能6U VPX高速信號處理平臺( B-VPX6-6678 )數據手冊( Data Sheet )Version 1.0 清華大學設備儀器廠智能計算研發中心

2016-03-16 11:00:00

`產品編號:1501001高性能6U VPX高速信號處理平臺( B-VPX6-6678 )數據手冊( Data Sheet )Version 1.0 清華大學設備儀器廠智能計算研發中心

2016-03-30 11:12:53

`產品編號:1501001高性能6U VPX高速信號處理平臺( B-VPX6-6678 )數據手冊( Data Sheet )Version 1.0 清華大學設備儀器廠智能計算研發中心

2016-04-07 10:40:35

`產品編號:1501001高性能6U VPX高速信號處理平臺( B-VPX6-6678 )數據手冊( Data Sheet )Version 1.0 清華大學設備儀器廠智能計算研發中心

2016-04-14 11:09:20

`產品編號:1501001高性能6U VPX高速信號處理平臺( B-VPX6-6678 )數據手冊( Data Sheet )Version 1.0 清華大學設備儀器廠智能計算研發中心

2016-04-25 11:21:12

產品編號:1501001高性能6U VPX高速信號處理平臺( B-VPX6-6678 )數據手冊( Data Sheet )Version 1.0 清華大學設備儀器廠智能計算研發中心

2016-03-23 11:03:18

高速信號互連設計,精品文章,課程不斷的發布,請大家關注

2022-05-30 11:44:28

PCIe-8034 是一塊4口USB 3.0主控卡,專為工業自動化和機器視覺相關應用設計。USB 3.0或稱作高速USB,是一項新興的總線技術,10倍于USB2.0的傳輸速度,尤其適用于高速數據存儲

2022-04-02 15:46:45

高速電路信號完整性分析與設計—信號完整性仿真:仿真信號仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上

2009-10-06 11:19:50 0

0 焊盤對高速信號的影響

焊盤對高速信號有的影響,它的影響類似器件的封裝對器件的影響上。詳細的分析

2009-03-20 13:48:28 1507

1507 多高的頻率才算高速信號?

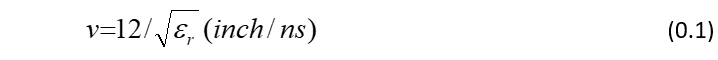

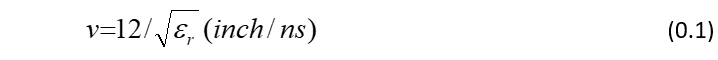

當信號的上升/下降沿時間< 3~6倍信號傳輸時間時,即認為是高速信

2009-04-15 00:41:34 6451

6451 高速信號走線規則教程

隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的關注。高速PCB設計的成功,對EMI

2009-04-15 08:49:27 2798

2798

力科在DesignCon 2010上首家發布PCIe 3.0綜合測試解決方案

第一個支持PCIe 3.0的高性能通訊發生器和練習器 Summit Z3-16 Exerciser同步2臺WaveMaster 8 Zi 在4通道上同時提供30GHz帶

2010-02-08 16:13:37 612

612 什么是鏈路質量和信號強度 術語名稱:鏈路質量和信號強度

術語解釋:信號強度是無線適配器接收到的信號的強度,

2010-02-24 10:30:34 3380

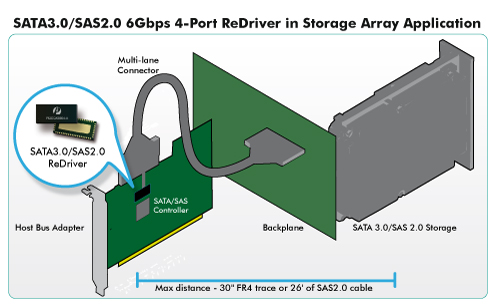

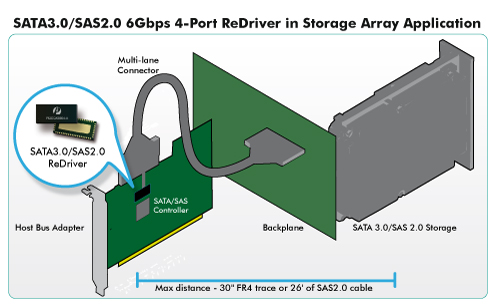

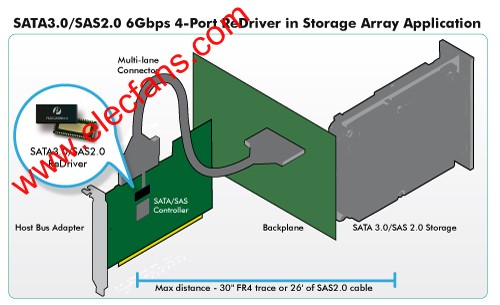

3380 Pericom發布業界第一條極低功耗SATA3/SAS2信號處理產品線

業界最小的單端口和四端口ReDriver產品線,以高成長的服務器、儲存和筆記型計算機為目標市場

美國加州舊

2010-11-16 10:35:41 1085

1085

Pericom發布業界第一條極低功耗SATA3/SAS2信號處理產品線業界最小的單端口和四端口ReDriver產品線,以高成長的服務器、儲存和筆記型計算機為目標市場

2010-11-16 10:36:55 861

861 Pericom Semiconductor Corporation日前宣布:推出一條包括三款全新的SATA3.0和SAS2.0 6Gbps ReDriver的信號處理產品系列,其中包括業界最小單端口和四端口ReDriver產品。此外,這三款低耗

2010-11-18 09:07:40 1324

1324

Pericom Semiconductor Corporation日前宣布:推出面向PCI Express (PCIe) 3.0的 ReDriver信號調節(signal conditioner)、信號交換(signal swit

2010-11-22 08:50:03 1120

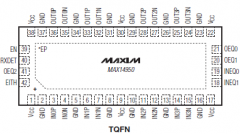

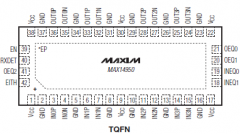

1120 maxim推出MAX14950超小尺寸均衡器/接收器,有效改善Gen 3.0應用中的PCIe信號完整性。

2011-01-15 08:56:06 968

968

百利通半導體公司(Pericom Semiconductor,納斯達克股票市場代碼:PSEM)日前宣布:其最新一代的USB 3.0、DP(Display Port)1.2和PCle 3.0產品系列將使最新CPU芯片組實現采用更高速串行協議的串行連接

2011-09-14 14:20:27 886

886 百利通半導體公司(Pericom )宣布其最新一代的USB3.0、DP(Display Port)1.2和PCle3.0產品系列將使最新CPU芯片組實現采用更高速串行協議的串行連接。

2011-09-17 12:03:46 2283

2283 百利通半導體公司(Pericom,納斯達克股票市場代碼:PSEM)今日宣布:公司產量持續攀升,并擴展了能夠支持最新一代英特爾平臺的USB3.0、DisplayPortTM(DP)1.2及PCI Express? (PCIe?) 3.0產品系列。

2012-04-11 15:46:29 1050

1050

因為PCIE 3.0信號的速率可以達到8Gb/s,而且鏈路通道走線也可能會很長,這可能會導致高速信號衰減過大,在接收端無法得到張開的眼圖。因此在PCIE 3.0的Tx和Rx端均使用了均衡設置,以補

2012-12-10 10:51:01 41

41 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)今天宣布推出全新用于PCIe 3.0的SpeedBridge? Adapter。它為設計師們提供了一個重要的工具,來驗證和確認他們的PCI Express (PCIe) 設計。

2013-07-30 18:35:06 2659

2659 ,正式推出業界首個 16 通道的 PCI Express? 3.0 信號調理重定時器。IDT 全新的 EyeBoost? 重定時器針對計算、存儲和通信應用中的長距離或嘈雜連接來恢復信號質量,從而

2013-09-26 17:06:02 1230

1230 領先的串行高速轉換、連接、信號完整性和時頻解決方案供應商百利通(Pericom)半導體公司日前宣布:Pericom將為包括筆記本電腦、智能手機和平板電腦等下一代移動設備,面向云計算的先進存儲和服務

2015-09-01 10:01:53 880

880 安立公司發布了高速串行總線接收器測試解決方案,該解決方案使用其信號質量分析儀MP1800A系列以及Granite River Labs(GRL)開發的GRL-PCIE4-BASE-RXA 校準/接收器測試軟件。

2015-12-23 17:45:15 2245

2245 PCIE 3.0中使用動態均衡方法能夠針對不同的情形自動配置并優化發送端和接收端的均衡設置,補償信號的傳輸通道對高速信號帶來的影響(如損耗),以在接收端獲得最好的信號質量。 但是動態均衡優化過程需要花費時間,有時候可能會導致系統工作或運行超時等錯誤。

2018-01-31 09:09:32 10138

10138

該信號為全局復位信號,由處理器系統提供(RC),處理器系統需要為PCIe插槽和PCIe設備提供該復位信號。PCIe設備使用該信號復位內部邏輯。當該信號有效時,PCIe設備將進行復位操作。

2018-12-22 14:45:41 22377

22377 在高速PCB電路設計過程中,經常會遇到信號完整性問題,導致信號傳輸質量不佳甚至出錯。

2019-12-10 17:25:23 1655

1655 在高速PCB設計中,“信號”始終是工程師無法繞開的一個知識點。不管是在設計環節,還是在測試環節,信號質量都值得關注。在本文中,我們主要來了解下影響信號質量的5大問題。

2019-10-10 17:21:31 5023

5023 本文主要分析一下在高速PCB設計中,高速信號與高速PCB設計存在一些理解誤區。 誤區一:GHz速率以上的信號才算高速信號? 提到高速信號,就需要先明確什么是高速,MHz速率級別的信號算高速、還是

2019-11-05 11:27:17 10310

10310

來源:羅姆半導體社區 提到“高速信號”,就需要先明確什么是“高速”,MHz速率級別的信號算高速、還是GHz速率級別的信號算高速? 傳統的SI理論對于“高速信號”有經典的定義。SI:Signal

2022-12-12 16:56:35 6009

6009 在高速PCB設計中,“信號”始終是工程師無法繞開的一個知識點。不管是在設計環節,還是在測試環節,信號質量都值得關注。

2020-11-20 10:55:07 3418

3418 在介紹信號的完整性分析方法在設計高速信號電路的作用前,首先必須明確兩個概念,一是何為高速信號,二是何為信號的完整性分析。一提到高速信號,大家一定會想到頻率高的信號即為高速信號,其實不然,對于數字信號

2020-12-22 08:00:00 5

5 在高速PCB設計中,“信號”始終是工程師無法繞開的一個知識點。不管是在設計環節,還是在測試環節,信號質量都值得關注。在本文中,我們主要來了解下影響信號質量的5大問題。 根據目前工作的結論,信號質量

2020-12-22 16:34:40 1472

1472

在高速PCB設計中,“信號”始終是工程師無法繞開的一個知識點。不管是在設計環節,還是在測試環節,信號質量都值得關注。在本文中,我們主要來了解下影響信號質量的5大問題。根據目前工作的結論,信號質量常見的問題主要表現在五個方面:過沖,回沖,毛刺,邊沿,電平

2020-12-24 18:20:46 840

840 高速信號鏈選擇指南

2021-04-24 12:19:08 14

14 據外媒 techpowerup 消息,美國芯片制造商Microchip發布了全球首款 PCIe 5.0 交換芯片:Switchtec PFX PCIe 5.0 系列。

2022-01-04 15:13:04 2552

2552 在高速PCB電路設計過程中,經常會遇到信號完整性問題,導致信號傳輸質量不佳甚至出錯。那么如何區分高速信號和普通信號呢?

2022-02-09 10:02:28 4

4 然而,高速電路是什么,什么信號才屬于高速信號?這是筆者曾在一次面試中被問到過的一個問題,當時腦袋中迅速閃過圖像數據處理、音頻處理等設計,但是如何定義所謂的“高速”卻一下子想不出來如何定義這個基本概念。

2022-06-24 11:16:50 6006

6006 PCIe 7.0 接口將繼續使用 1b/1b flit 模式編碼和隨 PCIe 6.0 引入的 PAM4 信號技術,這與PCIe 3.0 到PCIe 5.0 規范中使用的 128b/130b 編碼

2022-07-28 15:11:54 925

925 本文結合實際測試中遇到的時鐘信號回溝問題介紹了高速信號的概念,進一步闡述了高速信號與高頻信號的區別,分析了25MHz時鐘信號沿上的回溝等細節的測試準確度問題,并給出了高速信號測試時合理選擇示波器的一些建議。

2022-09-14 09:20:17 3153

3153 PCIE3.0協議分析儀U4301A,它是一塊采用了Agilent AXIe架構的插卡,可以插在AXIe的機箱里,通過探頭來捕獲高速的PCIE 3.0信號,并通過外部PC控制顯示協議分析的結果。

2022-10-12 17:33:56 1191

1191 PCIe標準自從推出以來,1代和2代標準已經在PC和Server上逐漸普及,用于滿足高速顯卡、高速存儲設備對于高速數據傳輸的要求。出于支持更高總線數據吞吐率的目的,PCI-SIG組織在2010年制定了PCIe 3.0,即PCIe 3代的規范,數據速率達到8Gbps。

2022-10-20 09:59:21 4792

4792 隨著高速串行信號的數據速率的越來越高,如PCIE6.0的數據速率已經達到64GT/s,USB4.0 V2的信號速率已經達到80Gb/s。高速信號的趨膚效應和傳輸線的介質損耗,使高速信號在傳輸

2023-06-07 17:27:02 832

832

電子發燒友網站提供《GEN3通道中的Pericom PCIe重新驅動程序/中繼器兼容性.pdf》資料免費下載

2023-07-24 09:50:50 0

0 電子發燒友網站提供《使用Pericom交換機連接LVDS信號.pdf》資料免費下載

2023-07-26 09:17:24 0

0 電子發燒友網站提供《使用Pericom視頻交換機接口視頻信號.pdf》資料免費下載

2023-07-26 15:31:11 0

0 采集模式,系統實現了效率的檢測。其中的挑戰在于觸發信號源來自編碼器的CO輸出,但每100個周期僅觸發一次。 ? 解決方案 硬件: 簡儀科技選擇了PCIe-69834高速采集卡和PCIe-5211 計數器卡,以滿足復雜的觸發需求。通過利用PCIe-5211計數

2023-09-04 09:50:55 370

370 今天給大家分享的是:高速信號、14條高速信號布局設計規則。

2023-09-07 09:19:57 454

454

1個PCIe X4連接器電口,接插件為molex接口,在使用中可支持光纖傳輸。1個PCIe X8 標準接口,支持V2.0,V3.0規范,1個千兆網絡。

2024-01-09 11:07:59 216

216

基于“眼圖”概念。眼圖是一種信號波形的圖形表示方法,由連續傳輸的數字信號構成。當高速信號被傳輸時,信號會受到各種噪聲、失真和干擾的影響。通過繪制眼圖可以觀察信號的質量和穩定性,進而判斷信號是否能被正確解讀。 在高速信號眼圖測

2024-02-01 16:19:49 142

142

電子發燒友App

電子發燒友App

評論