日本產(chǎn)業(yè)技術(shù)綜合研究所 (AIST)與東京都立大學(xué)聯(lián)合宣布,已經(jīng)成功在二硫化鉬 (MoS2) 上形成了層狀材料三碲化二銻 (Sb2Te3),并 制造的 n 型 MoS2晶體管具有足夠的耐熱性以承受半導(dǎo)體制造過(guò)程。

一種稱(chēng)為過(guò)渡金屬二硫化物(TMDC)的材料具有二維晶體結(jié)構(gòu),作為下一代晶體管溝道的半導(dǎo)體材料受到關(guān)注,因?yàn)樗词乖?1 納米或更小的原子層區(qū)域也能保持高導(dǎo)電性。然而,公共金屬電極與MoS2界面之間的高接觸電阻阻礙了晶體管性能的提升。

AIST正在參與日本科學(xué)技術(shù)廳的戰(zhàn)略基礎(chǔ)研究促進(jìn)計(jì)劃(CREST)“原子層異質(zhì)結(jié)構(gòu)器件的演示和3D集成LSI的原子層沉積工藝的開(kāi)發(fā)(2017-2021財(cái)年):Metropolitan I一直在研究與大學(xué)的聯(lián)合項(xiàng)目中的高性能 TMDC 晶體管。

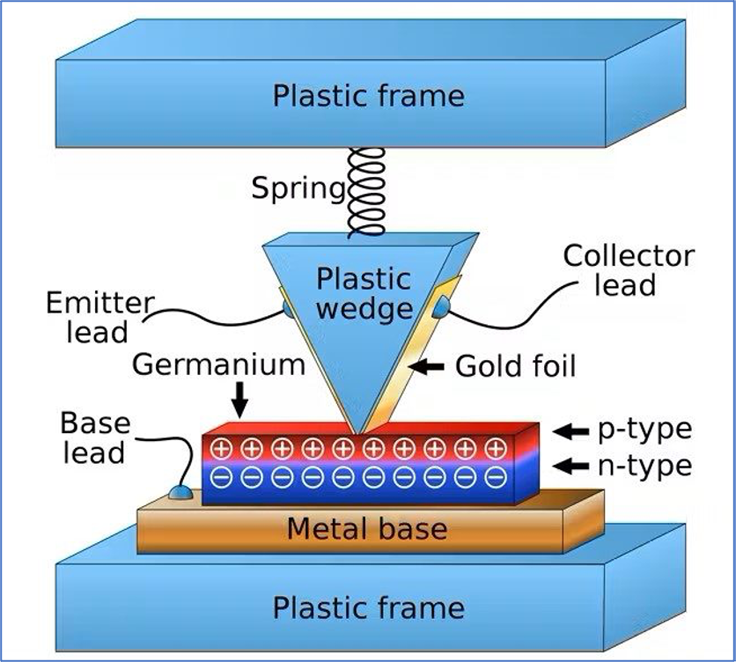

這一次,研究小組使用 MoS2制造了晶體管,并專(zhuān)注于將Sb2Te3作為其接觸材料。Sb2Te3有很多原子層,原子層通過(guò)稱(chēng)為范德華力的弱鍵結(jié)合在一起。它還表現(xiàn)出類(lèi)似于半金屬的特性(帶隙為 0.2 至 0.3 eV),并且具有約 620°C 的高熔點(diǎn)。

這些特征表明在Sb2Te3和MoS2之間可能形成范德華界面以抑制費(fèi)米能級(jí)釘扎(FLP)現(xiàn)象。因此,確定通過(guò)使用Sb2Te3,可以同時(shí)實(shí)現(xiàn)高耐熱性和低接觸電阻。

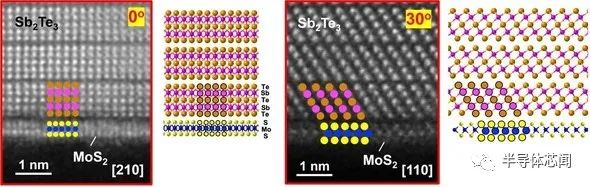

因此,這一次,使用濺射法在單層MoS2上形成Sb2Te3膜。然后,通過(guò)透射電子顯微鏡(TEM)確認(rèn)在Sb2Te3/MoS2接觸界面處形成了范德華界面。

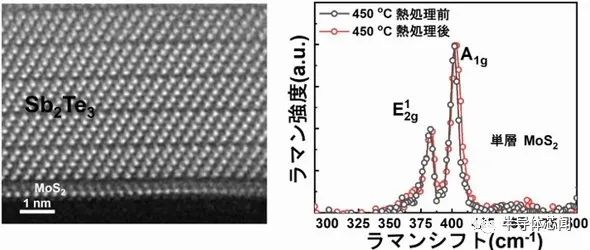

還研究了Sb2Te3/MoS2層壓膜結(jié)構(gòu)的耐熱性。拉曼光譜分析證實(shí),MoS2單層結(jié)構(gòu)在熱處理前后均保持不變。還證實(shí),即使在 450°C 的熱處理后,Sb2Te3/MoS2層壓膜結(jié)構(gòu)也保持良好的結(jié)晶度和范德華界面。

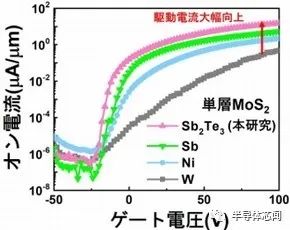

該研究小組還研究了Sb2Te3/MoS2范德瓦爾斯界面形成對(duì)晶體管特性的影響。結(jié)果發(fā)現(xiàn),具有Sb2Te3電極的晶體管的驅(qū)動(dòng)電流比使用Sb、Ni、W等作為接觸材料時(shí)高4至30倍。事實(shí)上,當(dāng)測(cè)量MoS2晶體管的接觸電阻時(shí),使用Sb2Te3電極的晶體管的接觸電阻值比使用Sb電極的晶體管低約一個(gè)數(shù)量級(jí)。

未來(lái),課題組將致力于p型TMDC晶體管的低接觸電阻技術(shù)開(kāi)發(fā),旨在通過(guò)串聯(lián)n型和p型TMDC晶體管來(lái)制造CMOS。

臺(tái)積電將帶來(lái)全球第一個(gè)2D納米片晶體管

臺(tái)積電工程師與臺(tái)灣兩所大學(xué)合作,將在今年的國(guó)際電子器件會(huì)議 (IEDM) 上報(bào)告世界上第一個(gè)由二維半導(dǎo)體材料制成的納米片柵環(huán)晶體管。

硅納米片晶體管或又名納米帶提供改進(jìn)的靜電控制和相對(duì)較高的驅(qū)動(dòng)電流,并在 3nm 制造工藝中實(shí)施。

根據(jù)即將推出的 IEDM 計(jì)劃的亮點(diǎn),臺(tái)積電已經(jīng)展示了在納米片晶體管中使用過(guò)渡金屬二硫?qū)倩飭螌幼鳛榘雽?dǎo)體通道的可能性。在這種情況下,它是二硫化鉬。

與硅和自旋軌道耦合相比,這種二維材料可以具有增強(qiáng)的電子遷移率,從而產(chǎn)生自旋電子計(jì)算的可能性。

柵極寬度為 40nm 的晶體管在 1V 的 Vds 下產(chǎn)生每微米 410 微安的驅(qū)動(dòng)電流。期望通過(guò)堆疊設(shè)備來(lái)增加驅(qū)動(dòng)電流。

臺(tái)積電領(lǐng)導(dǎo)的團(tuán)隊(duì)將報(bào)告制造此類(lèi)晶體管的集成流程,但優(yōu)化性能仍有待完成。

TSMC 論文#34.5首次展示 GAA 單層 MoS2 納米片 nFET……是第 68 屆年度 IEDM 的亮點(diǎn)之一。

在論文 #7.4 中,在 EOT 為 1 nm 的單層 MoS2 頂柵 nFET 中接近理想的亞閾值擺動(dòng)中,臺(tái)積電領(lǐng)導(dǎo)的團(tuán)隊(duì)描述了鉿基電介質(zhì)與 MoS2 的集成,以構(gòu)建頂柵 nFET 創(chuàng)建可堆疊系統(tǒng). 亞閾值電壓擺幅小于70mV/dec。這表明當(dāng)晶體管關(guān)閉時(shí)泄漏電流較低。

1納米以下制程重大突破!臺(tái)積電官宣「鉍」密武器

IBM 剛剛官宣研發(fā)2nm芯片不久,臺(tái)積電再次發(fā)起了挑戰(zhàn)!?臺(tái)積電取得1nm以下制程重大突破,不斷地挑戰(zhàn)著物理極限。?近日,臺(tái)大與臺(tái)積電、美國(guó)麻省理工學(xué)院合作研究發(fā)現(xiàn)二維材料結(jié)合「半金屬鉍(Bi)」能達(dá)極低電阻,接近量子極限。?這項(xiàng)研究成果由臺(tái)大電機(jī)系暨光電所教授吳志毅,與臺(tái)灣積體電路和MIT研究團(tuán)隊(duì)共同完成,已在國(guó)際期刊Nature上發(fā)表,有助實(shí)現(xiàn)半導(dǎo)體1nm以下制程挑戰(zhàn)。?

半導(dǎo)體新材料「鉍」:有望突破「摩爾定律」極限

目前半導(dǎo)體主流制程進(jìn)展到5nm和3nm節(jié)點(diǎn)。?晶片單位面積能容納的電晶體數(shù)目,已將逼近半導(dǎo)體主流材料「硅」的物理極限,晶片效能也無(wú)法再逐年顯著提升。?近年科學(xué)界積極尋找能取代硅的二維材料,挑戰(zhàn)1nm以下的制程,卻苦于無(wú)法解決二維材料高電阻及低電流等問(wèn)題。?臺(tái)大、臺(tái)積電和MIT自2019年展開(kāi)了長(zhǎng)達(dá)1年半的跨國(guó)合作,終于找到了這把key。?

這個(gè)重大突破先由MIT團(tuán)隊(duì)發(fā)現(xiàn)在「二維材料」上搭配「半金屬鉍(Bi)」的電極,能大幅降低電阻并提高傳輸電流。?臺(tái)積電技術(shù)研究部門(mén)則將「鉍(Bi)沉積制程」進(jìn)行優(yōu)化,最后臺(tái)大團(tuán)隊(duì)運(yùn)用「氦離子束微影系統(tǒng)」將元件通道成功縮小至納米尺寸,終于獲得突破性的研究成果。?吳志毅教授說(shuō)明,在使用「鉍(Bi)」為「接觸電極」的關(guān)鍵結(jié)構(gòu)后,二維材料電晶體的效能,不但與「硅基半導(dǎo)體」相當(dāng),又有潛力與目前主流的硅基制程技術(shù)相容,有助于未來(lái)突破「摩爾定律」極限。?

研究成果能替下世代晶片,提供省電、高速等絕佳條件,未來(lái)可望投入人工智能、電動(dòng)車(chē)、疾病預(yù)測(cè)等新興科技應(yīng)用。?

臺(tái)積電走向2nm!預(yù)計(jì)2024年實(shí)現(xiàn)量產(chǎn)

幾十年來(lái),半導(dǎo)體行業(yè)進(jìn)步的背后存在著一條金科玉律,即摩爾定律。?摩爾定律表明:每隔 18~24 個(gè)月,集成電路上可容納的元器件數(shù)目便會(huì)增加一倍,芯片的性能也會(huì)隨之翻一番。?

然而,在摩爾定律放緩甚至失效的今天,全球幾大半導(dǎo)體公司依舊在拼命「廝殺」,希望率先拿下制造工藝布局的制高點(diǎn)。?臺(tái)積電在先進(jìn)制程方面可謂是一騎絕塵。3nm領(lǐng)域,臺(tái)積電一只獨(dú)秀。2020年,5nm量產(chǎn)。2nm預(yù)計(jì)在2023至2024推出。?此前報(bào)道曾介紹了臺(tái)積電近年來(lái)整個(gè)先進(jìn)制程的布局:?

要知道,臺(tái)積電、英特爾和三星并稱(chēng)半導(dǎo)體制造業(yè)「三巨頭」。在芯片制程逐漸縮小的路上,三大巨頭你追我趕。?

現(xiàn)在半路又殺出了IBM,上周竟宣布自己研發(fā)出了世界首個(gè)2nm芯片,相當(dāng)于在指甲大小的芯片上容納多達(dá)500億個(gè)晶體管,速度更快并且更高效。?

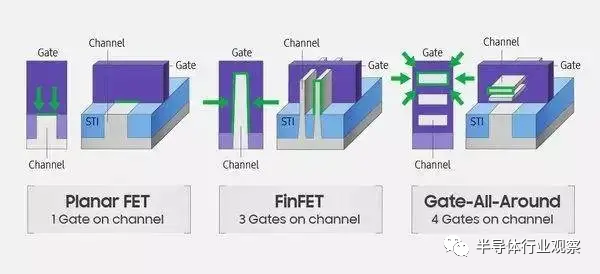

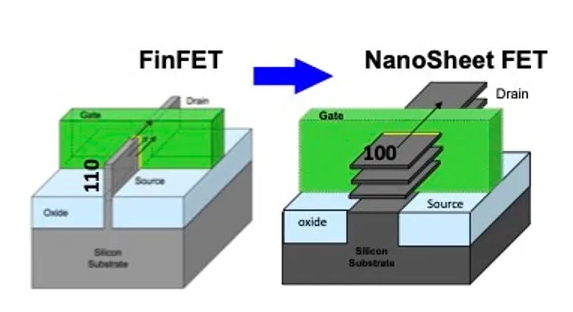

對(duì)與更先進(jìn)的2nm制程,臺(tái)積電早在2019年就宣布對(duì)此研發(fā)。?去年,在5nm量產(chǎn)不久后,臺(tái)積電宣布2nm制程取得重大突破——切入環(huán)繞式柵極技術(shù)?(gate-all-around,簡(jiǎn)稱(chēng) GAA) 技術(shù)。?有別于3nm與5nm采用鰭式場(chǎng)效晶體管(FinFET)架構(gòu)。FinFET 本身的尺寸已經(jīng)縮小至極限后,無(wú)論是鰭片距離、短溝道效應(yīng)、還是漏電和材料極限也使得晶體管制造變得岌岌可危,甚至物理結(jié)構(gòu)都無(wú)法完成。?

而全環(huán)繞柵(GAA)是FinFET技術(shù)的演進(jìn), 溝道由納米線(nanowire)構(gòu)成,其四面都被柵極圍繞,從而再度增強(qiáng)柵極對(duì)溝道的控制能力,有效減少漏電。?臺(tái)積電在2nm研發(fā)上切入全環(huán)柵場(chǎng)效應(yīng)晶體管GAA,其競(jìng)爭(zhēng)對(duì)手三星則早在2年前其揭露3nm技術(shù)工藝時(shí),就宣布從FinFET轉(zhuǎn)向GAA,并「大放厥詞」:2030年要超過(guò)臺(tái)積電,取得全球芯片代工龍頭地位。?

這也算是為兩家企業(yè)2-3nm制程的市場(chǎng)之戰(zhàn)吹響了號(hào)角。?為了搶在臺(tái)積電之前完成3nm的研發(fā),三星的芯片制造工藝由5nm直接上升到3nm,4nm則直接跳過(guò)。?盡管臺(tái)積電和三星在2nm-3nm市場(chǎng)你爭(zhēng)我?jiàn)Z,但是英特爾卻毫不在乎,依然堅(jiān)持在14nm,10nm制程上的研發(fā)。?臺(tái)積電,三星對(duì)最先進(jìn)制程的追趕,正是想要在世界先進(jìn)制程領(lǐng)域一決高下。

臺(tái)積電加入美半導(dǎo)體聯(lián)盟

與此同時(shí),出于利益考慮,全球晶圓代工第一大廠、島內(nèi)企業(yè)臺(tái)積電還積極尋求在美建廠,努力之一就是加入了剛剛成立的「美國(guó)半導(dǎo)體聯(lián)盟」。?本周二,由美國(guó)科技公司主導(dǎo)的游說(shuō)團(tuán)體「美國(guó)半導(dǎo)體聯(lián)盟」(Semiconductors in American Coalition,SIAC)成立。?

SIAC成員目前包括蘋(píng)果、谷歌、微軟和英特爾,除了這些美國(guó)主導(dǎo)科技企業(yè)外,還包括三星、海力士,還有***巨頭ASML,更有島內(nèi)晶圓代工大廠臺(tái)積電和聯(lián)發(fā)科。?對(duì)于加入SIAC的消息,臺(tái)積電沒(méi)有做出具體回應(yīng)。?

SAIC官網(wǎng)「成員」頁(yè)可以看到臺(tái)積電在列?這些成員任何一家的限制都會(huì)給我們的發(fā)展帶來(lái)阻擋。?專(zhuān)家解讀,可能讓中國(guó)更難達(dá)成不依賴(lài)美國(guó)技術(shù)、半導(dǎo)體自給自足的目標(biāo)。SIAC的當(dāng)務(wù)之急是敦促美國(guó)政府提供「補(bǔ)助」。

一個(gè)由美國(guó)兩黨參議員組成的小組在周五公布了一項(xiàng)「520億美元」的提案,以在5年內(nèi)大幅提高美國(guó)半導(dǎo)體芯片生產(chǎn)和研究水平。?美參議員Mark Kelly等人一直在討論一項(xiàng)折中的方案,以「應(yīng)對(duì)中國(guó)半導(dǎo)體產(chǎn)量的上升,以及芯片短缺對(duì)汽車(chē)制造和其他美國(guó)產(chǎn)業(yè)的影響」。這項(xiàng)提案預(yù)計(jì)將被納入?yún)⒆h院下周討論的關(guān)于資助美國(guó)基礎(chǔ)和先進(jìn)技術(shù)研究的法案中。?除了這項(xiàng)520億美元的提案,據(jù)美國(guó)《國(guó)會(huì)山報(bào)》報(bào)道,當(dāng)?shù)貢r(shí)間5月12日,美國(guó)參議院商務(wù)、科學(xué)和運(yùn)輸委員會(huì)以24:4的結(jié)果投票通過(guò)「無(wú)盡前沿」法案,授權(quán)在五年內(nèi)撥款「1100億美元」用于科技研究。?

「無(wú)盡前沿」法案將授權(quán)五年內(nèi)將其中1000億美元投資基礎(chǔ)和先進(jìn)科技研究、商業(yè)化、教育和培訓(xùn)項(xiàng)目,其中包括人工智能、半導(dǎo)體、量子計(jì)算、先進(jìn)通信、生物技術(shù)和先進(jìn)能源。?此外,法案還包括再撥款「100億美元」,設(shè)立至少十個(gè)區(qū)域技術(shù)中心,并創(chuàng)建一個(gè)供應(yīng)鏈危機(jī)應(yīng)對(duì)計(jì)劃,來(lái)解決殃及汽車(chē)生產(chǎn)的「半導(dǎo)體芯片缺口」等問(wèn)題。Hinrich基金會(huì)研究員、新加坡國(guó)立大學(xué)講師亞歷克斯·卡普里指出,因?yàn)槊绹?guó)正大力將半導(dǎo)體價(jià)值鏈與技術(shù)轉(zhuǎn)移回美國(guó),并設(shè)下保護(hù)網(wǎng),這讓「中國(guó)大陸提升芯片產(chǎn)業(yè)的努力,將更具挑戰(zhàn)性」。?卡普里認(rèn)為,臺(tái)積電大幅度增加對(duì)美投資,并參與在美國(guó)建立領(lǐng)先的5納米甚至3納米芯片制造工廠,可能會(huì)給中國(guó)大陸帶來(lái)壓力,因?yàn)榕_(tái)積電顯然不會(huì)在大陸蓋這類(lèi)工廠。?臺(tái)積電上月證實(shí)曾投資29億美元擴(kuò)大在南京的工廠,但該工廠的技術(shù)是28nm制程,比臺(tái)積電在美國(guó)亞利桑那州晶圓廠所使用的技術(shù)還要落后兩至三代。?

Intralink電子和嵌入軟件部門(mén)主管蘭道爾說(shuō),臺(tái)積電與其他加入SIAC的公司一樣,是出于自身利益的考量,有機(jī)會(huì)瓜分美國(guó)政府的500億美元資金。?同時(shí),他表示,中國(guó)沒(méi)有類(lèi)似集結(jié)全球各地公司的組織,而且組隊(duì)結(jié)盟有助美國(guó)與其盟友「長(zhǎng)期保有領(lǐng)先中國(guó)的優(yōu)勢(shì)地位。」?

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論