數(shù)字電路如何實現(xiàn)倍頻?? 數(shù)字電路是由數(shù)字電子器件以及邏輯門電路組成,可以用于處理數(shù)字信號或數(shù)字數(shù)據(jù)。其中最基本的電子器件有晶體管、二極管等,而邏輯門電路包括了與門、或門、非門、異或門等。在數(shù)字電路

2023-09-18 10:37:43 465

465 為什么說數(shù)字電路無法取代模擬電路 數(shù)字電路和模擬電路是兩種不同的電路體系,它們各有優(yōu)劣。數(shù)字電路是基于數(shù)字信號的處理方式,可以實現(xiàn)復(fù)雜的邏輯運算和控制功能,而模擬電路則是利用連續(xù)信號來實現(xiàn)電路功能

2023-08-27 15:37:05 392

392 數(shù)字電路是現(xiàn)代電子技術(shù)中的重要組成部分,它是由數(shù)字信號進行處理和傳輸?shù)?b style="color: red">電路系統(tǒng)。數(shù)字電路的定義是指由邏輯門和觸發(fā)器等基本邏輯元件組成的電路,用于處理和傳輸數(shù)字信號。數(shù)字電路通過將輸入信號轉(zhuǎn)換為離散

2023-07-31 11:46:22 774

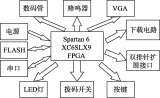

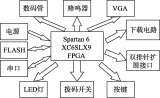

774 大俠好,歡迎來到FPGA技術(shù)江湖。本系列將帶來FPGA的系統(tǒng)性學(xué)習(xí),從最基本的數(shù)字電路基礎(chǔ)開始,最詳細操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業(yè)學(xué)生、初入職場小白及打算進階提升的職業(yè)開發(fā)者都可以有系統(tǒng)性學(xué)習(xí)的機會。

2023-05-11 11:48:00 285

285

用數(shù)字信號完成對數(shù)字量進行算術(shù)運算和邏輯運算的電路稱為數(shù)字電路或數(shù)字系 統(tǒng)。由于它具有邏輯運算和邏輯處理的功能,所以又稱數(shù)字邏輯電路。現(xiàn)代的數(shù)字電路是由半導(dǎo)體工藝制成的若干數(shù)字集成器件構(gòu)造而成

2023-03-24 10:36:00 676

676

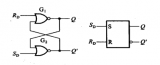

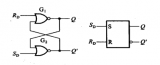

用數(shù)字信號完成對數(shù)字量進行邏輯運算和算術(shù)運算的電路稱為數(shù)字電路。 由于它具有邏輯運算和邏輯處理功能,所以又稱為數(shù)字邏輯電路。 現(xiàn)代的數(shù)字電路由半導(dǎo)體工藝制成的數(shù)字集成器件構(gòu)造而成。 邏輯門是數(shù)字電路的基本單元電路,就如同在模擬電路中基本放大電路是模擬電路的基本單元電路。

2023-02-23 14:18:32 10072

10072

數(shù)字電路設(shè)計是數(shù)字電路最為關(guān)鍵及重要的一步,今天我們將從各個流程為大家介紹完整的數(shù)字電路設(shè)計!

2022-07-10 17:14:16 5368

5368 數(shù)字電路基礎(chǔ)

2022-03-21 15:12:36 78

78 本帖最后由 gk320830 于 2015-3-7 06:25 編輯

數(shù)字電路 現(xiàn)代的數(shù)字電路由半導(dǎo)體工藝制成的若干數(shù)字集成器件構(gòu)造而成。邏輯門是數(shù)字邏輯電路的基本單元。存儲器是用來存儲二值

2009-04-06 23:45:00

直接說正題,幫助一下剛剛?cè)腴T的朋友們,也算是學(xué)習(xí)IC設(shè)計的一個總結(jié)吧。 一、首先要知道自己在干什么? 數(shù)字電路(fpga/asic)設(shè)計就是邏輯電路的實現(xiàn),這樣子說太窄了,因為asic還有不少是模擬

2021-11-06 11:36:01 18

18 FPGA CPLD數(shù)字電路設(shè)計經(jīng)驗分享.(電源技術(shù)發(fā)展怎么樣)-FPGA CPLD數(shù)字電路設(shè)計經(jīng)驗分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

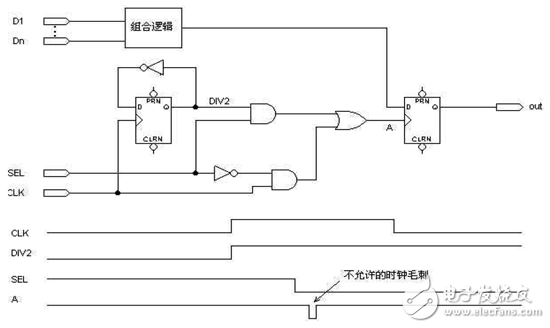

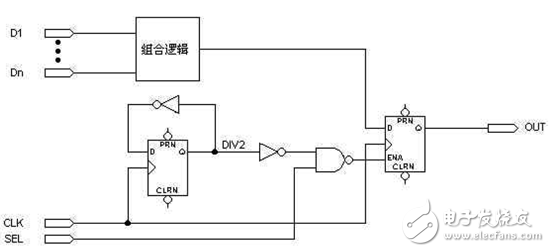

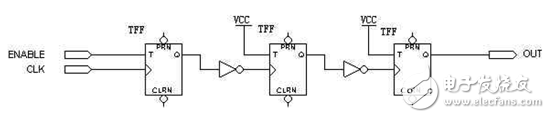

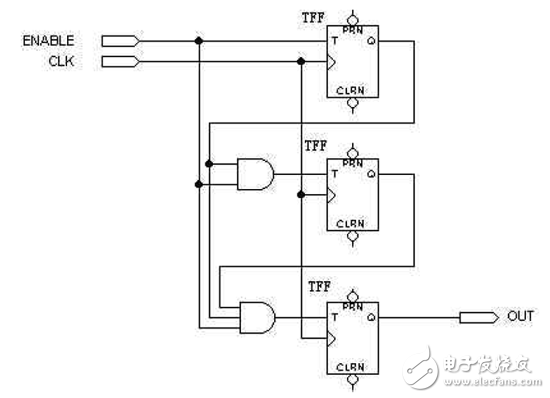

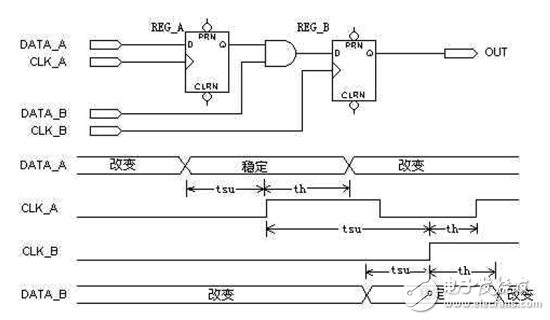

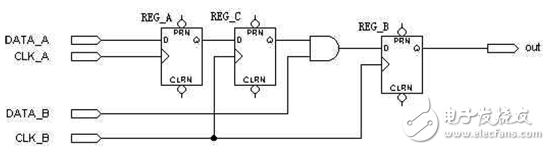

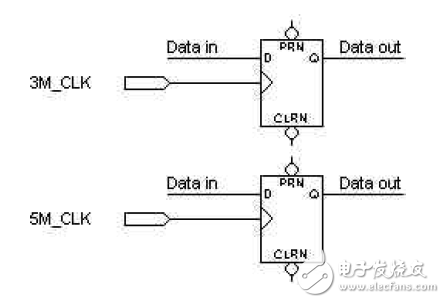

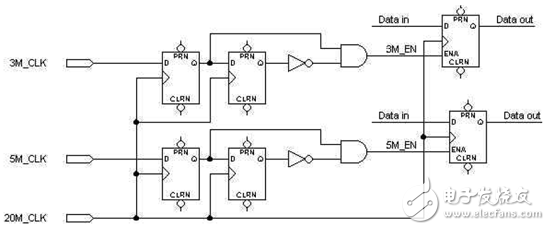

51 在數(shù)字電路的設(shè)計中,時序設(shè)計是一個系統(tǒng)性能的主要標志,在高層次設(shè)計方法中,對時序控制的抽象度也相應(yīng)提高,因此在設(shè)計中較難把握,但在理解RTL電路時序模型的基礎(chǔ)上,采用合理的設(shè)計方法在設(shè)計復(fù)雜數(shù)字系統(tǒng)

2021-01-20 14:26:03 14

14 為什么要學(xué)數(shù)字電路篇:數(shù)字電路是FPGA的敲門磚、墊腳石,為什么這樣說呢,因為數(shù)字電路主要的內(nèi)容就是邏輯和時序,而邏輯與時序就是FPGA設(shè)計的核心。邏輯無非就是與門或門、非門……,時序無非就是鎖存器

2020-12-23 16:47:38 43

43 數(shù)字電路作為一門專業(yè)基礎(chǔ)課,除了介紹數(shù)字電路的理論知識外,更需要通過配套的實驗平臺將理論知識和實踐環(huán)節(jié)相結(jié)合,培養(yǎng)學(xué)生的動手能力和實踐創(chuàng)新能力。

2020-08-16 12:03:45 5879

5879

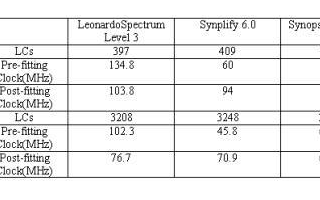

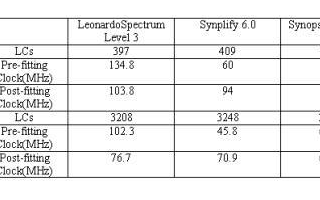

在使用FPGA做數(shù)字電路設(shè)計的流程中,綜合是其中非常重要的一個步驟。同樣的設(shè)計源代碼,無論是VHDL或Verilog HDL,采用不同的綜合工具綜合會產(chǎn)生不同的結(jié)果。

2020-07-24 15:47:00 1715

1715

雖然在FPGA中,利用綜合工具來可以將VHDL或者Verilog代碼轉(zhuǎn)化成電路。但是作為FPGA工程師而言,在沒有綜合工具的情況下,如何設(shè)計出數(shù)字電路呢?如果已經(jīng)知道需要實現(xiàn)的功能的狀態(tài)機,如何將它轉(zhuǎn)化成數(shù)字電路呢?和設(shè)計出數(shù)字電路呢?

2020-06-17 16:33:38 2736

2736 可編程邏輯器件PLD(Programmable Logic De-vice)是一種數(shù)字電路,它可以由用戶來進行編程和進行配置,利用它可以解決不同的邏輯設(shè)計問題。

2020-04-28 11:18:49 2112

2112 FPGA/CPLD能完成任何數(shù)字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現(xiàn)。

2020-01-20 09:29:00 2981

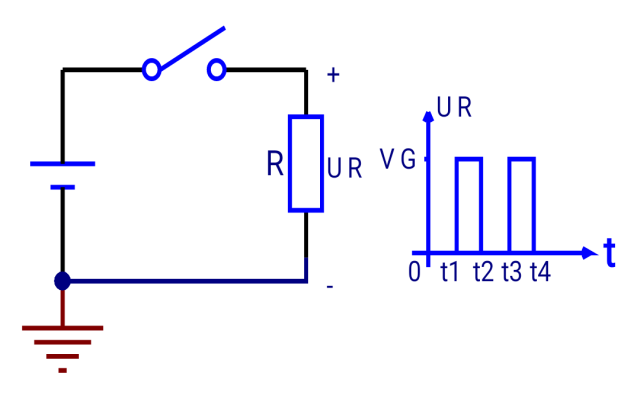

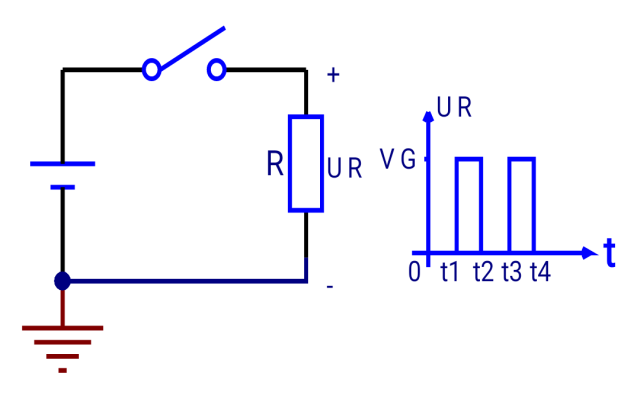

2981 數(shù)字電路輸出高電平時從電源拉出的電流Ioh和低電平輸出時灌入的電流Iol的大小一般是不同的,即:Iol>Ioh。

2019-11-06 16:47:43 8557

8557

FPGA 全稱「可編輯門陣列」(Field Programmable Gate Array),其基本原理是在 FPGA 芯片內(nèi)集成大量的數(shù)字電路基本門電路以及存儲器。

2019-09-16 17:53:31 861

861 模擬電路與數(shù)字電路的關(guān)系,有說所有電路都是模擬電路,數(shù)字電路只是模擬電路的一部分的;有說模擬電路和數(shù)字電路各成系統(tǒng),井水不犯河水的;有說線性的就是模擬電路,非線性的就是數(shù)字電路,不一而足。

2019-07-03 17:35:50 8629

8629 本文主要詳細介紹了數(shù)字電路比模擬電路的優(yōu)點,分別是數(shù)字電路結(jié)構(gòu)簡單、數(shù)字電路容易標準化、數(shù)字電路能夠滿足對信號保真度的要求。

2019-05-16 17:50:36 16644

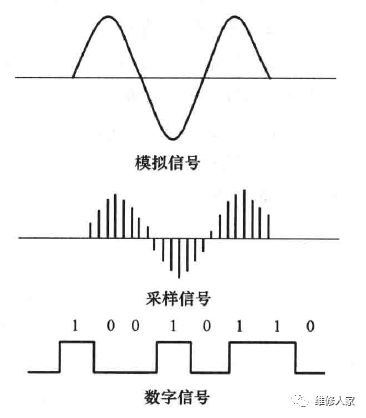

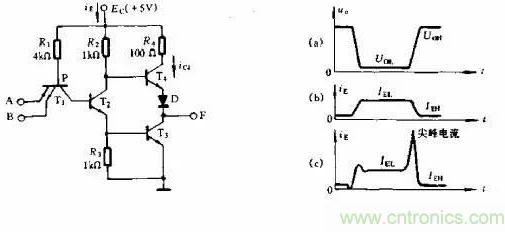

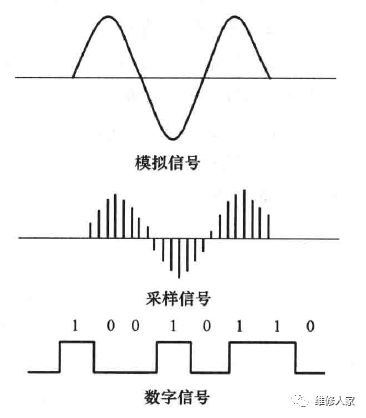

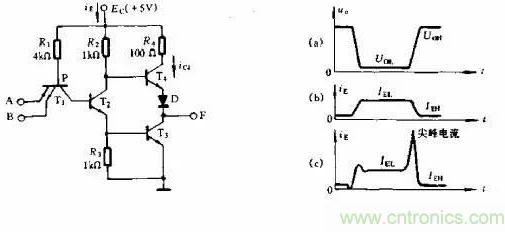

16644 數(shù)字電路是模擬電路的基礎(chǔ)上發(fā)展起來的,數(shù)字電路是以模擬電路為基礎(chǔ)的它們的基礎(chǔ)就是電流和電壓,但它們有著本質(zhì)的區(qū)別。在一個周期內(nèi)模擬電路的電流和電壓是持續(xù)不變的,而數(shù)字電路中它的電流和電壓是脈動變化的。

2019-05-10 16:43:16 35612

35612 電子設(shè)備從以模擬方式處理信息,轉(zhuǎn)到以數(shù)字方式處理信息的原因,數(shù)字電路的主要優(yōu)點在以下幾個方面:穩(wěn)定性好:數(shù)字電路不像模擬電路那樣易受噪聲的干擾。

2019-05-10 16:40:55 15286

15286 用VHDL語言設(shè)計交通燈控制系統(tǒng),并在MAX+PLUS II系統(tǒng)對FPGA/CPLD芯片進行下載,由于生成的是集成化的數(shù)字電路,沒有傳統(tǒng)設(shè)計中的接線問題,所以故障率低、可靠性高,而且體積小。體現(xiàn)了EDA技術(shù)在數(shù)字電路設(shè)計中的優(yōu)越性。

2018-11-05 17:36:05 23

23 模擬信號和數(shù)字信號的特點不同,處理這兩種信號的方法和電路也不同。一般地, 電子電路可分為模擬電路和數(shù)字電路兩大類。 1. 模擬電路 處理模擬信號的電子電路稱為模擬電路。模擬電路研究

2018-10-16 10:25:09 95060

95060 數(shù)字系統(tǒng)的設(shè)計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現(xiàn)數(shù)字設(shè)計。除了這些數(shù)字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數(shù)字邏輯單元實現(xiàn)共模功能,從而構(gòu)建模數(shù)轉(zhuǎn)換器(ADC)。

2018-04-26 11:53:00 995

995

用數(shù)字信號完成對數(shù)字量進行算術(shù)運算和邏輯運算的電路稱為數(shù)字電路,或數(shù)字系統(tǒng)。由于它具有邏輯運算和邏輯處理功能,所以又稱數(shù)字邏輯電路。現(xiàn)代的數(shù)字電路由半導(dǎo)體工藝制成的若干數(shù)字集成器件構(gòu)造而成。邏輯門

2018-03-23 17:27:39 32337

32337 數(shù)字編程是數(shù)字電路非常重要的一門課程,FPGA和CPLD是兩個重要的編程工具,本文帶您認識fpga和cpld的聯(lián)系和區(qū)別。 FPGA(Field-Programmable Gate Array),即

2017-12-01 10:07:59 18081

18081 ,或是硬件描述語言自由的設(shè)計一個數(shù)字系統(tǒng)。通過軟件仿真,我們可以事先驗證設(shè)計的正確性。在PCB完成以后,還可以利用FPGA/CPLD的在線修改能力,隨時修改設(shè)計而不必改動硬件電路。 使用FPGA/CPLD來開發(fā)數(shù)字電路,可以大大縮短設(shè)計時間,減少PCB面積,提高系統(tǒng)的可靠性。 FPGA/CPLD還

2017-10-09 09:52:20 14

14 CPLD_FPGA的數(shù)字通信系統(tǒng)建模與設(shè)計

2017-09-04 11:10:01 14

14 數(shù)字電路計步器,利用數(shù)字芯片實現(xiàn)對步數(shù)脈沖傳感器發(fā)出的信號進行統(tǒng)計和顯示。電路采用proteus進行仿真功能驗證,同時又相應(yīng)的配套CPLD實驗板進行配套驗證。

2017-06-11 09:21:38 74

74 電子天平中數(shù)字電路的CPLD實現(xiàn)_顧申申

2017-03-19 11:29:00 2

2 當(dāng)你需要將FPGA/CPLD內(nèi)部的信號通過管腳輸出給外部相關(guān)器件的時候,如果不影響功能最好是將這些信號通過用時鐘鎖存后輸出。因為通常情況下一個板子是工作于一種或兩種時鐘模式下,與FPGA/CPLD相連接的芯片的工作時鐘大多數(shù)情形下與FPGA的時鐘同源,如果輸出的信號經(jīng)過時鐘鎖存可以起到如下的作用:

2017-02-11 13:18:12 1792

1792

在數(shù)字電路的設(shè)計中,時序設(shè)計是一個系統(tǒng)性能的主要標志,在高層次設(shè)計方法中,對時序控制的抽象度也相應(yīng)提高,因此在設(shè)計中較難把握,但在理解RTL電路時序模型的基礎(chǔ)上,采用合理的設(shè)計方法在設(shè)計復(fù)雜數(shù)字系統(tǒng)

2017-02-11 13:04:32 1205

1205

數(shù)字電路設(shè)計方案中DSP與FPGA的比較與選擇

2017-01-18 20:39:13 15

15 數(shù)字電路7大基礎(chǔ)實驗

2016-12-20 17:20:06 8

8 脈沖與數(shù)字電路

2016-11-05 11:42:40 17

17 電子專業(yè)單片機相關(guān)知識學(xué)習(xí)教材資料——FPGACPLD數(shù)字電路設(shè)計經(jīng)驗,感興趣的小伙伴們可以瞧一瞧。

2016-09-13 17:46:48 34

34 在《數(shù)字電路之如雷貫耳的“邏輯電路”》、《數(shù)字電路之數(shù)字集成電路IC》之后,本文是數(shù)字電路入門3,將帶來「時序電路」的講解,及其核心部件觸發(fā)器的工作原理。什么是時序電路?

2016-08-01 10:58:48 17763

17763

關(guān)于電路的數(shù)字報告,能夠解決數(shù)字電路的實驗問題。

2016-05-16 11:56:08 1

1 數(shù)字電路中的FPGA和verilog教程,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-18 17:44:30 42

42 主要內(nèi)容有:第1 章實驗基本知識、第2 章 PROTEUS 仿真軟件快速入門、第3 章數(shù)字電路基礎(chǔ)實驗、第4 章數(shù)字電路綜合設(shè)計實驗、 第5章VHDL 語言基礎(chǔ)、第6 章 數(shù)字電路的CPLD/FPGA 實現(xiàn)。在教

2011-09-07 16:29:53 879

879 電子發(fā)燒友為大家提供了數(shù)字電路圖符號解析,希望對您有所幫助!像是多種場效應(yīng)管的電路圖符號,電位器符號等等。

2011-07-23 09:49:46 12568

12568

實驗安排及教學(xué)要求 1、鎖相環(huán)及頻率調(diào)制與解調(diào)電路 2、乙類功率放大器 3、數(shù)字電路的FPGA應(yīng)用實驗 4、脈沖電路及其應(yīng)用 5、綜合實驗

2011-04-05 17:18:22 98

98 《數(shù)字電路與FPGA》是高等教育自學(xué)考試、通信工程專業(yè)的一門專業(yè)基礎(chǔ)課,是在《電路分析》、《電子線路與pspice》課程知識的基礎(chǔ)上開設(shè)的必修課程之一,本課程的學(xué)習(xí)為通信系統(tǒng)底層硬件電路設(shè)計自動化打下了堅實的基

2011-03-15 15:33:34 48

48 摘要:在數(shù)字電路的設(shè)計中,時序設(shè)計是一個系統(tǒng)性能的主要標志,在高層次設(shè)計方法中,對時序控制的抽象度也相應(yīng)提高,因此在設(shè)計中較難把握,但在理解RTL電路時序模型的

2010-08-13 14:53:34 1680

1680 當(dāng)利用CPLD/FPGA開發(fā)系統(tǒng)完成數(shù)字電路或系統(tǒng)的開發(fā)設(shè)計并仿真校驗通過之后,就需要將獲得的CPLD/FPGA編程配置數(shù)據(jù)下載到CPLD/FPGA芯片中,以便最后獲得所設(shè)計的硬件數(shù)字電路或系

2010-06-01 10:14:46 23

23 基于FPGA和CPLD數(shù)字邏輯實現(xiàn)ADC技術(shù)

數(shù)字系統(tǒng)的設(shè)計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現(xiàn)

2010-05-25 09:39:10 1242

1242

摘要:在數(shù)字電路課程設(shè)計中引入先進的EDA技術(shù)是數(shù)字電路實驗教學(xué)改革的方向,本文通過一個數(shù)字電路課程設(shè)計的實例,說明了基于EDA技術(shù)中的VHDL語言和CPLD/FPGA器件進行數(shù)字系

2010-04-26 10:08:50 23

23 基于LabVIEW的數(shù)字電路設(shè)計和仿真

數(shù)字電路設(shè)計和仿真是電子工程領(lǐng)域的基本技術(shù)。介紹了基于LabV IEW的數(shù)字電路設(shè)計和仿真的原理和方法,比較了其與專業(yè)EDA軟

2010-03-30 16:09:49 123

123 數(shù)字電路設(shè)計

關(guān)于高速數(shù)字電路的電氣特性,設(shè)計重點大略可分為三項:

正時(Timing) :由于數(shù)字電路大

2009-08-26 19:08:06 2556

2556 數(shù)字電路圖

圖 數(shù)字電路圖

監(jiān)控單元本機監(jiān)控的實現(xiàn)比較簡單

2009-07-17 10:41:57 1341

1341

數(shù)字電路及其應(yīng)用

編者的話 當(dāng)今時代,數(shù)字電路已廣泛地應(yīng)用于各個領(lǐng)域。本報將在“電路與制作”欄里,刊登系列文章介紹數(shù)字電路的基本知識和應(yīng)用實例。

2009-04-07 09:38:37 3240

3240 數(shù)字電路是什么意思?

現(xiàn)代的數(shù)字電路由半導(dǎo)體工藝制成的若干數(shù)字集成器件構(gòu)造而成。邏輯門是數(shù)字邏輯電路的基本單元。存儲器是用來

2009-04-06 23:45:50 6907

6907

高速數(shù)字電路的仿真

介紹了專用于高速數(shù)字電路的仿真工具Hyperlynx,并使用它對高速數(shù)字電路中的阻抗匹配、傳輸線長度

2009-03-20 14:11:39 1226

1226

Altera FPGA/CPLD設(shè)計(基礎(chǔ)篇)系統(tǒng)地介紹了FPGA/CPLD的基本設(shè)計方法。在介紹FPGA/CPLD概念的基礎(chǔ)上,介紹了Altera上流FPGA/CPLD的結(jié)構(gòu)與特點,并通過豐富的實例講解Quartus II與ModelSim、Sy

2009-02-12 09:16:07 5248

5248 怎樣看數(shù)字電路圖緊扣“怎樣看數(shù)字電路圖”的主題,系統(tǒng)地介紹了看懂數(shù)字電路圖所必須掌握的基礎(chǔ)知識、基本方法和技巧,并通過電路實例進行了

2008-12-26 10:55:08 4338

4338 高速數(shù)字電路設(shè)計

關(guān)于高速數(shù)字電路的電氣特性,設(shè)計重點大略可分為三項 : Ø 正時 (Timing) :由于數(shù)字電路大多依據(jù)時脈信號來做信號間的同

2007-10-16 17:22:57 2697

2697

電子發(fā)燒友App

電子發(fā)燒友App

評論