ATE體系結(jié)構(gòu)的并行測試開銷

想要進(jìn)一步說明這個問題,考慮環(huán)繞聲音頻處理器對測試時間的影響。AC3數(shù)字音頻提供6路模擬輸出:前置L/R;環(huán)繞聲L/R;中央揚(yáng)聲器和超低單揚(yáng)聲器。從模擬觀點,這些器件需要高動態(tài)范圍與并行測試的結(jié)合。

CD品質(zhì)動態(tài)范圍和帶寬要求更高的取樣率。采用上面的公式而以Fs=4.8KHz代之,取樣時間為10.7ms。考慮到硬件設(shè)置、測試穩(wěn)定和其它開銷,測試時間取15ms。再考慮到10次以上的測量次數(shù),總測試時間上升到150ms。這樣對每個位置6聲道,串行測試實施方案將需900ms。

4測試點實施方案能充分利用多個波形數(shù)字化儀并行測試的優(yōu)勢。但數(shù)據(jù)傳送在多測試點測試中仍是串行的,傳送開銷是要累計的。因此,即使采用4個波形數(shù)字化儀,4測試點測試實施方案需900ms+4×600ms=3300ms。

多標(biāo)準(zhǔn)無線基帶處理器

無線設(shè)備在同一部手機(jī)中設(shè)置了多個標(biāo)準(zhǔn)。為了支持這些標(biāo)準(zhǔn),芯片組常常具有冗余的基帶模擬變換器和RF收發(fā)器。如在音頻環(huán)繞聲處理器中,無線基帶處理器中眾多模擬芯核對測試時間造成巨大的影響。測試這些器件的主要難題是如何在模擬測試硬件中設(shè)置充足的并行測試,以得到多測試點的效率。

基帶處理器塊由正交(I/O)發(fā)射(TX)DAC和接收(RX)ADC對組成。在2G至2.75G GSM/GPRS/EDGE技術(shù)中,載波信道間隔限于200KHz,導(dǎo)致低頻零IF。W-CDMA采用5MHz信道,對應(yīng)的帶寬較寬。

RX和TX路徑通常要求全動態(tài)測試,包括信號對畸變(SND)、CIN以及XTALK。I/Q對DAC和ADC還要求增益匹配和相位匹配測試,指標(biāo)分別規(guī)定在0.1dB和3度高精度內(nèi)。在發(fā)射期間保證信道隔離的要求,導(dǎo)致對DAC進(jìn)行附加的帶外(00B)衰減的測試。鄰道功率比(ACPR)能確認(rèn)信道隔離程度,對W-CDMA用DAC,檢驗的OOB頻率高達(dá)10MHz。

高清晰度視頻編碼器

當(dāng)前SoC器件支持多種視頻輸入標(biāo)準(zhǔn)。傳統(tǒng)的NTSC或PAL器件備有超級視頻CS-VIDEO和復(fù)合模擬輸出。支持HDTV需要3個附加輸出,來提供符合YPrPbHDTV(EIA-770.1-3)的信號。備齊上述全部輸出需用6個視頻DAC:2個用于S-Video、1個用于復(fù)合輸出、3個用于RGB。

雖然數(shù)字視頻標(biāo)準(zhǔn)最高要求的接口速度為74MHz,但測試DAC性能要求的模擬帶寬約為8MHz,分辨率10至12位。單個視頻DAC的典型測試項目包括積分非線性(INL)、微分非線性(DNL)以及SND測量。而HDTV系統(tǒng)的圖形質(zhì)量是由DAC輸出的相對精度決定的,須對輸出增益和相位匹配作附加測試。內(nèi)置數(shù)字視頻器件的總測試時間與測試可提供的并行數(shù)字化儀的數(shù)量直接相關(guān)。待測視頻DAC的數(shù)量通常在6個以上,由于缺乏測試儀資源,建立一套串行化測試方案是必不可少的。

并行測試方案

雖然降低總COT受多個變數(shù)的影響,但實施多點測試和并行測試來改進(jìn)吞吐率無疑是主要方法。最新一代ATE系統(tǒng)采用多端口體系結(jié)構(gòu),支持成組的和待測器件功能相匹配的測試儀資源結(jié)構(gòu)。

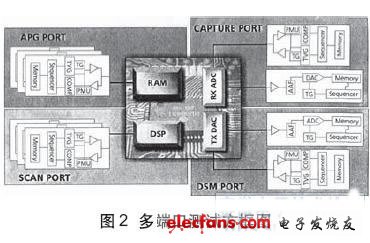

實現(xiàn)上述目標(biāo)的兩個主要功能是每端口定時發(fā)生器和每端口序列發(fā)生器,前者與測試芯核的頻率相匹配;后者可工作在不同測試模式并自動地執(zhí)行序列指令。每引腳多端口方案比上述方案更進(jìn)一步,將ATE系統(tǒng)的數(shù)字和模擬兩種資源的粒度細(xì)分至每個引腳 。測試典型SoC的必備的資源結(jié)構(gòu)實例包括:用作通信處理器的DSP、存儲器,以及與模擬IF或RF前端接口的ADC和DAC。在本場合,數(shù)字引腳配置成掃描模式,用來測試DSP芯核(見圖2)。

ADC塊需要任意波形發(fā)生器(Arb)和數(shù)字通道,數(shù)字通道處于捕獲模式來采集與分析ADC的輸出。DAC則需要多個數(shù)字通道組成的端口,用數(shù)字源存儲器(DSM)或波形存儲器段以及波形數(shù)字化儀來測試。每個端口能自動地工作在不同的測試頻率,執(zhí)行不同的序列指令。

由于測試系統(tǒng)已在每個引腳基礎(chǔ)上進(jìn)行分段,通過復(fù)制測試矢量的映象和每測試點使用的引腳上序列,應(yīng)用軟件能自動地管理絕大部分多測試點的控制。

并發(fā)測試是多端口測試的擴(kuò)充,讓這些芯核并行地進(jìn)行測試。當(dāng)然,器件中每個芯核應(yīng)是ATE系統(tǒng)可獨(dú)立地訪問和控制的,能獨(dú)立工作的。將每個器件芯核串行測試的純序列流修改為多個器件芯核并行測試的序列流,能大大減少測試執(zhí)行時間(圖3)。

用戶評論

共 0 條評論