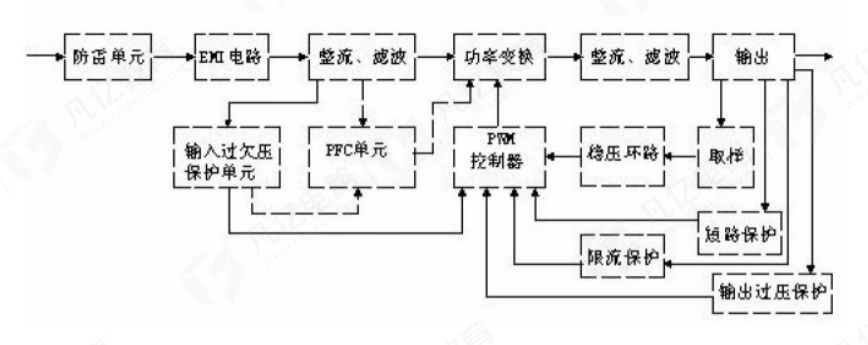

DC-DC轉換器可以實現各種電壓電平的高效電源轉換和供電,但是隨著需求的不斷上升,需要更高功率密度更高效率以及更小的尺寸,DC-DC轉換的PCB設計就更為重要了。

這篇文章主要是從:DC-DC轉換組件選擇、最小 EMI 布局、熱管理方面進行分析。 ? ?

一、路由注意事項

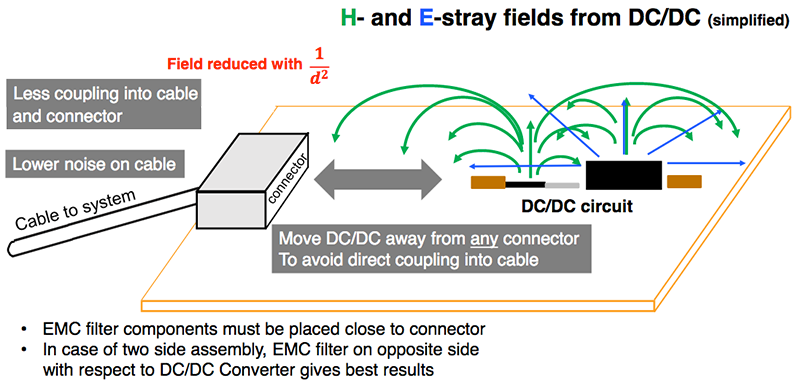

DC-DC轉換器的PCB布線會對電磁干擾水平產生重大影響,正確的 PCB布線技術幫助最大限度地減少EMI。 ? 走線長度和環路面積是DC-DC 轉換器(尤其是高頻開關轉換器)PCB 設計中的關鍵因素。 ?

1

走線長度

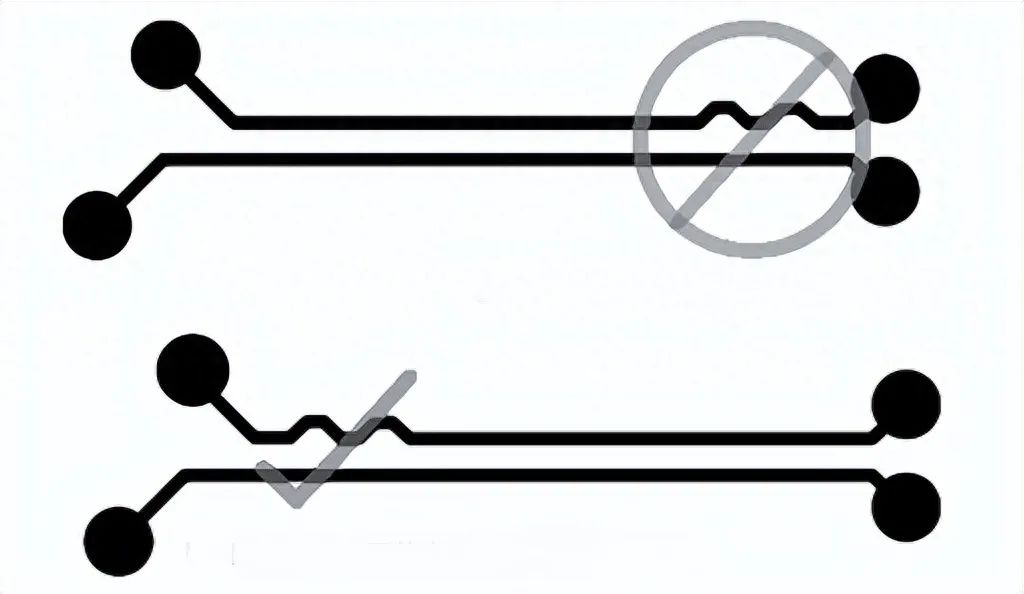

在高頻轉換器中,承載高速開關信號的走線長度對于保持信號完整性和降低EMI至關重要。 ? 較長的走線可以充當天線并輻射電磁能量,可能會對其他組件或電路造成干擾,此外,較長的走線可能會引起延遲、信號反射、寄生效應,從而導致轉換器效率和穩定性降低。 ? 因此走線長度應該盡可能短,尤其是對于高速時鐘和數據時鐘,適當的阻抗匹配技術和受控阻抗走線可u進一步優化信號傳輸并最大限度地減少信號衰減。 ? 對于高速信號,重要的是差分對的走線長度在整個PCB板上相同,如果不匹配,應該在不匹配的邊緣附近制作蛇形走線。 ?

高速 DC-DC 轉換器柵極信號的差分對走線匹配 ?

2

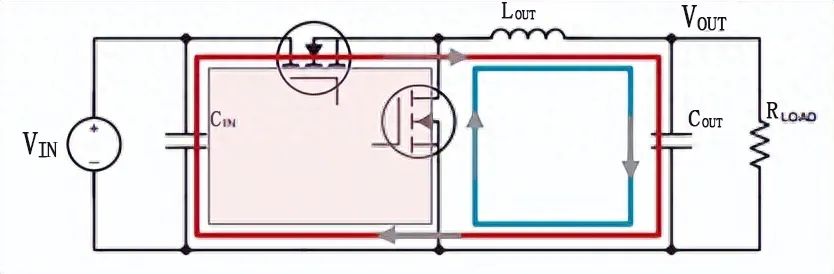

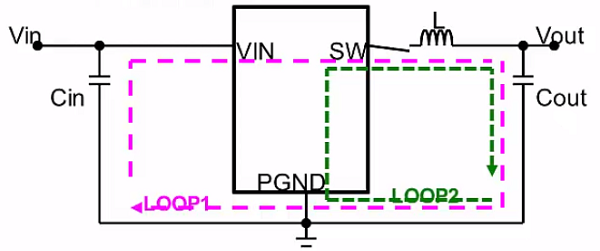

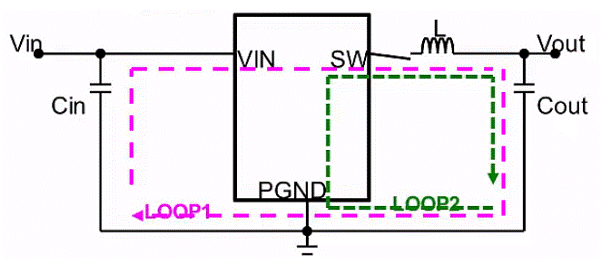

環路區域

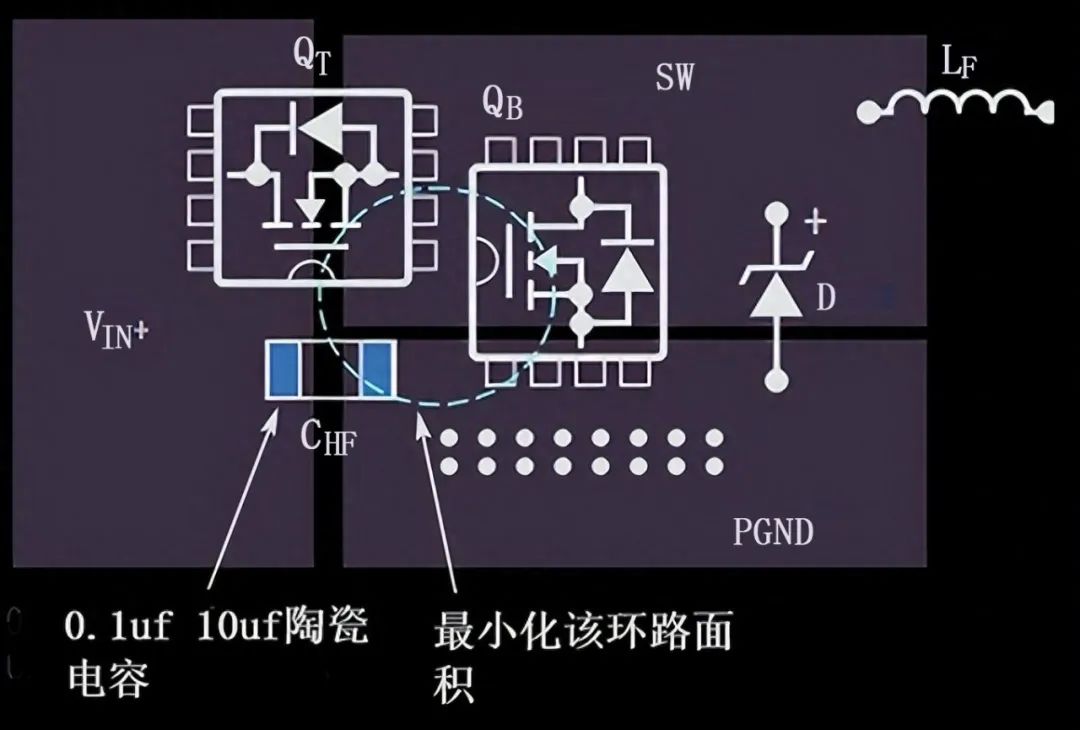

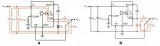

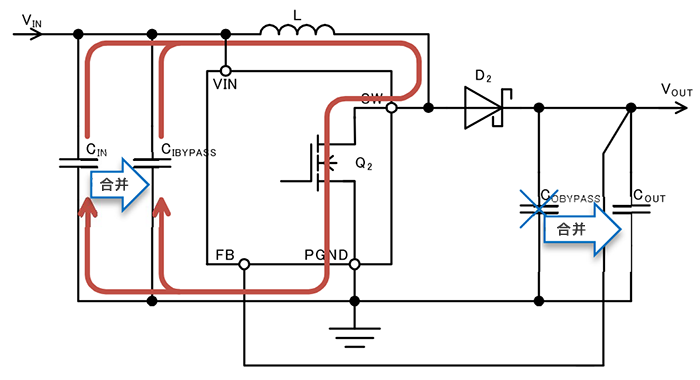

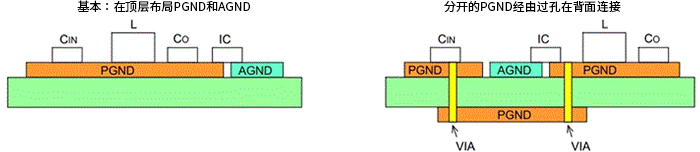

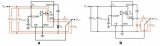

環路區域是指 PCB上的信號走線及其返回路徑形成的封閉區域,在DC-DC轉換器等高功率和高頻電路中,最小化環路面積對于降低輻射 EMI 至關重要。 ? 越大的環路面積會導致更多的磁通量與環路耦合,從而導致更高的 EMI。 ? 最小化環路面積的主要措施是:通過將信號走線放置在靠近其返回路徑的位置(例如利用接地層/緊密間隔的電源層)來最小化環路面積。 ? ?

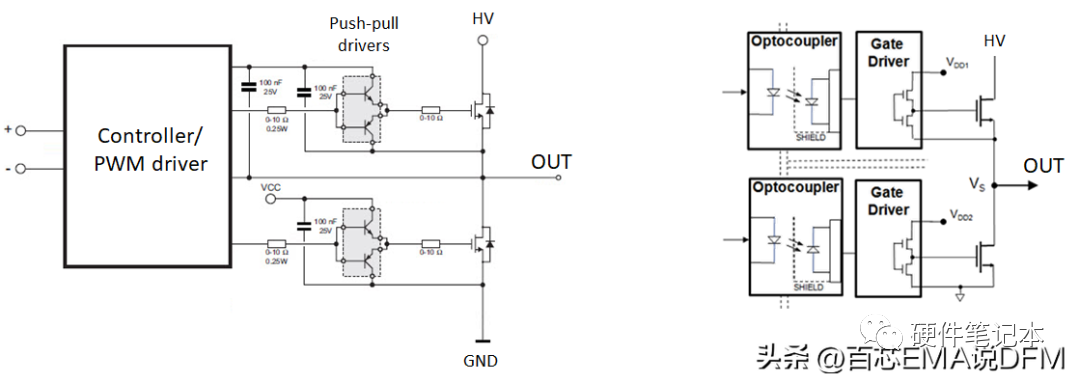

二、過濾器組件

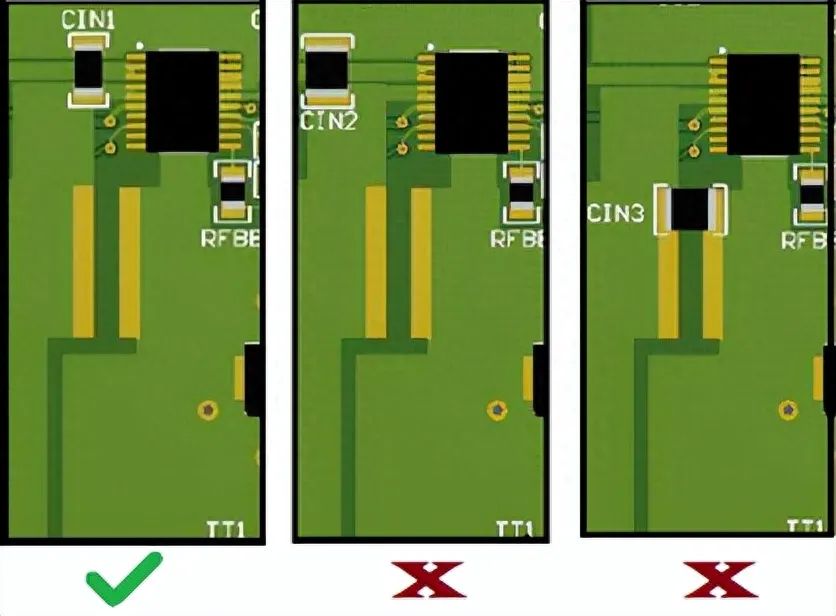

在關鍵信號和電源線中添加鐵氧體磁珠和共模扼流圈等濾波器組件可以減弱傳導電磁干擾并防止進一步傳播。連接濾波電容時,正確的位置對于濾除 EMI 至關重要。

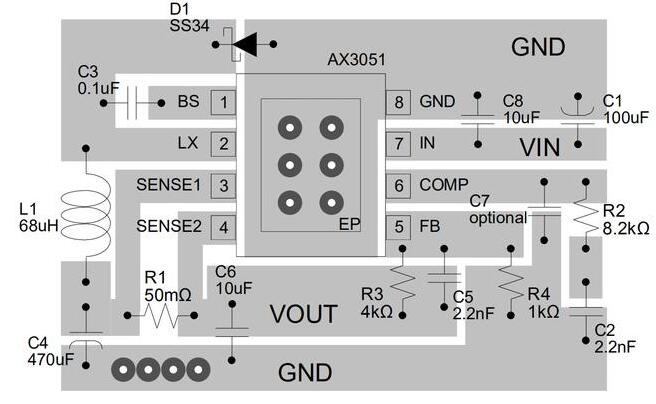

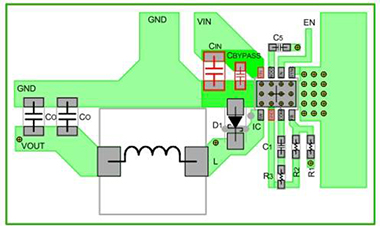

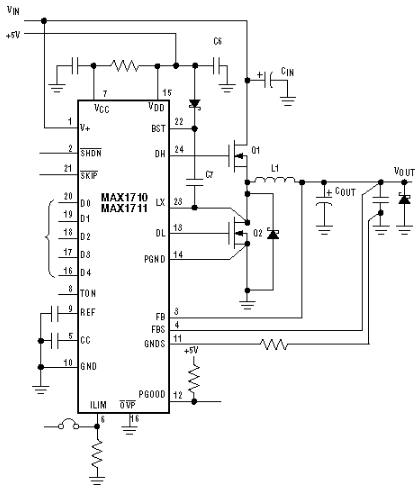

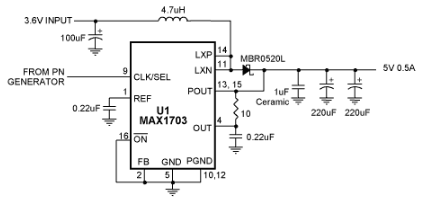

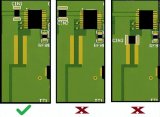

濾波元器件應該盡可能靠近 DC-DC轉換器放置,在 IC 和有源元件的電源引腳附近正確放置去耦電容有助于抑制高頻噪聲并提高EMI性能。 ?

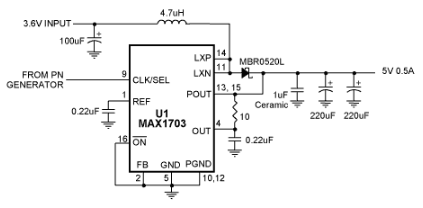

DC-DC 轉換器中去耦電容放置

三、寄生電感和電容

1

路徑電感

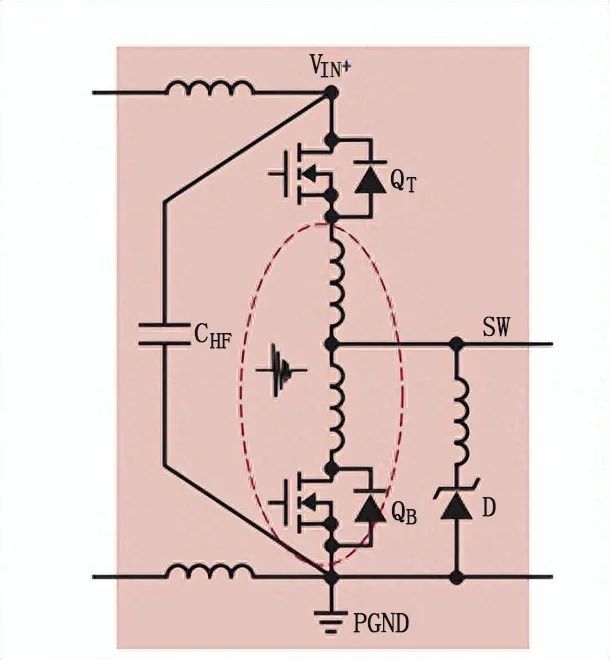

路徑電感是導電路徑(例如跡線/電線)的固有電感,取決于其物理尺寸和材料特性。在DC-DC 轉換器等高頻電路中,路徑電感會影響轉換器的效率和性能。

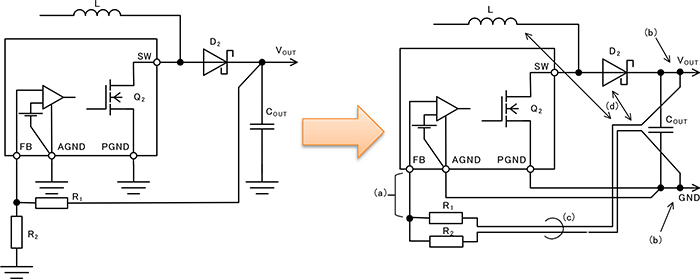

DC-DC 轉換器中高 di/dt 環路產生的路徑電感 ? 高路徑電感會導致電壓下降,開關損耗增加以及轉換器效率降低,還有可能導致電路中的電壓過沖和振鈴,影響信號完整性。 ? 為了最大限度地減少路徑電感,PCB工程師可以使用更寬的走線,更短的路徑,或者利用專用的接地層/電源層為高電流/開關信號創建低電感返回路徑。 ?

利用接地層并最大限度低減少di/dt 環路 ?

2

雜散電容

在高頻電路中,雜散電容會與高速信號耦合,導致不必要的電容耦合并增加EMI,還可能會導致信號失真和退化。 ? 為了最大限度低減少雜散電容,應該在信號走線、接地層、電源層之間保持適當的間距,適當的接地分段和隔離也有助于減少寄生電容。 ? ?

四、DC-DC 轉換器接地環路的影響

在設計DC-DC轉換器時,PCB工程師必須要考慮電流環路并正確放置組件,這樣可以讓環路在物理上金科能小。

DC-DC 轉換器中的電流環路 ?

1

接地環路過長的影響

由于接地環路過長會導致以下問題: ? ?

電磁干擾:接地環路可以充當天線,導致 EMI 輻射到周圍環境中。

噪聲和信號衰減:流經接地環路的電流會在不同接地點之間產生電壓差,可能會導致不需要的噪聲被引入敏感信號路徑,從而導致信號衰減和信噪比降低。

共模噪聲:接地環路可能導致共模噪聲耦合到敏感的模擬或數字電路中。這種噪聲會破壞信號精度,尤其是在低電平模擬測量或高速數字通信中。

寄生接地電流:循環電流可以在不同接地點之間流動,從而導致寄生接地電流。寄生電流會產生電壓降并影響轉換器的性能,從而導致效率低下和潛在的熱問題。

接地反彈:接地環路可能會導致接地參考平面之間存在電壓差,從而導致接地反彈。接地反彈是指開關事件期間接地電壓的瞬態增加,這可能會破壞信號完整性并影響數字電路的正常運行。

2

接地環路緩解措施

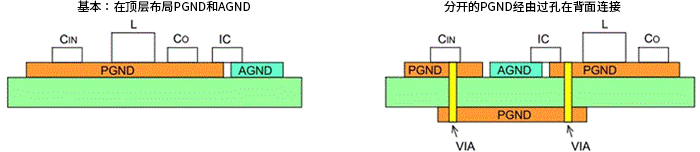

星形接地:將所有接地點匯聚到一個參考點,有助于消除接地環路并減少出現接地相關問題的可能性。

地平面:在 PCB 上使用堅固的接地層可確保電流的低阻抗返回路徑,從而降低接地環路的風險。

地面分割:對不同功能塊或組件的接地層進行適當的分割可以防止接地電流相互干擾。

將模擬地和數字地隔離:在物理上分離模擬和數字接地層可以防止敏感模擬電路和噪聲數字電路之間的干擾。

跟蹤路由:確保承載高電流或高頻信號的走線具有低電感返回路徑(例如,使用短而寬的走線或接地過孔)有助于最大限度地減少接地環路的可能性。

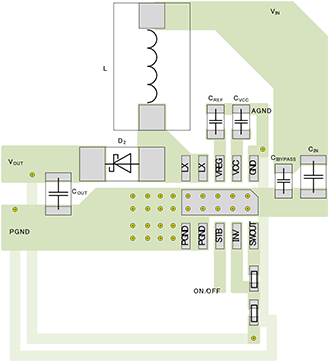

五、層堆疊

層堆疊指構成 PCB 的不同導電層和介電層的排列和配置,在確定電路板的性能、功能、可制造方面非常重要,下面就來分析一下層堆疊的重要性: ?

1

信號完整性和 EMI 控制

通過仔細選擇信號層和接地層/電源層的布置,工程師可以確保高速信號的受控阻抗、減少串擾并提高抗噪能力。 ?

2

接地和配電

層堆疊可以將接地層和電源層在整個 PCB 中恰當分布,接地層為信號提供低阻抗返回路徑,最大限度地減少接地反彈和噪聲。 ? 充足的電源分配可確保高效供電,從而減少電壓降和功率損耗。 ?

3

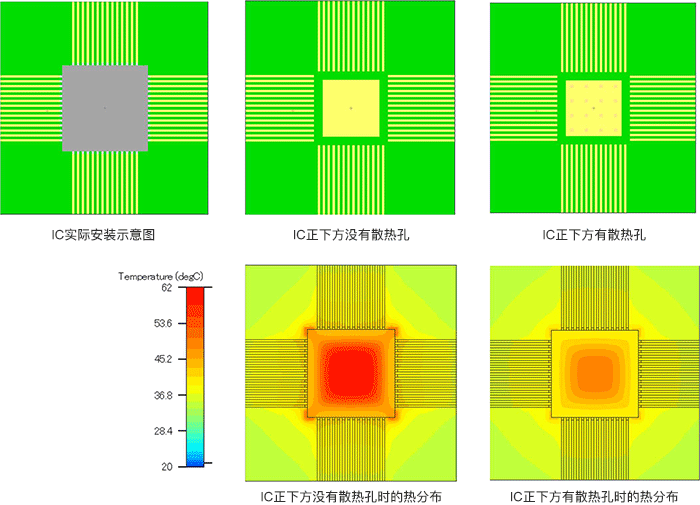

熱管理

層堆疊會影響 PCB 的熱性能。 ? 通過為電源和接地層分配專用銅層并仔細放置散熱通孔,工程師可以有效地散發電源組件產生的熱量并確保適當的熱管理。 ?

4

可制造性和組裝

正確的層布置、鉆孔對齊以及明確的堆疊規格可以實現順利的制造和組裝,從而降低生產過程中出現缺陷和錯誤的風險。 ?

5

多層設計和小型化

通過層堆疊工程師可以設計緊湊和小型化的 PCB。 ?

6

EMC 合規性

層堆疊有助于管理信號返回路徑、最小化環路面積并降低 EMI ,從而有助于 PCB 符合EMC 法規。 ?

7

信號路由和分區

層堆疊有助于 PCB 上不同功能塊之間的有效信號路由和分區。通過將敏感的模擬、數字、電源電路隔離在不同的層上,工程師可以增強信號隔離并減少干擾。

六、DC-DC轉換器 PCB的走線尺寸調整

走線寬度需要仔細考慮,走線寬度直接影響 PCB 的載流能力、功率損耗和熱性能,下面是確定 PCB 走線寬度的關鍵因素:

1

載流量

確定 DC-DC 轉換器電路中每條走線將承載的最大電流,包括流經 MOS 管、電感和電容等功率組件以及高電流信號走線的電流,最大電流應考慮瞬態尖峰和潛在的過流情況。 ?

2

溫升及允許溫度

使用以下公式根據最大電流和走線寬度計算走線的溫升: ? ΔT = (I^2 * R_trace) / (k * A) ? ? ?

ΔT 是溫升

I 是電流

R_trace 是走線電阻

A 是走線的橫截面積

k 是 PCB 材料的熱常數

3

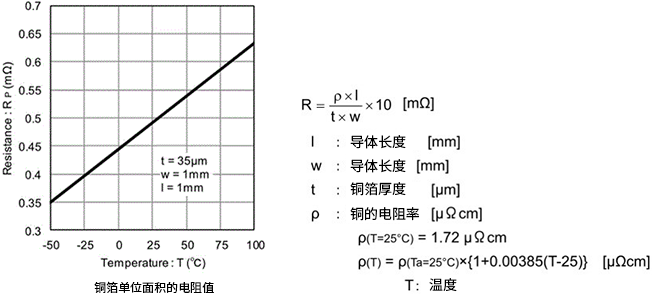

走線電阻

使用以下公式計算走線電阻:R_trace = ρ * (L / A) ρ是走線材料(銅)的電阻率 L是走線的長度 A是走線的橫截面積(寬度*厚度)?

4

電壓降

根據設計要求中指定的最大電流和允許電壓降,計算走線上可接受的電壓降。?

5

銅的重量和厚度

確定 PCB 的銅重量和厚度。標準銅重量包括 1 盎司(35 μm)、2 盎司(70 μm)和 3 盎司(105 μm)。?

較厚的銅可實現更高的載流能力,但會增加 PCB 成本和可制造性方面的考慮。

6

走線寬度計算

使用計算出的電流、走線電阻和電壓降值,使用在線走線寬度計算器或考慮 PCB 銅厚度和材料的 PCB 設計軟件來計算所需的走線寬度。?

7

尺寸空間限制

確保確定的走線寬度適合可用區域,且不違反間隙和間距要求。?

8

散熱

確保計算出的走線寬度和銅重量能夠實現高效散熱,并且不會導致溫升過高,尤其是對于高電流走線。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論