對于 48V 電源系統中的 GaN FET 應用,現有的一種方法是使用基于 DSP 的數字解決方案來實現高頻和高效設計。這在很大程度上是由于缺乏設計用于 GaN FET 的合適控制器的可用性。DSP 解決方案需要額外的 IC,這會增加額外的復雜性和挑戰。在本文中,作者介紹了一種與 GaN FET 兼容的模擬控制器,該控制器的材料清單數量很少,讓設計人員能夠以與使用硅 FET 相同的簡單方式設計同步降壓轉換器,并提供卓越的性能

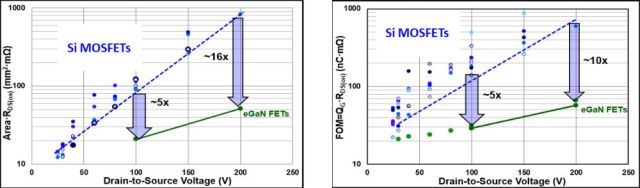

眾所周知,與傳統的硅 FET 相比,氮化鎵 (GaN) FET 已展示出卓越的電路內性能。由于 GaN FET 的高效率而產生的熱量更少,系統成本也可以大大降低。然而,構建商用電源的公司在使用 GaN FET 進行大規模生產時面臨著一些挑戰。以下是我們從客戶那里聽到的一些示例:

“基于 GaN FET 的設計與我們對硅 FET 所做的完全不同。” (電源制造商)

“使用 GaN 需要數字控制,我們對此猶豫不決;設計模擬電路更容易,成本更低,而且我們知道該怎么做。” (電信公司)

“GaN FET 即將問世,而且意義重大。如果我們可以開始縮小散熱器尺寸,這將是一件大事,但問題是我們需要一個微控制器來配合它。” (家電廠商)

許多設計工程師已經看到使用 GaN FET 的好處。然而,他們一直猶豫將 GaN 帶入實際設計,主要是由于設計復雜性。隨著 GaN FET 成本的降低,與硅 FET 相比較高的成本可以通過系統級節省來抵消。如果我們假設客戶永遠是對的,那我們該如何幫助他們?

在瑞薩電子,我們正在 48V 系統中使用 100V GaN FET 來解決這個問題。本文將探討這種方法,以及解決客戶問題的方式與以前的方法完全不同。

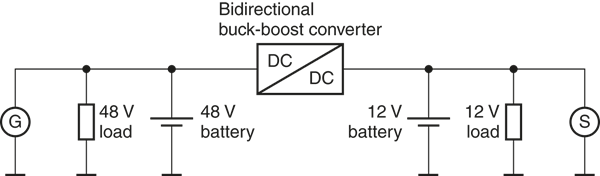

自從開發了電話設備以來,電信和無線基礎設施應用通常使用 48V 直流電源。近年來,數據中心和高端汽車系統也開始采用 48V,因為它仍然被認為是安全的低壓,安全要求要低得多,但允許使用更小規格的電線,壓降最小。已發表多篇文章討論迅速興起的 48V 市場1。

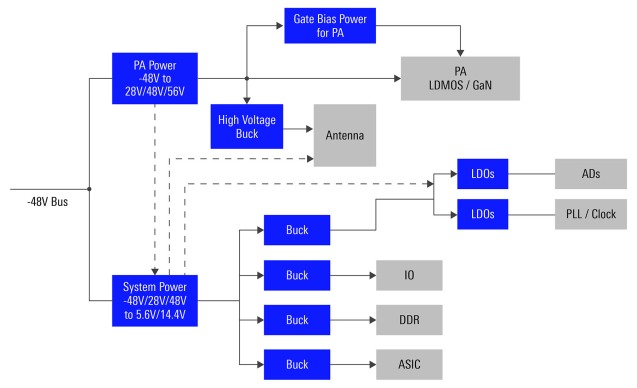

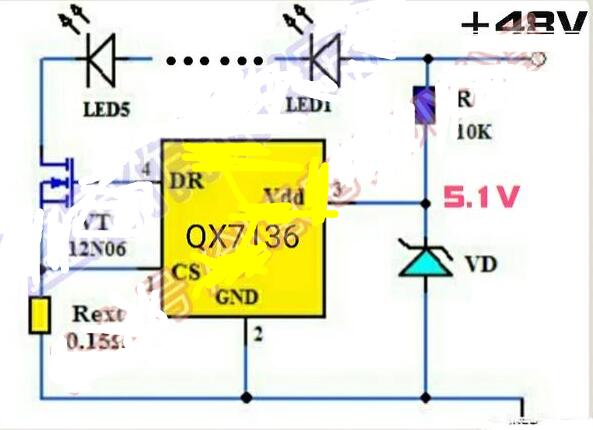

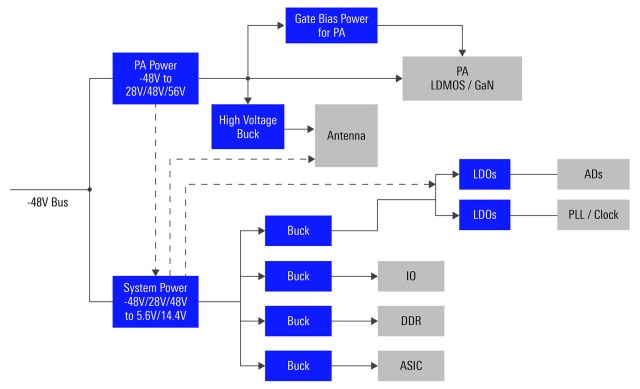

5G AAU(有源天線單元)的典型電源樹圖如圖 1 所示。從系統的 -48V 輸入總線,有一個 DC/DC 轉換成數百瓦或千瓦級,將 -48V 轉換為 +28V,或+48V~+56V,饋入大功放陣列。轉換后的正電壓還可以創建 12V 或 5V 總線來為其他系統負載供電,例如時序/時鐘、內存、ASIC/FPGA 等。(如果 -48V 已經與主電源隔離,則不需要隔離,例如交流或可再生能源)。顯然,隨著 5G 市場的迅速崛起,在 AAU 和 BBU(基帶單元,未顯示)中有多個不同功率級別的 48V 轉換,具有巨大的市場潛力。投資于額定電壓為 80V 或 100V 的 GaN FET 以取代傳統的硅 FET 符合 GaN 制造商的最大利益。

在無線基礎設施應用中采用 GaN 的一些潛在好處包括提高系統效率、最小化解決方案尺寸、降低電力成本和簡化熱管理。特別是對于 5G AAU,它甚至可以減輕系統重量,考慮到更分散且有時具有挑戰性的安裝,這一點非常重要。

圖 1:典型 5G AAU 電源樹圖(未顯示交流電源)

詳細的電源架構取決于站點類型、覆蓋范圍、位置以及與電網或遠程電源的距離。

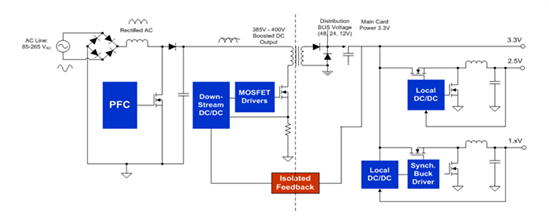

先前發布的使用 GaN FET 方法的 48V 總線電源轉換參考設計來自最著名的 GaN FET 公司之一,高效電源轉換 (EPC),EPC9143(如圖 2 所示)。整個設計是開源的2。

該參考設計基于行業標準的 1/16磚轉換器占位面積,可根據兩相交錯配置從 18V 輸入轉換為 60V,并轉換為額定電流為 25A 的 12V 輸出。除了 EPC GaN FET 之外,該設計還使用了 16 位數字控制器,運行頻率為 500kHz,并提供 >95% 的峰值效率(該控制器具有 DSP 內核和額外的模擬部分,為簡單起見,我們將其稱為 DSP文章)。

圖 2:帶有 DSP 控制器的 EPC9143 參考設計,頂部和底部

雖然這種設計無疑提供了非常令人印象深刻的性能,但我們的團隊注意到它還使用了六個其他集成電路 (IC),如圖 2 參考設計所示。

使用許多數字電源控制器,用戶可以靈活地重新編程輸出電壓和保護閾值,并且可以添加其他所需的功能。然而,對于某些 48V 應用,一旦設計確定,就不需要重新編程這些配置,因此控制調制器可以以模擬方式設計,與數字方式一樣有效。在瑞薩,我們開始考慮是否可以將 EPC9143 中所需的七顆 IC 組合并替換為僅使用一顆模擬 IC,并且仍能實現類似的性能。雖然 DSP 解決方案幾乎實現了 GaN FET 設計的最大潛力,而且效率遠高于硅 FET,但以更簡單的 BOM 實現相同目標將為客戶提供更高功率密度和更低解決方案成本的好處,這與效率同樣重要。

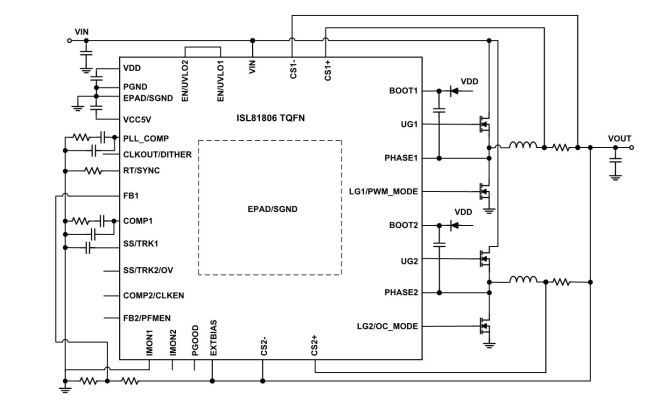

在簡化產品定義、IC 設計和全面驗證工作之后,瑞薩電子開發了一款 80V 雙同步降壓控制器,專門針對驅動 E 模式 GaN FET 進行了優化,即 ISL81806(圖 3)。

圖 3:ISL81806 80V 雙輸出/兩相 GaN FET 控制器

ISL81806 使用兩相交錯式拓撲結構,可以并聯成多達六個交錯相來承受千瓦級負載,而無需外部數字控制來分配相位。

其他功能包括:

寬輸入電壓范圍:4.5V 至 80V – 允許電信應用

寬 Vout 范圍:0.8V 至 76V

支持恒壓或恒流輸出

寬開關頻率:100Khz 至 2MHz

擊穿保護、OCP、OVP、OTP、UVP

每個輸出的獨立 EN 和軟啟動

針對增強型 GaN FET 優化的柵極驅??動和死區時間

EPC 和 Renesas 開發了一種新的參考設計板4,稱為 EPC9157(圖 4)。它采用與圖 2 中的 DSP 解決方案相同的兩相交錯拓撲和 1/16磚模塊外形尺寸進行設計。該板的額定輸入電壓、輸出電流和相同的 500kHz 頻率與 DSP 解決方案相同. (在本文發布時,此板可額定為 80V 輸入)。

圖 4:使用 ISL81806 和四個 GaN FET 的 EPC9157 EVB,僅模擬控制

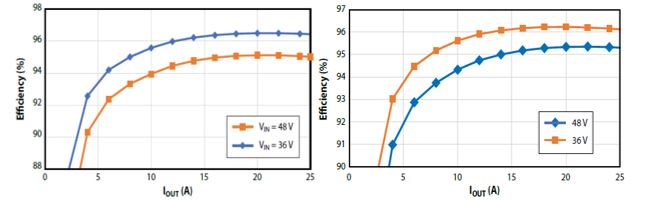

基于 DSP 的 EVB 和基于模擬的 EVB 的效率如圖 5 所示,在峰值功率時非常接近。基于模擬的 EVB 具有更好的輕負載效率,部分原因是單個模擬控制器消耗的工作電流 (50μA) 比 DSP 解決方案所需的七個組合 IC 少,并且可以直接使用 12V 輸出作為 IC 電源的外部偏置。

圖 5:效率比較(左:使用 DSP 的 EPC9143,右:使用 ISL81806 的 EPC9157)

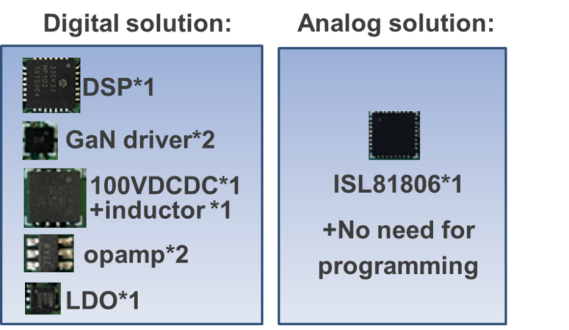

下面的圖 6 顯示了數字和模擬解決方案之間的主要 BOM 差異(省略了無源組件)。很明顯,模擬解決方案電路BOM非常簡單,只需要一個IC,不需要任何編程。

圖 6:BOM 差異

雖然 ISL81806 已經提供了一流的效率、解決方案尺寸和物料清單尺寸,但在未來的修訂中仍有改進的空間。正如 GaN FET 技術在過去幾年中迅速發展一樣,瑞薩電子致力于定義和設計匹配控制器的團隊也面臨著新的挑戰和機遇。

未來發展可能帶我們進入的一些方向包括(但不限于):

提高擊穿電壓

100V 可能是遠程 AAU 以及板安裝磚電源模塊的首選,特別是對于具有長電纜的電信,以使其更加堅固。

更強和分離的柵極驅動

可能需要更強的柵極驅動器以獲得更高的效率。然而,這也帶來了非常快的 dV/dt,它有可能因任何非理想布局的大雜散電感產生的負電壓損壞 IC。可能需要單獨開啟/關閉以優化開關速度,如參考文獻 5 中的 RAA226110 等分立 GaN 驅動器 IC。

優化布局的小封裝

GaN 供應商推薦不帶擴展引腳的 CSP 或 BGA 等小型封裝,以進一步降低系統雜散電感。但是,某些具有潛在惡劣環境部署的應用程序不能接受 CSP 或 BGA 封裝。

IC工藝改進

IC 開關節點需要非常穩健,才能在開關期間處理高 dV/dt > 200V/ns 和負電壓。內部自舉二極管可能更喜歡接近零 Qrr 以啟用高頻。此類要求可能會挑戰 IDM 或代工廠以改進其 IC 制造工藝。

對死區時間優化的更多研究

出于安全目的,需要在高邊開關關閉和低邊開關打開之間留有一點死區時間。在死區時間期間,GaN FET 的“體二極管”功能傳導負載電流。GaN FET 具有獨特的“體二極管”模式,Qrr 為零,但正向壓降相當大6. 因此,在死區時間期間,不僅導通損耗增加,而且自舉電容可能會過度充電,從而損壞頂部器件。為了優化非常小的且仍然安全的死區時間,我們還必須考慮由于溫度和批量生產分布導致的 IC 和其他 BOM 參數偏移。像 ISL81806 這樣的 E-MODE 控制器使用針對 GaN FET 優化的固定最小死區時間,EPC9157 EVB 設計有外部低成本保護電路,以避免自舉電容器過度充電。然而,這可能限制了實際的工作頻率。一些 DC/DC IC 供應商添加了死區時間編程引腳或使死區時間數字可編程。無論哪種方式,這都將死區時間選擇的艱巨工作留給了電路設計人員,并且未來可能需要更智能的 IC 功能。

增加靈活性以適應各種 GaN 技術

與普通硅 FET 不同,各種 GaN FET,甚至所有基于增強模式的 FET 都可能具有完全不同的設計。例如,推薦的柵極電壓在制造商6之間可能存在很大差異,并且由于它們需要在不同的 OVP 水平下受到保護而成為問題。除了未來提供的其他可能變量之外,柵極驅動電壓可能需要可編程。

GaN FET 前景光明,有朝一日,它們可能會以合理的成本和更好的性能成為硅 FET 的“直接替代品”,而 ISL81806 等控制器正在通過進一步的產品開發幫助實現這一目標. 當設計適當的控制器來控制它們時,現在使用 GaN FET 就像使用硅 FET 一樣容易。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論