您的位置:電子發燒友網 > 電子技術應用 > 電源管理 > 開關電源 >

多模式開關電源控制芯片的低功耗設計方案

2012年02月08日 10:50 來源:《固體電子學研究與進展 作者:郝炳賢,吳曉波,陳 我要評論(0)

引 言

所謂多模式控制就是在開關電源的工作中根據負載情況的不同采用不同的控制策略,以降低其功耗,提高效率。它是針對常用開關電源在輕載和待機條件下效率低的特點提出的,其設計思想可描述為:在重載下采用PWM 模式,以發揮其重載下效率高的優點;在輕載下采取PFM 模式,通過降低開關頻率來降低功耗;而在極輕載條件下(待機模式下)則采取BURST模式來降低功耗。

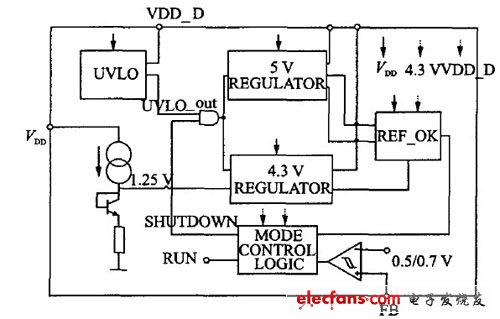

針對降低多模式開關電源控制芯片在輕載與待機工作模式下功耗,提高其全負載條件下工作效率的需要,提出一種開關電源控制芯片供電系統的設計方案,實現了其在啟動、關斷、重載、輕載以及待機等各種工作情況下的高效率低功耗工作。該供電系統主要包括欠壓鎖定電路、數字模塊電源單元和兩種不同的模擬模塊電源單元,以及狀態檢測模塊和模式控制邏輯單元,能夠實現電源的上電、掉電控制,同時能夠根據電源的負載條件控制各模塊的開通關斷以實現低功耗工作。該系統已應用于綠色多模式反激式開關控制器的設計中,取得了提高電源效率、降低待機功耗的作用。芯片采用1.5 um BiCMOS工藝設計制成。測試表明,所設計電源的各項指標均已達到設計要求。

1 系統與電路設計

1.1 系統構成

整個系統的構成如圖1所示。系統中包括一個欠壓鎖定電路(UVLO,Under voltage lockout),用于保證電路在合適的電壓范圍內正常工作;一個帶隙基準電壓源和一個專為數字模塊供電的電壓源(記為VDD_D),分別為芯片提供基準偏置和數字部分的電源。具體構成時此兩模塊包含在UVLO模塊內。兩個電壓調整器(REGULATOR)分別產生一個5 V和一個4.3 V 的穩定電壓,其中5 V穩定電壓源輸出記為REG,用于在重載時為控制器供電(輕載時關斷);4.3 V 穩定電壓源輸出記為VDD_AD,用于輕載時的供電。當然,必要時還可以利用帶隙基準產生更多不同的電壓以滿足復雜控制模式的需要。

圖1電源系統框圖

此外,本設計中還設置了一個REF-OK模塊來判斷上電后電源系統是否已進入正常工作狀態。

1.2 欠壓鎖定電路的設計

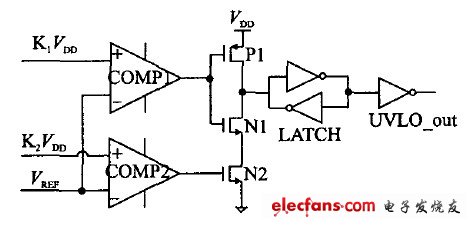

欠壓鎖定電路又稱UVLO,見圖2.圖中 VDD為芯片外部供電電源,設計值為12 V.欠壓鎖定電路的窗口設置為7~9.5 V,即上電后電壓上升到大于9.5V 時芯片開始正常工作,而當供電電壓小于7 V時芯片停止工作。考慮到欠壓鎖定電路在電源控制芯片中的重要性,設計給出了兩種實現方案,并對兩種控制策略的性能進行了分析與比較。

圖2 兩個比較器實現的欠壓鎖定電路

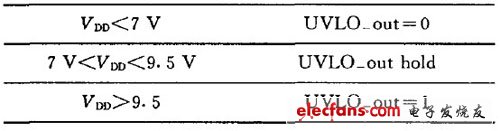

圖2給出第一種欠壓鎖定電路的原理圖,稱為U-VLO1,這是用兩個比較器實現的欠壓鎖定電路。VDD是外部供電電壓源,K1、K2 是小于1的常數,且K1>K2,VREF為1.25 V帶隙基準電壓,LATCH是由兩個反相器組成的鎖存器。圖中標的UVLO_out代表欠壓鎖定信號,狀態設置是UVLO_out=0時有效。

電路的工作原理可簡述如下:12 V供電電壓可在VDD比較低時建立一個PTAT (ProportiONal toabsolute temperature)電流源,然后利用其建立起帶隙基準電壓源;當VDD由0上升時,帶隙基準電壓r首先建立,此時兩個比較器的輸出為低電位,P1導通,輸出為高電位;當K1VDD大于 r時,COMP1輸出跳變,N1管導通,鎖存器鎖存上一個信號,UVLO為高電位(注意其為低電位有效);當K2VDD大于VREF 時,N2導通,則UVLO-out為低電位,使能其他模塊;隨著VDD減小,K2VDD首先小于VREF,N2關斷,則鎖存器鎖存信號,UVLO-out保持;當 VDD減小到K1 VDD小于VREF時COMP1跳變,P1導通,N1關斷,則輸出UVLO-out為高電位,關斷整個控制芯片。

表1 UVLO 的狀態對應表

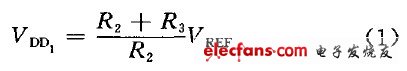

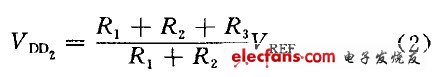

另一個方案是利用一個比較器實現的UVLO電路,稱UVLO2.該電路的特點是通過外部遲滯實現了欠壓鎖定功能,可應用于高壓和低壓場合,如圖3.電路的工作原理如下:當VDD由0上升到一個比較小的值時,帶隙基準電壓VREF首先建立,當VDD上升到:

時,比較器開始跳變,N1關斷,UVLO-out為0,使能整個控制芯片。當外部電源電壓開始減小到:

時,比較器跳轉,N1開通,UVLO-out開始變l.通過合理設置R1、R2、R3值就可以使VDD1=9.5 V,VDD2=7V,即VDD上升到9.5 V時UVLO輸出為零,芯片正常工作; VDD下降到7 V 時芯片停止工作。

圖3 用外部遲滯實現的欠壓鎖定電路

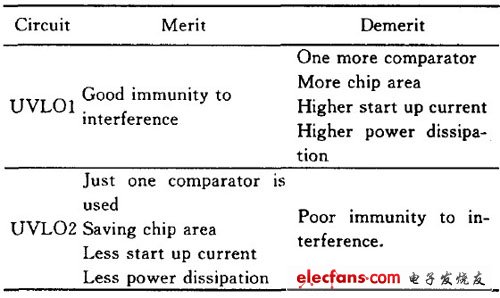

兩種方案的工作特性對比結果如表2所列。需要指出的是,若直接用門電路實現施密特觸發,由于"的工藝離散性,將使觸發電壓難以準確控制。

表2 兩種欠壓鎖定電路比較

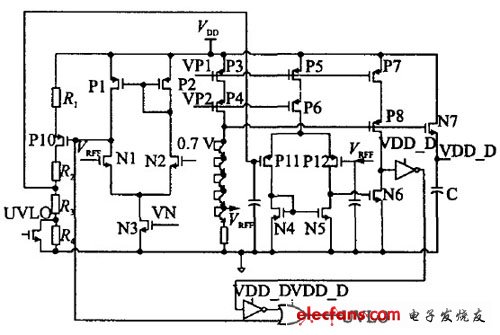

經比較可知,UVL02結構較為簡單,面積小,啟動電流小,有利于降低功耗。因此,本設計最終采用了UVL02方案。此外,為最大限度減小功耗,設計中將帶隙基準電壓、數字電源和欠壓鎖定電路集成在一起。具體電路圖見圖4。

圖4 欠壓鎖定和數字電源的具體電路圖

圖中利用帶隙基準電壓加上四個二極管連接的三極管產生一個大于4 V 的電壓,然后經過M0S管產生一個大約2.65 V左右的電壓。這個電壓在基準電壓建立后就產生了,主要用于為欠壓鎖定電路的數字部分供電,并且擔任了為整個系統的數字電路供電的任務。

本文導航

- 第 1 頁:多模式開關電源控制芯片的低功耗設計方案(1)

- 第 2 頁:5 V基準電壓源(REG)

- 第 3 頁:模式控制和效率測試