采用TOPSwitCh的電磁兼容性原理設計

????? 本文運用TOP224Y構成一款30W反激變換電路,對其進行了電磁兼容分析,并在多個方面實施EMC優化設計,實驗結果表明文中分析的有效性,為反激變換電路的EMC設汁提供了一定的理論根據。????

????? 隨著現代逆變技術的發展.開關電源正向著高頻化、小型化的方向發展:在此基礎上開發出的三端隔離、脈寬調制型反激式單片開關電源,集成了高壓M0SFET、振蕩器、脈寬調制器、閉環控制電路以及限流、過熱保護功能的集成芯片。以其為核心構成的單片開關電源外圍電路簡單,輸入電壓范圍寬,達到85~265V,電能轉換效率達到90%,已被廣泛應用于中小功率開關電源中。

????? TOPSwitch單片電源應用頻率一般在20kHz以上,這樣對前級電路(通常是電網)帶來很大的電磁干擾問題,危及其他電氣設備的正常運行;而且其本身產生的干擾直接危害到電子設備的正常工作。為此必須對電路進行電磁兼容(EMC)設計,使電磁干擾問題限制在允許的范圍內。

1 電磁兼容分析

??? 根據國際電工委員會(IEC)定義,電磁兼容性是電子設備的一種功能,電子設備在電磁環境中能完成其功能,而不產生不能容忍的干擾。解決EMC問題,主要考慮3個要素,即噪聲源、耦合途徑、噪聲接收機。因此,電磁兼容沒計的任務就是消弱千擾源的能量,隔離或減弱噪聲耦合途徑及提高設備對電磁干擾的抵抗能力。

1.1 共模、差模電路模型分析

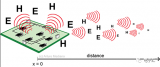

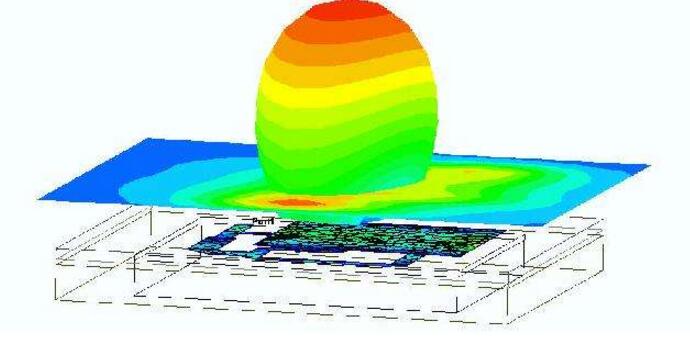

??? 單片開關電源的集成度很高,已經通過合理的設計將引線電感和寄生電容參數減小到比較小的水平。電路的共模電磁干擾主要是漏一源電壓和輸出整流管反向恢復過程產生的,由于高頻變壓器的分布電容以及芯片對地分布電容的影響,高頻電流不能完全抵消,形成共模干擾,其電路模型如圖1所示。這種共模干擾可以通過EMI濾波器的共扼電感和Y電容提供高頻電流對地泄放通道進行抑制。差模干擾電路模型如圖2所示,也可以通過EMI濾波器的X電容進行抑制。

1.2 高頻變壓器噪聲

??? 高頻變壓器是開關電源中實現能量儲存、隔離輸出、電壓變換的重要元件,同時它的漏感和分布電容對電路的性能帶來不可忽略的影響。其等效電路模型如圖3所示。

??? 當不考慮變壓器的漏感以及開關動作時間時,高頻工作下的MOSFET產生的波形是一個標準的方波,如圖4所示。

??? 而實際變壓器制作中,繞組漏感是不可避免的,由于漏感的存在,當開關閉合時(ton)原邊漏感儲存了一定的能量(與漏感大小和開關頻率有關),當開關關斷時(從ton到toff)儲存在原邊漏感中的能量釋放,使得開關器件的兩端出現電壓關斷尖峰,疊加在直流高壓V1和感應反射電壓VOR上,可使MOSFET的漏極電壓超過700V,影響開關工作的可靠性甚至損壞TOPSwitch。考慮變壓器漏感時實際電路的波形如圖5所示。

1.3 輸出整流二極管的尖峰干擾

??? 二極管導通時,在P區和N區分別有少數載流子電子和空穴導電,當突然加反向電壓時,存儲電荷在反向電場作用下被復合,形成反向恢復電流。由于變壓器次級漏感、引線電感及二極管的結電容,在關斷電壓上疊加了一個衰減振蕩電壓,形成了關斷電壓尖峰,如圖5所示。對此可以通過外接RC吸收電路抑制二極管電荷存儲效應所產生的浪涌電流。

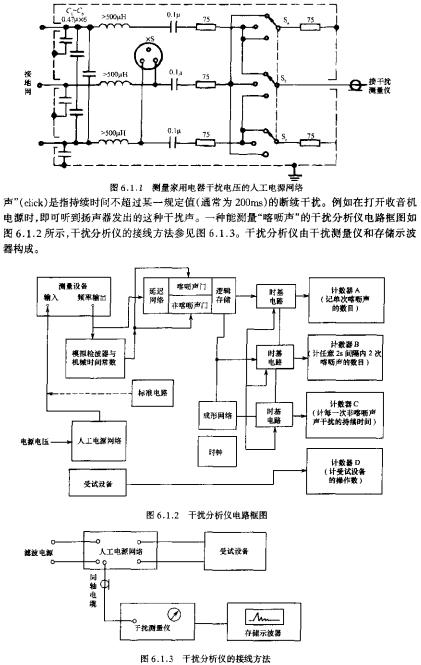

??? 電磁干擾有一定的標準,目前被世界廣泛采用的是歐洲的EMC標準,對于開關電源電路可以應用EN55022標準曲線,如圖6中虛線所示。圖6中上面一條曲線是為考慮EMC設計時的傳導E-MI測試曲線,可以看到干擾強度嚴重超過標準,必須對電路進行相應的抗干擾設計。圖7是參加傳導EMI測試的反激變換電路,圖7中虛線部分是考慮EMC問題而添加的電路部分。

2 優化EMC設計

2.1 輸入側EMC設計

??? 一般開關電源與電網直接相連,高頻開關的兩端產生浪涌電壓,流過一定的浪涌電流,這個電流通過高頻變壓器原邊、直流電容和開關器件形成回路,產生高頻輻射干擾;同時高頻電流流過一次側整流電路,產生的脈沖電壓疊加在電網電壓上,形成差模干擾,對同一線路上的其他設備帶來干擾。如圖8所示,在開關電源的電源輸入端安裝電源濾波器可以起到抑制共模和差模干擾的作用。

??? 從濾除電磁干擾的角度,EMI濾波器實質是一個低通濾波器,對直流至截止頻率(工頻)的信號以最小衰減通過,而對電磁干擾的頻帶給以盡可能高的衰減,通帶與阻帶之間的過渡帶應盡量地陡。

??? 由圖8推導分別得到共模、差模的插入損耗為

???

??? 按前文的分析,理想EMI濾波器應使共模插入損耗(ILCM)最大,而差模插入損耗(ILDM)最小,從圖6可以看出,EMI濾波器在10MHz時噪聲超出標準最大,達到35dB左右,所以,共模噪聲的衰減必須達到40dB,設計時令Rs/RL=50Ω/50Ω,衰減損耗按60dB設計,則有

???

??? 而且根據開關電源產生共模、差模干擾的特點,將整個頻率范圍劃分為3個部分,即

??? 0.15~0.5MHz 差模干擾為主;

??? 0.5~5MHz 差、共模干擾共存;

??? 5~30MHz 共模干擾為主。

??? 對照圖6,發現原電路差模、共模干擾全面超標,但可以看出5~30MHz,頻率范圍內,出現兩個尖峰,應由共模干擾引起,所以,在優化設計EMC時必須加強共模的抑制,即可增加CY的容量來實現。

??? 考慮以上各點因素,取Cx=0.47μF,CY=0.22μF,L=22mH,加入EMI濾波器后電路經過傳導測試符合EN55022標準,如圖6中下方一條曲線所示。

2.2 變壓器原邊關斷尖峰電壓抑制

??? 單片開關電源內部集成的MOSFET的高速開斷,使得高頻變壓器原邊漏感中儲存的能量釋放,在變壓器原邊疊加一個電壓尖峰,使高頻方波波形畸變,甚至由于尖峰電壓全部加在TOPSwitch的D端(漏極)上,可能使芯片損壞。為抑制尖峰電壓,在變壓器原邊繞組并聯由瞬態電壓抑制器(TVS)和超快恢復二極管(SRD)相串聯組成的吸收電路。當MOSFET關斷時,TVS反向擊穿,SRD導通,漏感中的能量沿并聯回路釋放,使得MOS-FET兩端的電壓限定在TVS的擊穿電壓之內。結合圖5的波形可以看出,在開關管關斷瞬間,關斷尖峰電壓疊加在TOPswitch的D端上,使VD達到600V左右(直流高壓450V加上TVS的擊穿電壓200V),TVS鉗位電路導通,漏感能量沿并聯通路釋放,而且由于雜散電容和初級電感形成了諧振電路,產生衰減振蕩,之后,VD回落并穩定在直流高壓水平上。

2.3 輸出二極管關斷尖峰電壓抑制

??? 反激變換電路+5V主輸出電路整流二極管選用SRl640超快恢復二極管(共陰對管),其反向恢復時間trr=35ns,平均整流電流Id=10A,反向峰值電壓VRM=200V。電路工作頻率在100kHz(周期10μs),選用超快恢復二極管可有效降低由于反向恢復電流而形成的關斷電壓尖峰。

??? 另外,并聯RC電路吸收高頻紋波,100Ω的電阻同時作為假負載避免空載時輸出電壓升高。同時電路增加了一階濾波器,其傳遞函數為 在轉折頻率后以-40dB衰減高頻諧波分量,如圖9所示。

在轉折頻率后以-40dB衰減高頻諧波分量,如圖9所示。

??? 由于實際應用中一階LC濾波會在截止頻率附近產生振蕩,所以,要合理選取L及C的參數,使其截止頻率fc小于輸出紋波的最低次諧波分量頻率。

??? 如果輸出電壓紋波達不到要求,可以在輸出側加一級共扼扼流圈以抑制共模干擾傳導至輸出端。

2.4 其他改進措施

??? 1)采用變壓器屏蔽技術,盡量減少其漏感引起的對外輻射噪聲;

??? 2)開關管兩端并接RC網絡,減緩漏源電壓的上升斜率,以減小dv/dt對控制端的影響;

??? 3)對PCB工藝進行改進,使其主電路與控制電路分開,對電磁輻射源和電磁敏感器件要注意隔離,以及合理的接地。

3 實驗結果

??? 經過以上EMC優化設計,基于TOP224Y設計的的反激變換電路實現輸出電壓調整率△Vo/Vo=0.1/5=2%(主輸出+5V,滿載20W,連續72h帶載),達到了預期設計的要求。圖10是輸出電壓直流分量與其交流分量波形。

4 結語

??? 由于電磁兼容已經成為開關電源產業必須考慮的問題,所以,考慮EMC問題要有一定的設計理論依據。本文就噪聲干擾產生的不同途徑,給出抑制差模、共模干擾的濾波器模型,并結合原電路傳導EMI測試曲線存在的問題推算出電路的參數,改進后的電路再次進行傳導EMI測試,證實了插入濾波器的有效性。

??? 在此基礎上,本文還提出了一些改進噪聲干擾的措施,對輸出電壓的紋波幅值和開關漏源電壓峰值起到一定的限制作用。

電子發燒友App

電子發燒友App

評論