是否加屏蔽地線要根據(jù)板上的串?dāng)_/EMI情況來(lái)決定,而且如對(duì)屏蔽地線的處理不好,有可能反而會(huì)使情況更糟。

79、布不同頻率的時(shí)鐘線時(shí)有什么相應(yīng)的對(duì)策?

對(duì)時(shí)鐘線的布線,最好是進(jìn)行信號(hào)完整性分析,制定相應(yīng)的布線規(guī)則,并根據(jù)這些規(guī)則來(lái)進(jìn)行布線。

80、PCB單層板手工布線時(shí),是放在頂層還是底層?

如果是頂層放器件,底層布線。

81、PCB單層板手工布線時(shí),跳線要如何表示?

跳線是PCB設(shè)計(jì)中特別的器件,只有兩個(gè)焊盤(pán),距離可以定長(zhǎng)的,也可以是可變長(zhǎng)度的。手工布線時(shí)可根據(jù)需要添加。板上會(huì)有直連線表示,料單中也會(huì)出現(xiàn)。

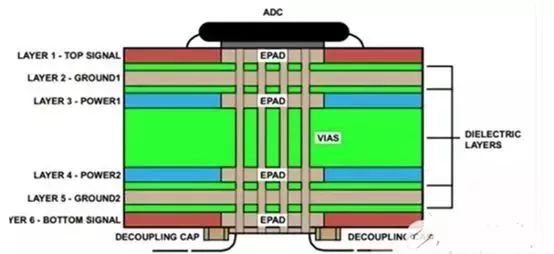

82、假設(shè)一片4層板,中間兩層是VCC和GND,走線從top到bottom,從BOTTOM SIDE流到TOP SIDE的回流路徑是經(jīng)這個(gè)信號(hào)的VIA還是POWER?

過(guò)孔上信號(hào)的回流路徑現(xiàn)在還沒(méi)有一個(gè)明確的說(shuō)法,一般認(rèn)為回流信號(hào)會(huì)從周?chē)罱慕拥鼗蚪与娫吹倪^(guò)孔處回流。一般EDA工具在仿真時(shí)都把過(guò)孔當(dāng)作一個(gè)固定集總參數(shù)的RLC網(wǎng)絡(luò)處理,事實(shí)上是取一個(gè)最壞情況的估計(jì)。

83、“進(jìn)行信號(hào)完整性分析,制定相應(yīng)的布線規(guī)則,并根據(jù)這些規(guī)則來(lái)進(jìn)行布線”,此句如何理解?

前仿真分析,可以得到一系列實(shí)現(xiàn)信號(hào)完整性的布局、布線策略。通常這些策略會(huì)轉(zhuǎn)化成一些物理規(guī)則,約束PCB的布局和布線。通常的規(guī)則有拓?fù)湟?guī)則,長(zhǎng)度規(guī)則,阻抗規(guī)則,并行間距和并行長(zhǎng)度規(guī)則等等。PCB工具可以在這些約束下,完成布線。當(dāng)然,完成的效果如何,還需要經(jīng)過(guò)后仿真驗(yàn)證才知道。

此外,Mentor提供的ICX支持互聯(lián)綜合,一邊布線,一邊仿真,實(shí)現(xiàn)一次通過(guò)。

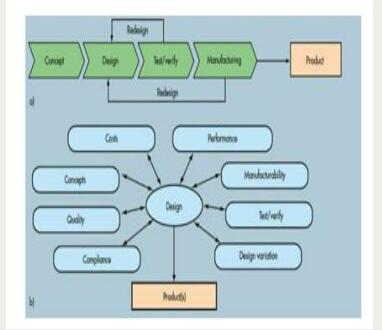

84、怎樣選擇PCB的軟件?

選擇PCB的軟件,根據(jù)自己的需求。市面提供的高級(jí)軟件很多,關(guān)鍵看看是否適合您設(shè)計(jì)能力,設(shè)計(jì)規(guī)模和設(shè)計(jì)約束的要求。刀快了好上手,太快會(huì)傷手。找個(gè)EDA廠商,請(qǐng)過(guò)去做個(gè)產(chǎn)品介紹,大家坐下來(lái)聊聊,不管買(mǎi)不買(mǎi),都會(huì)有收獲。

85、關(guān)于碎銅、浮銅的概念該怎么理解呢?

從PCB加工角度,一般將面積小于某個(gè)單位面積的銅箔叫碎銅,這些太小面積的銅箔會(huì)在加工時(shí),由于蝕刻誤差導(dǎo)致問(wèn)題。從電氣角度來(lái)講,將沒(méi)有合任何直流網(wǎng)絡(luò)連結(jié)的銅箔叫浮銅,浮銅會(huì)由于周?chē)盘?hào)影響,產(chǎn)生天線效應(yīng)。浮銅可能會(huì)是碎銅,也可能是大面積的銅箔。

86、近端串?dāng)_和遠(yuǎn)端串?dāng)_與信號(hào)的頻率和信號(hào)的上升時(shí)間是否有關(guān)系?是否會(huì)隨著它們變化而變化?如果有關(guān)系,能否有公式說(shuō)明它們之間的關(guān)系?

應(yīng)該說(shuō)侵害網(wǎng)絡(luò)對(duì)受害網(wǎng)絡(luò)造成的串?dāng)_與信號(hào)變化沿有關(guān),變化越快,引起的串?dāng)_越大,(V=L*di/dt)。串?dāng)_對(duì)受害網(wǎng)絡(luò)上數(shù)字信號(hào)的判決影響則與信號(hào)頻率有關(guān),頻率越快,影響越大。

87、在PROTEL中如何畫(huà)綁定IC?

具體講,在PCB中使用機(jī)械層畫(huà)邦定圖,IC襯底襯根據(jù)IC SPEC.決定接vccgndfloat,用機(jī)械層print bonding drawing即可。

88、用PROTEL繪制原理圖,制板時(shí)產(chǎn)生的網(wǎng)絡(luò)表始終有錯(cuò),無(wú)法自動(dòng)產(chǎn)生PCB板,原因是什么?

可以根據(jù)原理圖對(duì)生成的網(wǎng)絡(luò)表進(jìn)行手工編輯, 檢查通過(guò)后即可自動(dòng)布線。用制板軟件自動(dòng)布局和布線的板面都不十分理想。網(wǎng)絡(luò)表錯(cuò)誤可能是沒(méi)有指定原理圖中元件封裝;也可能是布電路板的庫(kù)中沒(méi)有包含指定原理圖中全部元件封裝。如果是單面板就不要用自動(dòng)布線,雙面板就可以用自動(dòng)布線。也可以對(duì)電源和重要的信號(hào)線手動(dòng),其他的自動(dòng)。

89、PCB與PCB的連接,通常靠接插鍍金或銀的“手指”實(shí)現(xiàn),如果“手指”與插座間接觸不良怎么辦?

如果是清潔問(wèn)題,可用專用的電器觸點(diǎn)清潔劑清洗,或用寫(xiě)字用的橡皮擦清潔PCB。還要考慮1、金手指是否太薄,焊盤(pán)是否和插座不吻合;2、插座是否進(jìn)了松香水或雜質(zhì);3、插座的質(zhì)量是否可靠。

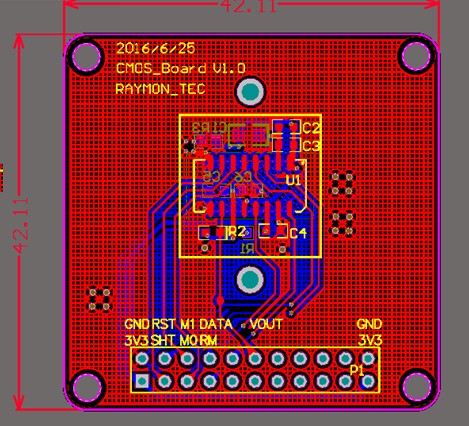

90、如何用powerPCB設(shè)定4層板的層?

可以將層定義設(shè)為

1:no plane+ component(top route)

2:cam plane或split/mixed (GND)

3:cam plane或split/mixed (power)

4:no plane+component(如果單面放元件可以定義為no plane+route)

注意:

cam plane生成電源和地層是負(fù)片,并且不能在該層走線,而split/mixed生成的是正片,而且該層可以作為電源或地,也可以在該層走線(部推薦在電源層和地層走線,因?yàn)檫@樣會(huì)破壞該層的完整性, 可能造成EMI的問(wèn)題) 。將電源網(wǎng)絡(luò)(如3.3V,5V等)在2層的assign中由左邊列表添加到右邊列表,這樣就完成了層定義

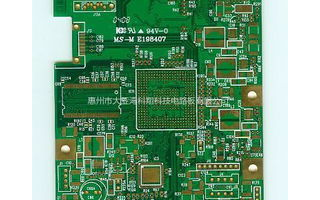

91、PCB中各層的含義是什么?

Mechanical 機(jī)械層:定義整個(gè)PCB板的外觀,即整個(gè)PCB板的外形結(jié)構(gòu)。

Keepoutlayer 禁止布線層:定義在布電氣特性的銅一側(cè)的邊界。也就是說(shuō)先定義了禁止布線層后,在以后的布過(guò)程中,所布的具有電氣特性的線不可以超出禁止布線層的邊界。

Topoverlay 頂層絲印層 & Bottomoverlay 底層絲印層:定義頂層和底的絲印字符,就是一般在PCB板上看到的元件編號(hào)和一些字符。

Toppaste 頂層焊盤(pán)層 & Bottompaste 底層焊盤(pán)層:指我們可以看到的露在外面的銅鉑。

Topsolder 頂層阻焊層 & Bottomsolder 底層阻焊層:與toppaste和bottompaste兩層相反,是要蓋綠油的層。

Drillguide 過(guò)孔引導(dǎo)層:

Drilldrawing 過(guò)孔鉆孔層:

Multiplayer 多層:指PCB板的所有層。

92、在高速PCB中,VIA可以減少很大的回流路徑,但有的又說(shuō)情愿彎一下也不要打VIA,應(yīng)該如何取舍?

分析RF電路的回流路徑,與高速數(shù)字電路中信號(hào)回流還不太一樣。首先,二者有共同點(diǎn),都是分布參數(shù)電路,都是應(yīng)用maxwell方程計(jì)算電路的特性。

然而,射頻電路是模擬電路,有電路中電壓V=V(t),電流I=I(t)兩個(gè)變量都需要進(jìn)行控制,而數(shù)字電路只關(guān)注信號(hào)電壓的變化V=V(t)。因此,在RF布線中,除了考慮信號(hào)回流外,還需要考慮布線對(duì)電流的影響。即打彎布線和過(guò)孔對(duì)信號(hào)電流有沒(méi)有影響。

此外,大多數(shù)RF板都是單面或雙面PCB,并沒(méi)有完整的平面層,回流路徑分布在信號(hào)周?chē)鱾€(gè)地和電源上,仿真時(shí)需要使用3D場(chǎng)提取工具分析,這時(shí)候打彎布線和過(guò)孔的回流需要具體分析;高速數(shù)字電路分析一般只處理有完整平面層的多層PCB,使用2D場(chǎng)提取分析,只考慮在相鄰平面的信號(hào)回流,過(guò)孔只作為一個(gè)集總參數(shù)的R-L-C處理。

93、在設(shè)計(jì)PCB板時(shí),有如下兩個(gè)疊層方案:

疊層1 》信號(hào) 》地 》信號(hào) 》電源+1.5V 》信號(hào) 》電源+2.5V 》信號(hào)

》電源+1.25V 》電源+1.2V》信號(hào) 》電源+3.3V 》信號(hào) 》電源+1.8V

》信號(hào) 》地 》信號(hào)

疊層2 》信號(hào) 》地 》信號(hào) 》電源+1.5V 》信號(hào) 》地 》信號(hào)

》電源+1.25V +1.8V 》電源+2.5V +1.2V 》信號(hào) 》地 》信號(hào)

》電源+3.3V 》信號(hào) 》地 》信號(hào)

哪一種疊層順序比較優(yōu)選?對(duì)于疊層2,中間的兩個(gè)分割電源層是否會(huì)對(duì)相鄰的信號(hào)層產(chǎn)生影響?這兩個(gè)信號(hào)層已經(jīng)有地平面給信號(hào)作為回流路徑。

應(yīng)該說(shuō)兩種層疊各有好處。第一種保證了平面層的完整,第二種增加了地層數(shù)目,有效降低了電源平面的阻抗,對(duì)抑制系統(tǒng)EMI有好處。

理論上講,電源平面和地平面對(duì)于交流信號(hào)是等效的。但實(shí)際上,地平面具有比電源平面更好的交流阻抗,信號(hào)優(yōu)選地平面作為回流平面。但是由于層疊厚度因素的影響,例如信號(hào)和電源層間介質(zhì)厚度小于與地之間的介質(zhì)厚度,第二種層疊中跨分割的信號(hào)同樣在電源分隔處存在信號(hào)回流不完整的問(wèn)題。

94、當(dāng)信號(hào)跨電源分割時(shí),是否表示對(duì)該信號(hào)而言,該電源平面的交流阻抗大?此時(shí),如果該信號(hào)層還有地平面與其相鄰,即使信號(hào)和電源層間介質(zhì)厚度小于與地之間的介質(zhì)厚度,信號(hào)是否也會(huì)選擇地平面作為回流路徑?

沒(méi)錯(cuò),這種說(shuō)法是對(duì)的,根據(jù)阻抗計(jì)算公式,Z=squa(L/C), 在分隔處,C變小,Z增大。當(dāng)然此處,信號(hào)還與地層相鄰,C比較大,Z較小,信號(hào)優(yōu)先從完整的地平面上回流。但是,不可避免會(huì)在分隔處產(chǎn)生阻抗不連續(xù)。

95、在使用protel 99se軟件設(shè)計(jì),處理器的是89C51,晶振12MHZ 系統(tǒng)中還有一個(gè)40KHZ的超聲波信號(hào)和800hz的音頻信號(hào),此時(shí)如何設(shè)計(jì)PCB才能提供高抗干擾能力?

對(duì)于89C51等單片機(jī)而言,多大的信號(hào)的時(shí)候能夠影響89C51的正常工作?除了拉大兩者之間的距離之外,還有沒(méi)有其他的技巧來(lái)提高系統(tǒng)抗干擾的能力?

PCB設(shè)計(jì)提供高抗干擾能力,當(dāng)然需要盡量降低干擾源信號(hào)的信號(hào)變化沿速率,具體多高頻率的信號(hào),要看干擾信號(hào)是那種電平,PCB布線多長(zhǎng)。除了拉開(kāi)間距外,通過(guò)匹配或拓?fù)浣鉀Q干擾信號(hào)的反射,過(guò)沖等問(wèn)題,也可以有效降低信號(hào)干擾。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論