二、Cadence PCB editor繪制PCB板

步驟:焊盤設計,零件封裝→創建電路板,機械結構尺寸層疊結構預定義→導入網表→設定電器規則線寬線距→布局布線→布線后調整零件編號,絲印,DRC檢查→設計輸出gerber文件Drill文件圖紙

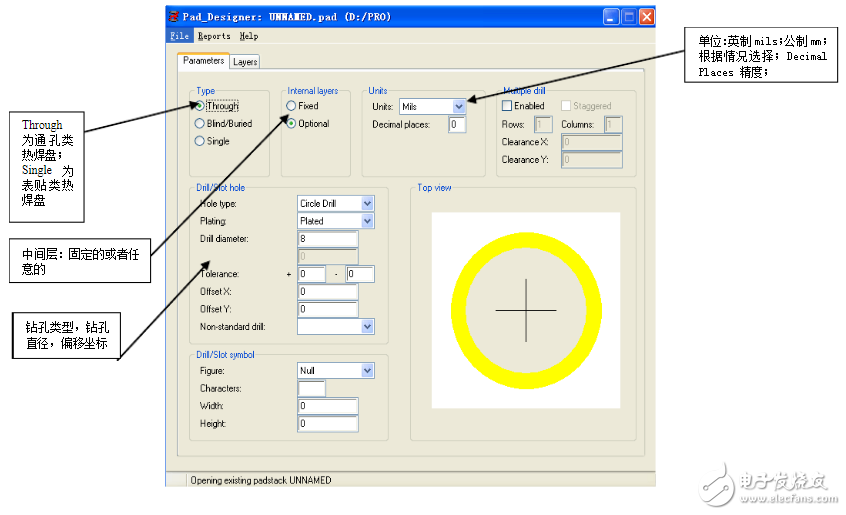

1、Cadence SPB15.7 Pad Designer畫電子元器件的焊盤;

(1)File--》New創建文件

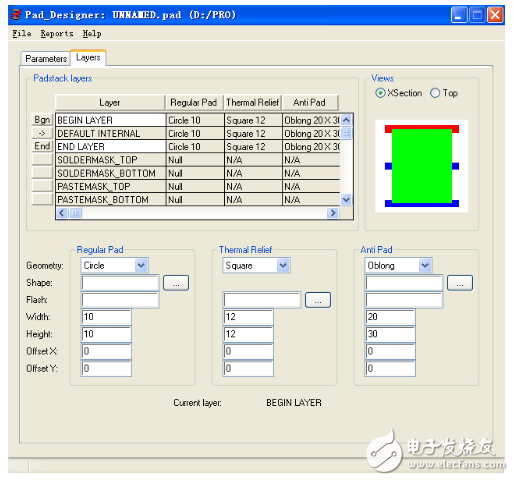

2)層的定義:BEGIN Layer(Top)層:REGULAR-PAD < THERMAL-PAD = ANTI-PAD END LAYER(同BEGIN,常用copy begin layer, then paste it)

TOP SOLDERMASK:只定義REGULAR-PAD ,大于(Begin layer層regular-pad,約為1.1~1.2倍)

BOTTOM SOLDERMASK(同Top soldermask,常用Top soldermask, then paste it)

PASTEMASK _TOP(同BEGIN,常用copy begin layer, then paste it) 設置高度,寬度,偏移坐標原點的x,y值;

(3)A:規則的焊盤可以在Geometry中選擇圓形,正方形,長方形,橢圓形等; B:不規則焊盤需要導入設計好的圖形;

圖形通過Allegro PCB Editer設計; File --》new --》shape symbol;

設計好begin層和soldermask_top層的圖形后設置放置路徑setup--user preference editer選擇Design_paths

Cadence PCB editor零件封裝 手工建立元件(主要包含四項:

PIN;Geometry:SilkScreen/Assembly;Areas:Boundary/Height;RefDes:SilkScreen/Display)

注意:元件應放置在坐標中心位置,即(0,0)

(1)、File →new→package symbol

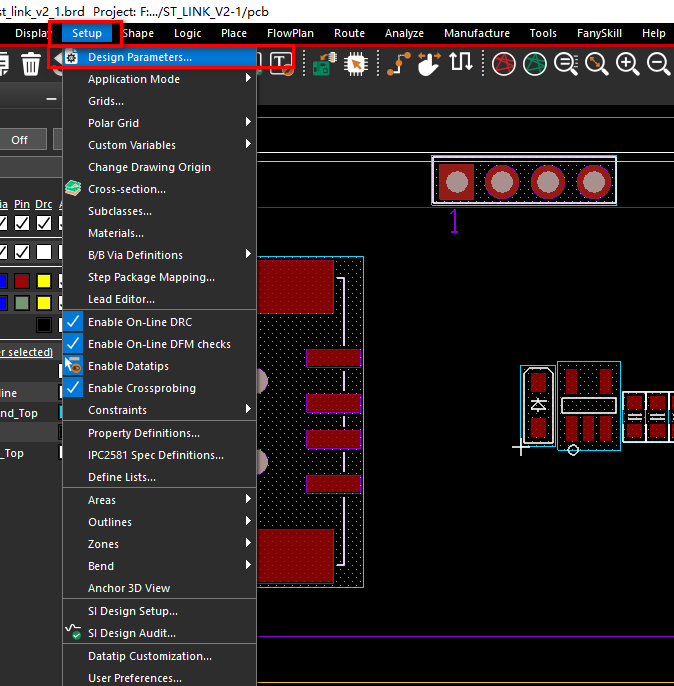

(2)、設定繪圖區域:Setup →Drawing size →Drawing parameter.。。

設置柵格點:setup →Grids;

(3)、添加pin:選擇padstack ,放置。放置前先設置方向,坐標,編號。 (4)、添加元件外形:(Geometery)

*絲印層Silkscreen:AddLine(OptionActive:package geometery;subclass:silkscreen_top) *裝配外框Assembly:AddLine(OptionActive:package geometery;subclass:Assembly_top) (5)、添加元件范圍和高度:(Areas)

*元件范圍Boundary:Setup →Areas →package boundary.。。。

Add Line(OptionActive Class:Package geometry;subclass:Package_bound_top) *元件高度Height:Setup →Areas →package Height.。。。

Add Line(OptionActive Class:Package geometry;subclass:Package_bound_top) (6)、添加封裝標志:(RefDes)LayoutLabelsResDs.。。)

*底片用封裝序號(ResDes For Artwork):Pin1附近(。。.RefDes:Silkscreen_Top) *擺放用封裝序號(ResDes For Placement):封裝中心附近(。。.RefDes:Display_Top) *封裝中心點(Body center):指定封裝中心位置(Add →Text →Package Geometery:Boby_centre)

2、創建電路板

(1)、file→new→broad

(2)、基本設置(同零件封裝基本設置);

(3)、繪制外框(outline):Options→Board geometry:outline

(4)、添加定位孔

(5)、傾斜拐角:(dimension chamfer)

(6)、設定走線區域:shape→polygon.。.option route keepin:all

(7)、設置擺放元件區域:Editz-copy shape.。.options package keepin:all;

(8)、設置不可擺放元件區域:setup→areas→package keepout

(9)、設定不可走線區域:setup→areas route keepout

3、設置約束規則

(1)、Allegro中設置約束規則(Setup→Constraints.。)Spacing Rules和 Physical Rules

(2)、設置默認規范。。.setup→constraints →set standard value

(3)、設置和賦值高級間距規范 : 設定間距規范值:set value

設定間距的Type屬性:Edit→Properties

(4)、設置和賦值高級物理規范 :(基本同上) 設定物理規范值:

(5)、建立設計規范的檢查(setup constraits.。。 )

4、導入網表

File→ Import →logic;

5、布局布線

1、手動擺放元件:Placemanually.。。。。。

查看元件屬性:DisplayElemant;;FindComps;單擊要查看屬性的元件

2、自動擺放元件:PlaceQuick Place.。。。。。 3、隨機擺放:EditMove.。。

4、自動布局:Place auto Place 網格:Top Grid.。

設置元件進行自動布局的屬性:EditProperties Find 。.more.。

5、設定Room:

設定Room:add rectangle;options board geometry op room 給Room定義名字;Add ext;options board geometry op room

定義該Room所限制的特性和定義某些元件必須放置在該Room中:

定義Room所限制的特性:Edit Properties;選中Room;Edit properties;Room_type=hard(指定room的元件必須放Room中)

定義放入Room中的元件:Edit properties;

6、擺放調整(Move、Mirror、Spin)

7、交換(swap)(配合原理圖使用,比較少用)

8、未擺放元件報表(ToolReport.。。)

9、已擺放元件報表(ToolReport.。。)

6、Allegro 產生鉆孔文件

(1)、設置鉆孔參數 Manufacture-》NC-》NC Parameters Paraeter file : 參數文件所在路徑(默認nc_param.txt) Output file: 輸出文件內容設置(默認設置就ok) Exellon format鉆孔文件輸出使用的格式

format :2.3

(2表示小數點前面為2位,3表示小數點后面為3位) offset : 輸出的坐標值和pcb的坐標值的差距 coordinates :

絕對坐標和增量坐標 Output units :

輸出的那位英制或公制 leading

(2)、產生鉆孔文件 Manufacture-》NC-》NC Drill.。。 root file name : 鉆孔文件的名字和路徑

Scale factor : 鉆孔比例因子(建議不要設置) Tool sequence : 鉆孔工具遞增或遞減

Auto tool select :自動選擇工具 Drilling :

Layer pair (全為通孔) By layer (有盲孔或埋孔)

(3)Drill、 產生過孔文件

(4)View Log: 查看鉆孔記錄 可能出現的警告: WARNING: Design precision is greater than that of the drill output file data. Data rounding errors are very possible. 解決方案:

Manufacture-》NC-》NC Parameters-》Exellon format-》format : 3.6(報錯原因過孔精度不足,提高過孔精度)

WARNING: This design contains 1 slot holes that can NOT be drilled. They can be processed by NC routing instead. 解決方案: Manufacture-》NC-》NC route(產生不規則鉆孔,警告可忽略)產生rou文件 (5)產生鉆孔表 Manufacture-》NC-》NC Legend

相關資料下載推薦>>>>>>>>利用Cadence Allegro進行PCB級的信號完整性仿真

電子發燒友App

電子發燒友App

評論