protel PCB設(shè)計(jì)使用手冊(cè)

一、板框?qū)Ш疆?dāng)我們?cè)O(shè)計(jì)了原理圖,生成了網(wǎng)表,下一步就要進(jìn)行

2010-04-26 16:12:57 3075

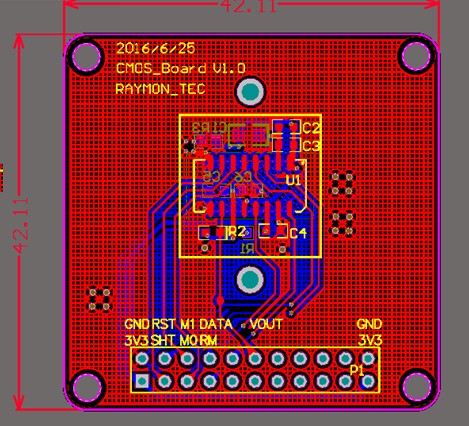

3075 本章旨在說(shuō)明如何生成電路原理圖、把設(shè)計(jì)信息更新到 PCB 文件中以及在 PCB中布線和生成器件輸出文件。并且介紹了工程和集成庫(kù)的概念以及提供了 3D PCB開發(fā)環(huán)境的簡(jiǎn)要說(shuō)明。歡迎使用 Altium

2019-05-16 09:48:00

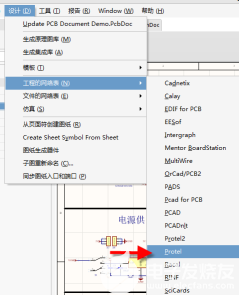

在Altium Designer中,由網(wǎng)絡(luò)表生成PCB具體操作如下:1.在PCB環(huán)境操作菜單中的Projects>Show Differences。

2019-07-24 06:58:29

PCB中導(dǎo)入由PROTEL生成的網(wǎng)絡(luò)表后,PCB中竟丟失一些元件,,怎么回事?

2013-05-27 11:47:37

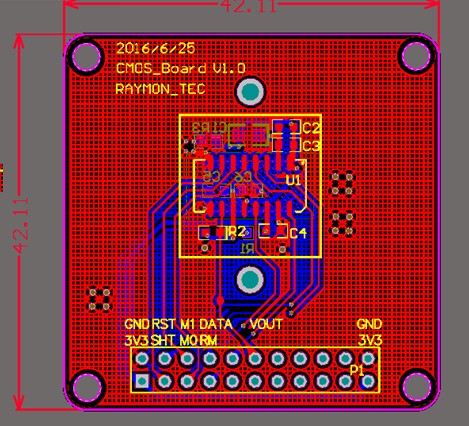

的完整性、回路的控制等多重技術(shù)手段,實(shí)現(xiàn)對(duì)PCB的完整控制,來(lái)為客戶提供PCB設(shè)計(jì)服務(wù)。 您要準(zhǔn)備的: 1:完整的原理圖(原理圖PDF與網(wǎng)表) 2:板子結(jié)構(gòu)圖 3:元件封裝或元件器規(guī)格書

2013-03-26 14:52:54

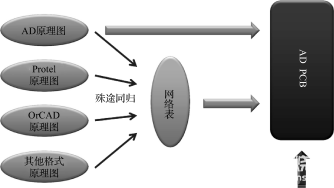

8.2.1網(wǎng)表網(wǎng)表也稱網(wǎng)絡(luò)表,顧名思義,就是網(wǎng)絡(luò)連接和聯(lián)系的表示,其內(nèi)容主要是電路圖中各個(gè)元件類型、封裝信息、連接流水序號(hào)等數(shù)據(jù)信息。在使用Altium]

2020-04-24 08:00:00

PCB設(shè)計(jì)軟件allegro藍(lán)牙音箱案例實(shí)操講解,以藍(lán)牙音箱為案例將PCB設(shè)計(jì)基礎(chǔ)知識(shí)融進(jìn)實(shí)際案例中,通過(guò)操作過(guò)程講解PCB設(shè)計(jì)軟件功能及實(shí)用經(jīng)驗(yàn)技巧,本文著重講解網(wǎng)表導(dǎo)入的常見(jiàn)錯(cuò)誤,減少操作失誤

2018-08-06 11:05:50

PCB設(shè)計(jì)審核表。

2012-08-04 10:32:37

`PCB設(shè)計(jì)軟件allegro藍(lán)牙音箱案例實(shí)操講解,以藍(lán)牙音箱為案例將PCB設(shè)計(jì)基礎(chǔ)知識(shí)融進(jìn)實(shí)際案例中,通過(guò)操作過(guò)程講解PCB設(shè)計(jì)軟件功能及實(shí)用經(jīng)驗(yàn)技巧,全文著重講解網(wǎng)表導(dǎo)出導(dǎo)入和封裝路徑設(shè)置

2018-07-31 14:15:07

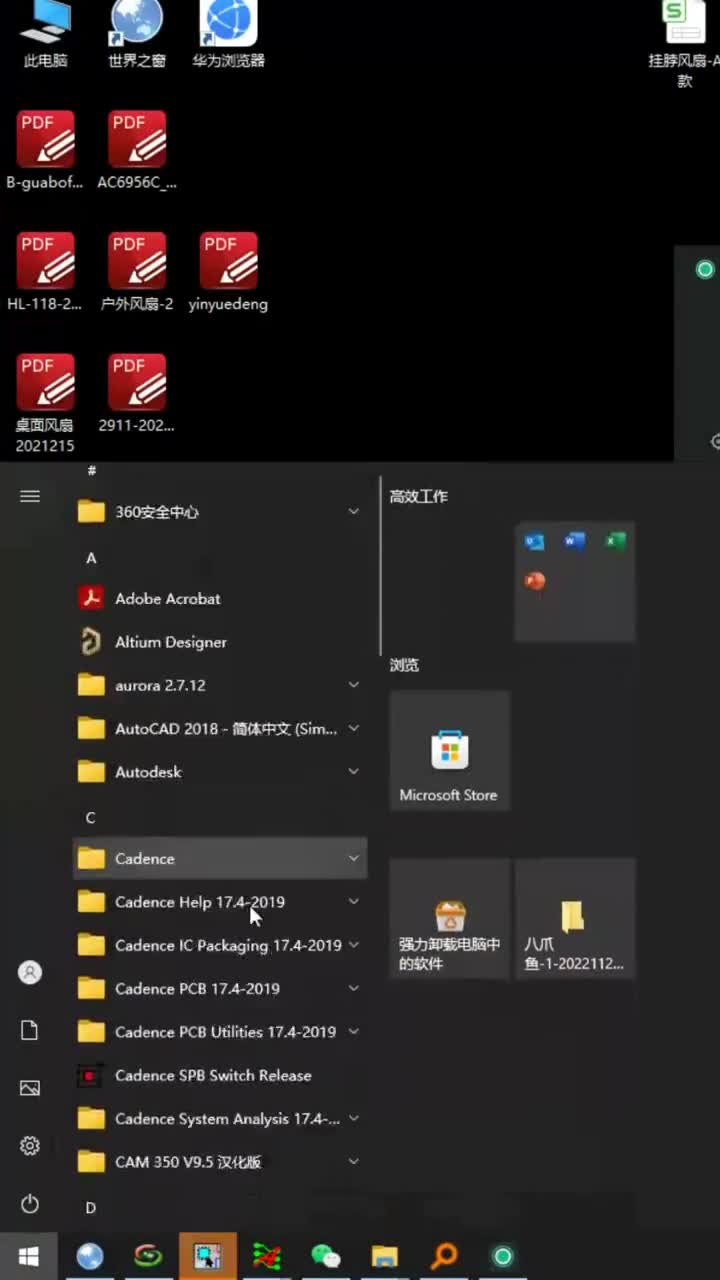

多年的PCB專職設(shè)計(jì)經(jīng)驗(yàn),主要使用的軟件有Cadence(Allegro)、PADS(PowerPCB)、Altium Designer(PROTEL)、CAM350,可以設(shè)計(jì)2-20層板,對(duì)模電

2018-01-03 08:58:31

`<font face="Verdana">Protel 99 PCB設(shè)計(jì)經(jīng)驗(yàn)談</font><br/>`

2009-03-31 11:50:55

Protel99SE PCB設(shè)計(jì)經(jīng)驗(yàn)談

2020-05-07 09:18:23

大多數(shù)器件。eMtri文件中包含有這三項(xiàng)就足夠了。有了第三方網(wǎng)表和設(shè)備描述文件。我們就可以將Protel中原理圖設(shè)計(jì)以網(wǎng)表形式代入到Cadence PCB設(shè)計(jì)軟件中,接下來(lái),設(shè)計(jì)師就可以借助

2018-09-10 16:28:07

pcb圖怎么直接導(dǎo)出網(wǎng)表

2016-06-17 10:40:09

如題:pcb沒(méi)有網(wǎng)表能鋪銅鋪地嗎?

2011-05-02 11:15:52

protel99se可以用pcb生成網(wǎng)絡(luò)表嗎?可以的話怎么操作?

2011-11-17 10:29:50

在生成網(wǎng)表時(shí)報(bào)Error,【ALG0030】Unable to read design "d:\PCB\test\test.dsn"為什么呢,請(qǐng)高手說(shuō)明,謝謝

2013-03-26 16:04:00

生成網(wǎng)表出問(wèn)題,,求助!

2017-06-14 13:00:51

AD6中加載網(wǎng)表生成PCB

2015-12-20 13:08:20

AD9在原理圖繪制完之后如何生成網(wǎng)表文件?在PROTEL99SE里面我就可以看到相關(guān)選項(xiàng) 設(shè)計(jì)\GREATE NET,AD9就沒(méi)有這個(gè)選項(xiàng),另外AD9里面也沒(méi)有電氣規(guī)則檢測(cè)選項(xiàng)。

2012-12-25 10:16:31

本帖最后由 菜鳥級(jí)別 于 2015-9-7 22:04 編輯

AD生成OrCad/PCB2網(wǎng)表,第一次導(dǎo)入allgero沒(méi)問(wèn)題,但是更新原理圖(有添加元件)重新生成網(wǎng)表,再導(dǎo)入allegro,沒(méi)有報(bào)錯(cuò),allegro中的元件清單還是和之前的一樣,沒(méi)有變化,請(qǐng)高手幫忙解釋下。

2015-09-07 21:31:40

,Orcad軟件的第三方網(wǎng)表導(dǎo)入PCB文件,是需要導(dǎo)入之前就要指定好封裝庫(kù)的路徑,所有的封裝都需要之前處理好,指定好路徑,才可以導(dǎo)入,第一方網(wǎng)表是不用的,沒(méi)有封裝可以先將網(wǎng)表導(dǎo)入到PCB中,再去制作封裝

2020-09-07 17:26:43

在生成網(wǎng)表文件時(shí)一直提示這兩個(gè)錯(cuò)誤,怎么解決的,求大神指導(dǎo)

2019-02-21 03:23:31

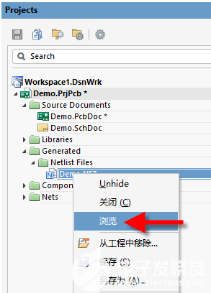

的圖標(biāo),如下圖所示,即可產(chǎn)生網(wǎng)標(biāo)。l Allegro第一方網(wǎng)表如上圖操作以后。彈出以下界面,選擇PCB Editor,然后點(diǎn)擊確定,即可生成Allegro第一方網(wǎng)表,網(wǎng)表的形式會(huì)已Allegro文件夾的方式存在于當(dāng)前原理圖的根目錄下。(圖文詳解見(jiàn)附件)

2019-08-26 17:46:14

本帖最后由 糖果. 于 2016-12-19 15:22 編輯

Altium Designer13.3.4導(dǎo)出網(wǎng)表,allegro16.6通過(guò)other導(dǎo)入導(dǎo)入后出現(xiàn)error生成了device,setup中路徑已添加,求問(wèn)如何解決

2016-12-19 14:32:45

第一個(gè)可以生成網(wǎng)表,這是第二個(gè)不能生成網(wǎng)表。查了一下是器件屬性Device 幾個(gè)器件重復(fù),但第一例子器件device重復(fù)就可以導(dǎo)出網(wǎng)表,不知道為什么?使用的均為orcad下PCB Editor 導(dǎo)出

2019-03-04 07:35:18

allegro第三方生成網(wǎng)表如何實(shí)現(xiàn)與allegro pcb交互設(shè)計(jì)

2014-10-28 10:37:14

cadence allegro 16.5軟件生成網(wǎng)表時(shí)出現(xiàn)這些,求大神給予解答

2015-12-16 13:32:22

cadence16.6生成網(wǎng)表后原理圖與PCB不能交互,交互功能勾選了,原理圖改網(wǎng)絡(luò)重新生成網(wǎng)表PCB的網(wǎng)絡(luò)也會(huì)相應(yīng)改過(guò),PCB選擇器件高亮原理圖相應(yīng)的也會(huì)有關(guān)聯(lián),但是在原理圖選擇元器件PCB不會(huì)

2021-09-09 17:10:24

向各位大牛請(qǐng)教下,design entry cis在輸出網(wǎng)表時(shí)管腳名重復(fù)報(bào)錯(cuò),像這種報(bào)錯(cuò)應(yīng)該不會(huì)影響到網(wǎng)表輸出吧?為什么我的網(wǎng)表沒(méi)能輸出

2015-12-09 11:09:21

以下界面,選擇PCB Editor,然后點(diǎn)擊確定,即可生成Allegro第一方網(wǎng)表,網(wǎng)表的形式會(huì)已Allegro文件夾的方式存在于當(dāng)前原理圖的根目錄下。3、Allegro第三方網(wǎng)表如上圖操作以后,彈出

2018-11-05 15:04:04

power pcb2007 導(dǎo)入orcad網(wǎng)表后元件的值沒(méi)有求指教啊是什么問(wèn)題啊?

2012-04-18 17:15:07

少的),如果+3.3V全部更名為+3.3V_P ,則不顯示+3.3V_P~~這個(gè)問(wèn)題應(yīng)該怎么解決呢~~(其他節(jié)點(diǎn)都正常,如+5V),由于生成網(wǎng)表沒(méi)有報(bào)錯(cuò),生成PCB后可以看出+3.3V節(jié)點(diǎn)在PCB中用GND來(lái)代替了,即本來(lái)電容兩端是+3.3V和GND,現(xiàn)在都是GND了~

2011-12-30 15:20:26

本帖最后由 Goodtimes 于 2020-6-22 08:56 編輯

【Altium】PCB設(shè)計(jì)軟件Altium Designer10.0安裝包+破解文件 網(wǎng)盤分享地址:鏈接:https://pan.baidu.com/s/1lnDSsIsGKx2McuqZaVUT_A提取碼:3vl0

2019-03-25 17:29:18

本帖最后由 Goodtimes 于 2020-6-22 08:55 編輯

【Altium】PCB設(shè)計(jì)軟件Altium Designer13安裝包+破解文件 網(wǎng)盤分享地址:鏈接:https://pan.baidu.com/s/1acsa_EGWhbmqtd_Pt_r9fg提取碼:mn52

2019-03-26 09:35:10

本帖最后由 Goodtimes 于 2020-6-22 08:55 編輯

【Altium】PCB設(shè)計(jì)軟件Altium Designer14安裝包+破解文件 網(wǎng)盤分享地址:鏈接:https://pan.baidu.com/s/1-eXuglgNwc9R-5tGujG3Vw提取碼:4oe7

2019-03-26 09:36:46

本帖最后由 Goodtimes 于 2020-6-22 08:57 編輯

【Altium】PCB設(shè)計(jì)軟件Altium Designer15(AD15.0.7)更新、破解、漢化安裝包 網(wǎng)盤

2019-03-24 11:27:39

本帖最后由 Goodtimes 于 2020-6-22 08:55 編輯

【Altium】PCB設(shè)計(jì)軟件Altium Designer16(AD16.1.12)更新、破解、漢化安裝包 網(wǎng)盤

2019-03-26 09:44:15

本帖最后由 Goodtimes 于 2020-6-22 08:54 編輯

【Altium】PCB設(shè)計(jì)軟件Altium Designer17(AD17.1.9)更新、破解、漢化安裝包 網(wǎng)盤

2019-03-26 09:45:36

本帖最后由 Goodtimes 于 2020-6-22 08:54 編輯

【Altium】PCB設(shè)計(jì)軟件Altium Designer18(AD18.1.7)更新、破解、漢化安裝包 網(wǎng)盤

2019-03-26 09:47:10

本帖最后由 Goodtimes 于 2020-6-22 08:53 編輯

【Altium】PCB設(shè)計(jì)軟件Altium Designer19(AD19.0.10)更新、破解、漢化安裝包 網(wǎng)盤

2019-03-26 09:48:44

【Altium】PCB設(shè)計(jì)軟件Altium Designer6.9安裝包+破解文件 網(wǎng)盤分享地址:鏈接:https://pan.baidu.com/s/1F3JiAaPwG_LahoCCY3_fQw

2019-03-25 17:20:46

本帖最后由 Goodtimes 于 2020-6-22 08:56 編輯

【Altium】PCB設(shè)計(jì)軟件Altium Designer9.4安裝包+破解文件 網(wǎng)盤分享地址:鏈接:https://pan.baidu.com/s/1rG3ZqSvmCx_VRA6eFkYvQw提取碼:6sge

2019-03-25 17:27:16

匯總了Altium Designer的各個(gè)版本,可能還有版本缺失,后期會(huì)補(bǔ)上,歡迎大家在樓下留言,希望能幫助到大家~【Altium】PCB設(shè)計(jì)軟件Altium Designer6.9安裝包+破解文件

2019-03-26 10:44:56

本帖最后由 Goodtimes 于 2020-6-22 08:57 編輯

【Protel】PCB設(shè)計(jì)入門軟件Protel99SE增強(qiáng)工具網(wǎng)盤分享地址:鏈接:https://pan.baidu.com/s/1vcstlSID3YamAZUHHdvPsw 提取碼:o799

2019-03-25 16:20:30

本帖最后由 Goodtimes 于 2020-6-22 08:56 編輯

【Protel】PCB設(shè)計(jì)入門軟件Protel99SE免費(fèi)下載網(wǎng)盤分享(安裝包+破解漢化+SP6插件)https

2019-03-25 16:28:31

本帖最后由 Goodtimes 于 2020-6-22 08:57 編輯

【Protel】PCB設(shè)計(jì)入門軟件Protel99SE視頻教程網(wǎng)盤分享地址:鏈接:https://pan.baidu.com/s/1aMQiuEZCtINPDrTVmx-fcA 提取碼:mk0k

2019-03-25 16:22:13

實(shí)戰(zhàn)設(shè)計(jì)的過(guò)程,涉及到的每一個(gè)器件是怎么PCB布局?jǐn)[放?每一根線怎么拉線?都會(huì)一一給大家呈現(xiàn)。希望大家學(xué)有所成!福利送不停,8月4日直播預(yù)告《PCB設(shè)計(jì)流程、網(wǎng)表導(dǎo)入及常見(jiàn)導(dǎo)入錯(cuò)誤解決辦法》——第一期

2021-07-29 14:00:38

oracd capture cis 生成網(wǎng)表時(shí),我確定所有路徑都是沒(méi)問(wèn)題的,而且也沒(méi)有非法字符,但是按了creat netlist的確定時(shí),一直不出現(xiàn)這個(gè)窗口,也沒(méi)有生成任何bat文件。后來(lái)查看

2016-06-25 13:02:03

案例就表示了網(wǎng)表已經(jīng)成功導(dǎo)入,一共有451個(gè)器件,現(xiàn)在這些器件全部在后臺(tái),并未放置到PCB中,我們要做的就是將這些器件放到PCB中,進(jìn)行PCB設(shè)計(jì); Allegro軟件導(dǎo)入網(wǎng)表以后,為什么在PCB板

2020-09-07 17:23:05

生成pads2k網(wǎng)表的時(shí)候顯示這種錯(cuò)誤

2019-06-20 05:35:09

編號(hào)。 6.DRC檢查。 7.全局更改為原理圖添加封裝。 8.輸出元件清單。 9.生成網(wǎng)表。 10.PCB設(shè)計(jì)設(shè)置。 11.板框設(shè)置。 12.設(shè)置安裝孔。 13.導(dǎo)入網(wǎng)表。 14.

2019-05-06 17:16:11

PCB設(shè)計(jì)中網(wǎng)表導(dǎo)入常見(jiàn)錯(cuò)誤的查找:1、打開netin。log文件2、查找關(guān)鍵字error,如下圖:網(wǎng)表常見(jiàn)錯(cuò)誤查找1網(wǎng)表常見(jiàn)錯(cuò)誤查找2網(wǎng)表常見(jiàn)錯(cuò)誤查找3網(wǎng)表導(dǎo)入的常見(jiàn)錯(cuò)誤處理:1、器件沒(méi)指定PCB

2017-01-10 10:51:59

嗨,Vivado的新手問(wèn)題;是否有可能為后綜合模擬和/或后PAR網(wǎng)表模擬生成VHDL或Verilog網(wǎng)表?謝謝,埃里克

2019-11-11 07:33:05

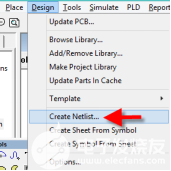

用OrCAD畫好原理圖后我們需要導(dǎo)出網(wǎng)表便于后續(xù)導(dǎo)入Allego畫PCB(AD這點(diǎn)不同,可直接生成PCB文件)。Tools-Create Netlist,出現(xiàn)以下界面:點(diǎn)擊確定即可生成第一方網(wǎng)表。選擇Other項(xiàng):

2022-02-15 07:33:39

嗨, 我有一個(gè)edif網(wǎng)表,我必須將其轉(zhuǎn)換為ngc網(wǎng)表。我該怎么做謝謝poorna

2019-10-24 08:12:41

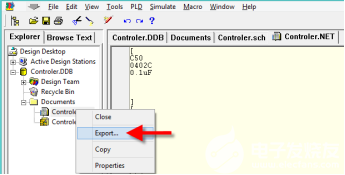

一.第三方網(wǎng)表的導(dǎo)出 點(diǎn)擊后(生成的netlist就是第三方網(wǎng)表,第三方網(wǎng)表的格式有.txt .tel等多種格式,但都能用記事本打開) 點(diǎn)擊保存,得到netlist.txt文檔,即第三方網(wǎng)表二

2016-09-14 10:32:32

嗨,大家好 我有一個(gè)專為virtex 2 pro設(shè)計(jì)的edf網(wǎng)表。但是現(xiàn)在我正在研究kintex 7.我有什么方法可以使用網(wǎng)表進(jìn)行kintex 7 ??請(qǐng)幫幫我..謝謝Karthik R.

2020-04-21 08:42:38

實(shí)時(shí)鉆頭表有哪些特征?在PCB設(shè)計(jì)中怎樣去放置實(shí)時(shí)鉆表?

2021-07-22 09:27:53

各位大俠,我在用orcad生成網(wǎng)表時(shí),軟件無(wú)法正常退出,但其實(shí)網(wǎng)表文件已經(jīng)生成了,這個(gè)怎么解決?謝謝本來(lái)一直沒(méi)有理會(huì)這個(gè)問(wèn)題,直接那生成的網(wǎng)表去布局布線,但現(xiàn)在需要back annonate,這個(gè)步驟只能在網(wǎng)表正常生成后做,所以需要急需解決這個(gè)問(wèn)題。

2011-12-18 11:14:55

454.4.2庫(kù)路徑的全局指定 464.5網(wǎng)表的生成及PCB元器件的導(dǎo)入 484.5.1Protel 網(wǎng)表生成 484.5.2Altium 網(wǎng)表生成 484.6PCB元器件的導(dǎo)入 494.6.1直接

2016-03-05 23:44:33

請(qǐng)問(wèn)在生成網(wǎng)表文件時(shí)出現(xiàn)錯(cuò)誤 Port has a type which is inconsistent with other ports on the net USART_RX SCHEMATIC1, STM3210E-MCU(2.60, 2.90)是怎么回事啊?我該怎樣修改,謝謝!

2013-01-07 11:02:15

如圖所示,不知道為什么從元理圖導(dǎo)入PCB時(shí),總提示網(wǎng)絡(luò)連接不對(duì)(如圖上紅框內(nèi))元理圖也沒(méi)錯(cuò),PCB封裝也沒(méi)錯(cuò),但就不知道怎么回事,感覺(jué)是網(wǎng)表的問(wèn)題,不是很理解。希望各位大俠幫個(gè)忙啊!

2012-02-09 17:36:22

本人現(xiàn)在轉(zhuǎn)行做電源PCB LAYOUT,現(xiàn)跪求求電源PCB設(shè)計(jì)的經(jīng)驗(yàn)、資料等相關(guān)方面的知識(shí)。另外Altium Designer跟PROTEL 99SE有什么差別?

2011-08-06 12:08:49

用PADS生成網(wǎng)表時(shí)出現(xiàn)的問(wèn)題,求高手解答,謝謝。PCB Net List Errors Report - FIRST.sch - Sat Feb 11 19:51:39

2012-02-11 20:08:33

電源布局、網(wǎng)口電路、音頻走線的PCB設(shè)計(jì)

2021-03-04 06:10:24

一.第三方網(wǎng)表的導(dǎo)出 點(diǎn)擊后(生成的netlist就是第三方網(wǎng)表,第三方網(wǎng)表的格式有.txt .tel等多種格式,但都能用記事本打開) 點(diǎn)擊保存,得到netlist.txt文檔,即第三方網(wǎng)表二

2016-09-16 16:16:58

請(qǐng)教pads網(wǎng)絡(luò)表咋轉(zhuǎn)換為protel網(wǎng)表?

2011-09-01 19:28:02

怎么將ORCAD原理圖輸出網(wǎng)表?PADS-PCB導(dǎo)入網(wǎng)表?然后PCB輸出CAM? 越詳細(xì)越好啊。

2011-09-29 22:38:31

pads如何生成IPC網(wǎng)表與gerber比對(duì)?

2019-04-16 07:35:16

請(qǐng)問(wèn)如何在allegro中導(dǎo)入orcad 生成的網(wǎng)表?誰(shuí)知道詳細(xì)的步驟,如何把DSN導(dǎo)成NETLIST的形式呢?請(qǐng)高手幫幫呀。。

2011-09-29 22:34:58

本人現(xiàn)在轉(zhuǎn)行做電源PCB LAYOUT,現(xiàn)跪求電源PCB設(shè)計(jì)的經(jīng)驗(yàn)、資料等相關(guān)方面的知識(shí)。另外Altium Designer跟PROTEL 99SE有什么差別?

2011-08-06 12:10:17

一、PCB設(shè)計(jì)前期處理概述PCB設(shè)計(jì)前期處理,包含網(wǎng)表的調(diào)入,添加外形結(jié)構(gòu)以及添加禁布區(qū)域的信息。網(wǎng)表是原理圖設(shè)計(jì)和PCB設(shè)計(jì)之間的橋梁,網(wǎng)表里主要記錄的是元件電氣連接關(guān)系和各個(gè)元件的封裝類型以及

2019-10-14 20:48:18

前言:上期主要介紹了PCB設(shè)計(jì)的前處理中“原理圖網(wǎng)表”的生成方法,那么網(wǎng)表導(dǎo)入時(shí)有哪些常見(jiàn)錯(cuò)誤呢?一、網(wǎng)表導(dǎo)入常見(jiàn)錯(cuò)誤查找: 1、打開netin。log文件2、查找關(guān)鍵字error,如下圖: 查找1

2017-03-21 11:05:15

Cadence工具包含IC設(shè)計(jì)組件和PCB設(shè)計(jì)組件,從現(xiàn)在開始學(xué)習(xí)PCB設(shè)計(jì)組件,并對(duì)比曾經(jīng)的Altium(Protel)

2019-11-02 09:01:00 2786

2786

@[TOC]PCB設(shè)計(jì)經(jīng)驗(yàn)(1)#PCB設(shè)計(jì)規(guī)則#PCB走線經(jīng)驗(yàn)#快捷鍵的使用#易犯錯(cuò)誤匯總

2021-11-05 18:35:59 19

19

??

??

??????

??????

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論