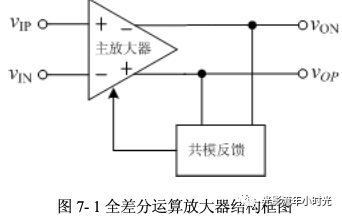

全差分運(yùn)算放大器就是一種具有差分輸入,差分輸出結(jié)構(gòu)的運(yùn)算放大器。

2023-09-25 17:34:56 3116

3116

這種全差分放大器能不能使用G=+1高速運(yùn)算放大器作為buffer使用,增加AD8132的負(fù)載能力

2023-11-20 07:52:37

信號(hào),也可以輸入共模信號(hào),共模信號(hào)大部分來自噪聲,最核心的愿景是:共模被抵消,差模被放大。四、輸入電壓范圍(Vin或Vcm)運(yùn)算放大器輸入范圍比較復(fù)雜,理論上來講,同相端和反相端模擬輸入在電源的正軌到

2021-12-07 07:00:00

描述差分運(yùn)算放大器板運(yùn)算放大器在配置為“差分”模式時(shí)可用于許多有趣的事情——包括模擬計(jì)算器、簡(jiǎn)單的平衡麥克風(fēng)前置放大器和原始組件曲線跟蹤器。

2022-06-28 07:20:14

平衡的電路,兩個(gè)集電極電壓之間的零差。這被稱為共模操作,當(dāng)輸入為零時(shí),放大器的共模增益為輸出增益。運(yùn)算放大器還具有一個(gè)低阻抗的輸出(盡管有一個(gè)輸出帶有一個(gè)額外的差分輸出),該輸出以一個(gè)公共接地端為基準(zhǔn)

2020-12-25 09:05:21

運(yùn)算放大器共模抑制(CMR)的問題出在哪里呢?我們?cè)撛趺慈ソ鉀Q這個(gè)問題?

2021-04-07 06:55:35

信號(hào),也可以輸入共模信號(hào),共模信號(hào)大部分來自噪聲,最核心的愿景是:共模被抵消,差模被放大。四、輸入電壓范圍(Vin或Vcm)運(yùn)算放大器輸入范圍比較復(fù)雜,理論上來講,同相端和反相端模擬輸入在電源的正軌到

2021-08-25 07:00:00

運(yùn)算放大器的電路結(jié)構(gòu)運(yùn)算放大器的內(nèi)部電路結(jié)構(gòu)如下所示。一般由輸入段、增益段、輸出段等3段電路構(gòu)成。輸入段由差分放大段構(gòu)成,用于放大兩個(gè)引腳間的電壓差。 另外,同相信號(hào)成分(引腳間無電位差,輸入相等

2019-05-27 02:48:52

地”的,當(dāng)使用單端輸入信號(hào)時(shí),就會(huì)產(chǎn)生共模輸入信號(hào),即使使用高共模抑制比的運(yùn)算放大器,也還是會(huì)有共模輸出的。 所以,一般在使用時(shí),都會(huì)盡量采用反相輸入接法。 (2)正相是振蕩器,反相才能穩(wěn)定放大器

2019-07-21 22:54:12

范圍從-45℃到125℃零漂移運(yùn)放GS833X系列高精密零漂移運(yùn)算放大器采用臺(tái)積電先進(jìn)的CMOS工藝及全新的斬波電路結(jié)構(gòu)設(shè)計(jì),可提供極低的輸入失調(diào)電壓(10μV,最大值)同時(shí)隨時(shí)間推移和溫度變化輸入

2020-04-27 10:35:17

運(yùn)算放大器有哪幾類?折疊式共源共柵全差分運(yùn)算放大器會(huì)受到哪些影響?

2021-04-07 06:29:07

RF設(shè)計(jì)領(lǐng)域,回歸到了全差分結(jié)構(gòu),也開啟了在差分信號(hào)鏈接口中的新應(yīng)用領(lǐng)域。如何得心應(yīng)手地應(yīng)用運(yùn)算放大器,快速、準(zhǔn)確地設(shè)計(jì)滿足需求的電路系統(tǒng),是工程師們必須認(rèn)真面對(duì)的問題。本書出自全球領(lǐng)先的半導(dǎo)體公司

2017-06-09 17:38:49

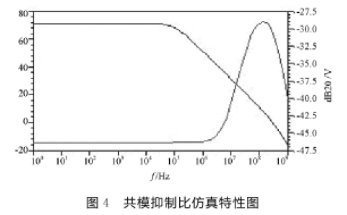

衡量運(yùn)算放大器對(duì)作用在兩個(gè)輸入端的相同交流信號(hào)的抑制能力,是差模開環(huán)增益除以共模開環(huán)增益的函數(shù)。CMRAC通常定義在特定頻率和整個(gè)直流共模電壓范圍:4. 增益帶寬積 (GBW) 增益帶寬積AOL

2009-09-25 10:42:49

類配置的低失真結(jié)合在一起。 摘要標(biāo)準(zhǔn)的運(yùn)算放大器架構(gòu)由三個(gè)相互連接的子電路組成:差分輸入級(jí),高增益級(jí)和輸出級(jí)。741運(yùn)算放大器的輸入級(jí)具有一個(gè)差分對(duì)和一個(gè)有源負(fù)載。高增益級(jí)包括一個(gè)射極跟隨器,一個(gè)有源負(fù)載的共射極放大器和一個(gè)補(bǔ)償電容器。輸出級(jí)是AB類放大器。

2020-09-16 10:19:24

類配置的低失真結(jié)合在一起。 摘要標(biāo)準(zhǔn)的運(yùn)算放大器架構(gòu)由三個(gè)相互連接的子電路組成:差分輸入級(jí),高增益級(jí)和輸出級(jí)。741運(yùn)算放大器的輸入級(jí)具有一個(gè)差分對(duì)和一個(gè)有源負(fù)載。高增益級(jí)包括一個(gè)射極跟隨器,一個(gè)有源負(fù)載的共射極放大器和一個(gè)補(bǔ)償電容器。輸出級(jí)是AB類放大器。

2020-09-23 09:49:22

還是有微小的差模信號(hào),只是一般儀器測(cè)不出來,可是,這樣一來,由于“虛短”就人為(因?yàn)樘摱淌巧疃蓉?fù)反饋的結(jié)果,是人為的)的增大了兩輸入端的共模信號(hào),這樣就對(duì)運(yùn)算放大器的性能構(gòu)成挑戰(zhàn)。為什么運(yùn)算放大器要這么

2019-06-19 04:20:05

非ppm放大器類型運(yùn)算放大器的誤差源輸入共模抑制和偏置誤差

2021-02-05 06:17:26

運(yùn)算放大器這類集成運(yùn)算放大器的特點(diǎn)是差模輸入阻抗非常高,輸入偏置電流非常小,一般Rid>1GΩ~1TΩ,一般為幾皮安到幾十皮安。實(shí)現(xiàn)這些指標(biāo)的主要措施是利用場(chǎng)效應(yīng)管高輸入阻抗的特點(diǎn),用場(chǎng)效應(yīng)管組成

2019-09-26 16:40:31

本帖最后由 gk320830 于 2015-3-5 02:30 編輯

運(yùn)算放大器經(jīng)典應(yīng)用資料特點(diǎn):反相端為虛地,所以共模輸入可視為0,對(duì)運(yùn)放共模抑制比要求低輸出電阻小,帶負(fù)載能力強(qiáng)要求放大倍數(shù)

2011-12-19 14:26:00

VOUT下限為50 mV。顯然,給定運(yùn)算放大器的內(nèi)部設(shè)計(jì)會(huì)影響該輸出共模動(dòng)態(tài)范圍,必要時(shí),器件本身的設(shè)計(jì)應(yīng)當(dāng)最大程度地減小VSAT(HI)和VSAT(LO),以便實(shí)現(xiàn)最大輸出動(dòng)態(tài)范圍。某些類型的運(yùn)算放大器

2014-08-13 15:34:22

為50 mV。 顯然,給定運(yùn)算放大器的內(nèi)部設(shè)計(jì)會(huì)影響該輸出共模動(dòng)態(tài)范圍,必要時(shí),器件本身的設(shè)計(jì)應(yīng)當(dāng)最大程度地減小VSAT(HI)和VSAT(LO),以便實(shí)現(xiàn)最大輸出動(dòng)態(tài)范圍。某些類型的運(yùn)算放大器就采用

2018-09-21 14:50:51

采用運(yùn)算放大器的基準(zhǔn)電壓源

2019-10-29 09:01:22

采用運(yùn)算放大器的基準(zhǔn)電壓源

2019-10-31 09:02:27

本帖最后由 gk320830 于 2015-3-9 06:26 編輯

高速運(yùn)算放大器產(chǎn)品型號(hào)工作電壓±15(V)工作電壓±5(V)工作電壓5(V)最小穩(wěn)定增益(V/V)帶寬@Acl(MHz

2012-08-02 13:22:30

這種全差分放大器能不能使用G=+1高速運(yùn)算放大器作為buffer使用,增加AD8132的負(fù)載能力附件無標(biāo)題.jpg84.1 KB

2019-01-15 10:43:40

特征除非另有說明,否則在TA=+25°C,VS=+5V,RL=25k?時(shí)連接至VS/2。應(yīng)用程序信息OPA336系列運(yùn)算放大器采用最先進(jìn)的0.6微米CMOS工藝制造。它們具有單位增益穩(wěn)定,適用于廣泛

2020-09-27 17:38:18

應(yīng)用的理想選擇,尤其是在遇到高源阻抗的場(chǎng)合。OPAx132運(yùn)算放大器易于使用,并且不存在常見FET輸入運(yùn)算放大器中常見的相位反轉(zhuǎn)和過載問題。輸入共源共柵電路提供優(yōu)良的共模抑制,并在其寬輸入電壓范圍內(nèi)保持低

2020-09-22 16:36:06

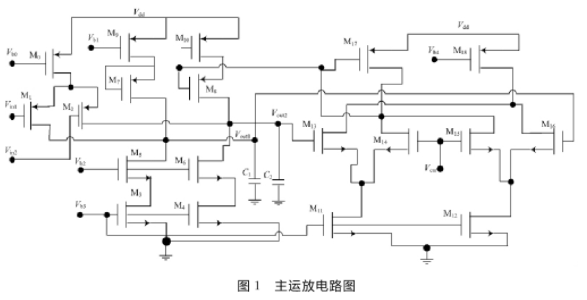

尾電流源架構(gòu),運(yùn)算放大器主體部分單條支路上多達(dá)6個(gè)晶體管,造成偏置困難、工作不穩(wěn)定的問題。因此,必須采用折疊式輸入設(shè)計(jì),本團(tuán)隊(duì)對(duì)運(yùn)算放大器主體部分做了下圖改進(jìn)。

5.4 Cascode補(bǔ)償提高帶寬

2023-09-01 13:42:42

)或沿相同方向(同相)擺動(dòng),因此從兩個(gè)集電極之間獲取的輸出電壓信號(hào)為一個(gè)完美平衡的電路,兩個(gè)集電極電壓之間的零差。這被稱為共模操作,當(dāng)輸入為零時(shí),放大器的共模增益為輸出增益。運(yùn)算放大器還具有一個(gè)低阻抗

2021-02-20 09:15:44

的最高速度時(shí),運(yùn)算放大器不太可能會(huì)用作比較器,因此,通常只需注意從運(yùn)算放大器的信號(hào)擺幅驅(qū)動(dòng) ECL邏輯電平,因雜散電容造成的額外速度損失并不重要。只需采用三個(gè)電阻即可,如圖 2所示。 圖2:驅(qū)動(dòng)ECL

2018-10-31 22:32:44

運(yùn)算放大器的精度。目前溫度漂移參數(shù)可達(dá)0.15ppm。通過改變標(biāo)準(zhǔn)的硅工藝,我們可以設(shè)計(jì)通用運(yùn)算放大器和高速運(yùn)算放大器。典型的例子是LM324。 在標(biāo)準(zhǔn)硅工藝中采用JFET工藝的運(yùn)算放大器主要是將

2023-02-14 15:40:39

。 OTA的設(shè)計(jì) 1、OTA結(jié)構(gòu) 在2.5 V的電源電壓下,雖然套筒式共源共柵結(jié)構(gòu)具有高速、高頻、低功耗的特點(diǎn),但由于套筒式結(jié)構(gòu)的輸出擺幅低,不太適合低壓下的設(shè)計(jì)。因此折疊式共源共柵的運(yùn)放結(jié)構(gòu)是一個(gè)

2018-10-08 15:47:53

雙電源方案,但是雙電源方案在實(shí)際操作中很麻煩,也容易出錯(cuò),所以需要找一個(gè)單電源供電的差分運(yùn)算放大器電路。實(shí)現(xiàn)方案INA321是一款既可以雙電源供電又可以單電源供電的芯片。基本結(jié)構(gòu)很簡(jiǎn)單,如下圖所示...

2021-11-11 08:07:04

和精確(可調(diào))增益;但是,在需要全差分輸出信號(hào)時(shí),它就無能為力了。人們已經(jīng)使用一些方法,用標(biāo)準(zhǔn)組件實(shí)現(xiàn)全差分儀表放大器。但是,它們有著各自的缺點(diǎn)。圖1. 經(jīng)典儀表放大器一種技術(shù)是使用運(yùn)算放大器驅(qū)動(dòng)

2021-10-15 06:30:00

輸出。這樣的運(yùn)算放大器被稱為理想運(yùn)算放大器。一般希望運(yùn)算放大器具有高輸入電阻、低輸出電阻,盡量設(shè)計(jì)為接近理想運(yùn)算放大器的電路結(jié)構(gòu)。運(yùn)算放大器按其放大率放大引腳間的電壓差,因此輸出電壓表示如下。當(dāng)

2019-04-23 22:49:51

輸出。這樣的運(yùn)算放大器被稱為理想運(yùn)算放大器。一般希望運(yùn)算放大器具有高輸入電阻、低輸出電阻,盡量設(shè)計(jì)為接近理想運(yùn)算放大器的電路結(jié)構(gòu)。運(yùn)算放大器按其放大率放大引腳間的電壓差,因此輸出電壓表示如下。當(dāng)

2019-05-26 23:36:35

儀[/td]表放大器與運(yùn)算放大器的區(qū)別是什么??jī)x表放大器是一種具有差分輸入和相對(duì)參考端單端輸出的閉環(huán)增益單元。大多數(shù)情況下,儀表放大器的兩個(gè)輸入端阻抗平衡并且阻值很高,典型值≥109 Ω。其輸入偏置

2011-11-18 22:02:54

初學(xué)者向各位請(qǐng)教一些問題!

1.儀表放大器和普通運(yùn)算放大器有什么不同呢?二者在組建電路上有什么區(qū)別呢?

2.使用儀表放大器對(duì)差分輸入信號(hào)自身的性能有什么要求嗎?(比如共模電壓要到一定值,這是

2023-11-20 07:56:29

電流、輸入輸出全擺幅的CMOS運(yùn)算放大器。同時(shí)還具有低工作電壓,寬工作溫度范圍及低輸入偏置電流等特點(diǎn),這使得該系列運(yùn)算放大器,非常適合在傳感放大器,電池供電設(shè)備以及消費(fèi)類設(shè)備中使用。圖1

2019-04-08 09:33:51

最近在設(shè)計(jì)全差分折疊型共源共柵運(yùn)放的時(shí)候,有一個(gè)問題想不明白,加入偏置電壓后,調(diào)節(jié)管子讓每個(gè)管子都處于飽和狀態(tài),并且輸出處在了VDD/2。但是我發(fā)現(xiàn)只要偏置電壓改變一點(diǎn)點(diǎn)哪怕1mv,靜態(tài)工作點(diǎn)就會(huì)有很大的改變,這是為什么呢,好奇怪,有沒有老哥為我解惑

2022-09-27 00:29:12

也沒有同時(shí)流過兩個(gè)R2電阻,所以放大器A1和A2將作為單位增益跟隨器(緩沖器)工作。由于放大器A1和A2的輸出端的輸入電壓在三個(gè)電阻器網(wǎng)絡(luò)上出現(xiàn)差異,只需改變R1的值就可以改變電路的差分增益。差分運(yùn)算放大器

2020-12-30 09:18:53

低壓共源共柵結(jié)構(gòu)是什么?具有最小余度電壓的共源共柵電流源是什么?

2021-09-29 06:47:22

引起的失調(diào)電壓降至最小。圖2. 滿擺幅輸入放大器的共模輸入電壓從一個(gè)電源擺幅過渡到另一個(gè)電源擺幅時(shí),輸入偏置電流的極性和大小都可能變化。圖3給出了典型運(yùn)算放大器中保持反相和同相結(jié)構(gòu)阻抗匹配的方法。反相

2020-11-20 10:03:54

號(hào)就屬于這種情況。根據(jù)前面的假設(shè)條件,在電阻失配的情況下,這個(gè)電路就不再是一個(gè)真正的差分放大器,VO會(huì)隨著共模分量而變化。 小結(jié) 運(yùn)算放大器,如果選取恰當(dāng)?shù)耐獠吭軌驑?gòu)成各種運(yùn)算電路,如放大、加、減、微分和積分等運(yùn)算電路。運(yùn)算放大器實(shí)現(xiàn)數(shù)學(xué)運(yùn)算的能力,是將高增益與負(fù)反饋結(jié)合起來的結(jié)果。

2021-02-20 16:21:09

是一種廣泛應(yīng)用的運(yùn)放結(jié)構(gòu)。 由于所設(shè)計(jì)的電路應(yīng)用于電源芯片系統(tǒng)中,基于速度等方面綜合考慮,選擇的是一個(gè)折疊式共源共柵運(yùn)算放大器,另外由于運(yùn)放在基準(zhǔn)中是用作負(fù)反饋,所以選用單端輸出的折疊運(yùn)放。具體電路如下

2018-10-09 14:42:54

DC2319A-A,LTC6363的演示電路,是一款低功耗,低噪聲差分運(yùn)算放大器,具有軌到軌輸出擺幅和良好的直流精度。放大器可以被配置為處理全差分輸入信號(hào)或?qū)味溯斎胄盘?hào)轉(zhuǎn)換為差分輸出信號(hào)。 DC2319A的差分輸出可配置一階RC網(wǎng)絡(luò),以驅(qū)動(dòng)ADC的差分輸入

2019-05-17 09:11:23

的最佳輸入共模電壓間不一致程度的增加而大幅降低。 圖2:二級(jí)放大器電路圖。 寬帶差分運(yùn)算放大器的主要劣勢(shì)在于其增益通常都很有限,且其增益級(jí)別也許在內(nèi)部已經(jīng)預(yù)設(shè)。根據(jù)應(yīng)用的不同,可能需要為設(shè)計(jì)添加

2011-07-28 09:32:59

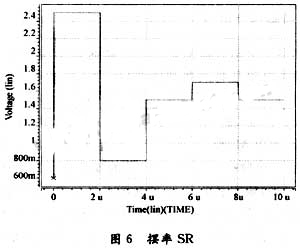

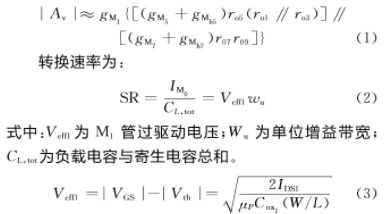

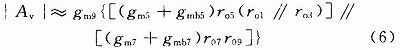

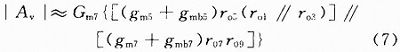

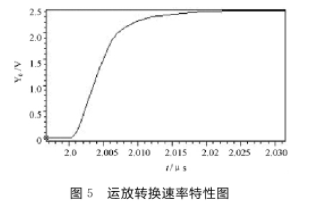

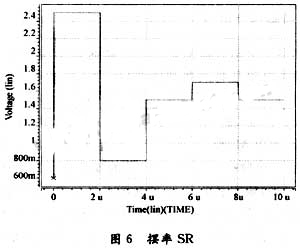

本文介紹的運(yùn)放是一種采用TSMC 0.18 μm Mixed Signal SALICIDE(1P6M,1.8V/3.3V)CMOS工藝的折疊共源共柵運(yùn)放,并對(duì)其進(jìn)行了DC,AC及瞬態(tài)分析,最后與設(shè)計(jì)指標(biāo)進(jìn)行比較。

2021-04-14 06:59:22

電流反饋和電壓反饋運(yùn)算放大器的基本原理提高運(yùn)算放大器速度和帶寬的有效途徑高速運(yùn)算放大器使用過程中的穩(wěn)定性解析

2021-04-23 06:22:22

TI高精度實(shí)驗(yàn)室-運(yùn)算放大器-第七節(jié)-共模抑制和電源抑制抑制可能是一件好事,特別是在共模或電源電壓錯(cuò)誤的情況下。 本系列視頻介紹了如何改變運(yùn)算放大器的共模電壓或電源電壓,從而在交流和直流兩端引入誤差

2021-12-30 06:50:21

我有一個(gè)源極跟隨器(共漏極)配置的NMOS晶體管,但具有從輸出到輸入的反饋。它被用作功率級(jí),因?yàn)樨?fù)載的功率很高。如何用運(yùn)算放大器代替電壓源?

2024-03-01 07:26:44

時(shí),SFDR為76 dB,精度達(dá)0.012%,完全滿足12 bit要求。本文運(yùn)用增益增強(qiáng)型折疊式運(yùn)算放大器,以獲得較高的增益和帶寬。同時(shí)采用柵壓自舉開關(guān),并通過對(duì)電路中的開關(guān)組合優(yōu)化,極大的提高了電路

2021-04-20 06:45:33

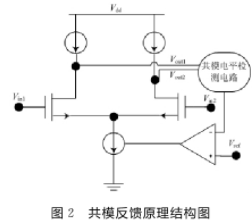

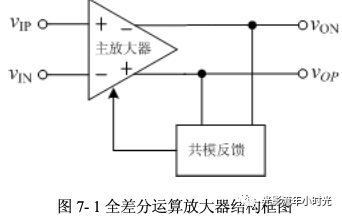

如何設(shè)計(jì)用于運(yùn)算放大器的共模反饋電路?共模反饋電路的設(shè)計(jì)要點(diǎn)有哪些?全差分運(yùn)算放大器的共模反饋原理是什么?

2021-04-20 06:17:09

共源共柵電感的工作機(jī)理是什么?怎么實(shí)現(xiàn)共源共柵CMOS功率放大器的設(shè)計(jì)?

2021-06-18 06:53:41

實(shí)現(xiàn)低于 1uV/oC 的失調(diào)漂移,而 CMOS 的輸入級(jí)則提供高達(dá) 5uV/oC 的失調(diào)漂移。在 CMOS 輸入運(yùn)算放大器中實(shí)現(xiàn)極低失調(diào)的挑戰(zhàn)在于閥值電壓之間的差異(輸入差分對(duì))以及柵-源電壓與閥值

2018-09-13 10:08:21

很麻煩,也容易出錯(cuò),所以需要找一個(gè)單電源供電的差分運(yùn)算放大器電路。實(shí)現(xiàn)方案INA321是一款既可以雙電源供電又可以單電源供電的芯片。基本結(jié)構(gòu)很簡(jiǎn)單,如下圖所示:其中,電路的增益是由R2和R1的比值決定

2019-12-11 17:38:07

求一款實(shí)現(xiàn)IR接近檢測(cè)的高速運(yùn)算放大器

2021-04-25 09:00:00

本文設(shè)計(jì)的帶共模反饋的兩級(jí)高增益運(yùn)算放大器結(jié)構(gòu)分兩級(jí),第一級(jí)為套筒式運(yùn)算放大器,用以達(dá)到高增益的目的;第二級(jí)采用共源級(jí)電路結(jié)構(gòu),以增大輸出擺幅。另外還引入了共模反饋以提高共模抑制比。

2021-04-14 06:55:14

本文設(shè)計(jì)的帶共模反饋的兩級(jí)高增益運(yùn)算放大器結(jié)構(gòu)分兩級(jí),第一級(jí)為套筒式運(yùn)算放大器,用以達(dá)到高增益的目的;第二級(jí)采用共源級(jí)電路結(jié)構(gòu),以增大輸出擺幅。另外還引入了共模反饋以提高共模抑制比。該方案不僅

2021-04-22 06:08:31

求微弱電流檢測(cè)用的共模電壓范圍最大值大于65V的運(yùn)算放大器或儀表放大器

2023-11-14 07:21:08

用于精密放大器的匹配電阻網(wǎng)絡(luò)適用于全差分運(yùn)算放大器,配置為VOUT / VIN = 0.2

2019-11-06 08:53:34

折疊共源共柵比較器怎么修改為遲滯比較器

2021-06-24 07:36:52

初學(xué)者向各位請(qǐng)教一些問題!1.儀表放大器和普通運(yùn)算放大器有什么不同呢?二者在組建電路上有什么區(qū)別呢?2.使用儀表放大器對(duì)差分輸入信號(hào)自身的性能有什么要求嗎?(比如共模電壓要到一定值,這是為什么呢

2018-08-19 07:02:41

怎么設(shè)計(jì)一種單級(jí)全差分增益增強(qiáng)的折疊共源共柵運(yùn)算放大器?

2021-04-20 06:26:29

CMOS運(yùn)算放大器結(jié)構(gòu)具有哪些特點(diǎn)?如何去設(shè)計(jì)CMOS運(yùn)算放大器?怎樣對(duì)CMOS運(yùn)算放大器進(jìn)行仿真測(cè)試?

2021-04-21 07:21:39

。通用運(yùn)算放大器為我們提供了一個(gè)堅(jiān)實(shí)的基礎(chǔ)以開發(fā)專用的元件。所有運(yùn)算放大器旨在在這些領(lǐng)域實(shí)現(xiàn)好的性能:大開環(huán)增益、共模抑制和電源抑制。高輸入阻抗和低輸出阻抗也是關(guān)鍵要求。Precision

2018-10-22 08:57:48

,在中國(guó)構(gòu)建了與羅姆日本同樣的集開發(fā)、生產(chǎn)、銷售于一體的一條龍?bào)w制。BU7475HFV/BU7475SHFV是ROHM推出的超低消耗電流的CMOS運(yùn)算放大器。是在單芯片中集成了輸入輸出全擺幅和接地檢測(cè)

2019-04-19 04:47:53

集成運(yùn)算放大器電子教案教學(xué)基本要求教 學(xué) 基 本 要 求主 要 知 識(shí) 點(diǎn)熟練掌握正確理解一般了解集成電路中元器件的特點(diǎn)及集成運(yùn)放大典型結(jié)構(gòu)√差分放大電路的類型與特點(diǎn)√差分放大電路分析計(jì)算方法

2009-09-16 09:12:40

分析了準(zhǔn)浮柵晶體管PMOS 的工作原理、電學(xué)特性和等效電路,設(shè)計(jì)了一種電路結(jié)構(gòu)簡(jiǎn)單的共模反饋電路(CMFB),實(shí)現(xiàn)了一個(gè)低壓低功耗的差分運(yùn)算放大器。采用Chrt0.35umCMOS 工藝

2009-11-27 11:39:23 8

8 本文設(shè)計(jì)了一種低壓低功耗CMOS 折疊-共源共柵運(yùn)算放大器。該運(yùn)放的輸入級(jí)采用折疊-共源共柵結(jié)構(gòu),可以優(yōu)化輸入共模范圍,提高增益;由于采用AB 類推挽輸出級(jí),實(shí)現(xiàn)了全擺幅輸

2009-12-14 10:37:19 29

29 設(shè)計(jì)了一種用在高精度音頻Σ-Δ A/D轉(zhuǎn)換器中的高增益CMOS全差分運(yùn)算放大器。該運(yùn)算放大器采用了套筒式共源共柵結(jié)構(gòu)和開關(guān)電容共模反饋電路。通過分析和優(yōu)化電路性能參數(shù),實(shí)現(xiàn)了

2010-07-29 17:23:00 51

51 0.6μm CMOS工藝全差分運(yùn)算放大器的設(shè)計(jì)

0 引言 運(yùn)算放大器是數(shù)據(jù)采樣電路中的關(guān)鍵部分,如流水線模數(shù)轉(zhuǎn)換器等。在此類設(shè)計(jì)中,速度和精度是兩個(gè)

2009-12-08 17:19:51 1632

1632 高速型運(yùn)算放大器是什么意思

高速型運(yùn)算放大器的定義

2010-03-09 15:51:14 2516

2516 折疊共源共柵運(yùn)算放大器原理及設(shè)計(jì)

1 引言

本文介紹的運(yùn)放是一種采用TSMC 0.18 μm Mixed Signal SALICIDE(1P6M,1.8V/3.3V)CMOS工藝的折疊共源共柵運(yùn)放,并對(duì)其進(jìn)行了DC

2010-03-12 15:05:24 10224

10224

電子發(fā)燒友為您提供了李福樂的全差分運(yùn)算放大器電子書,介紹了全差分 運(yùn)算放大器 的基本知識(shí),如對(duì)于全差分放大器,其輸出是差分方式且輸出共模電壓可以獨(dú)立于差分電壓設(shè)置。對(duì)

2011-07-18 16:54:32 0

0 設(shè)計(jì)并討論了一種高單位增益帶寬cmos全差分運(yùn)算放大器。由于折疊共源共柵結(jié)構(gòu)電路具有相對(duì)高的單位增益帶寬以及開關(guān)電容共模反饋電路穩(wěn)定性好、對(duì)運(yùn)放頻率特性影響小等優(yōu)點(diǎn),故

2011-07-31 21:51:57 115

115 本文設(shè)計(jì)了一種用于高速ADC中的高速高增益的全差分CMOS運(yùn)算放大器。主運(yùn)放采用帶開關(guān)電容共模反饋的折疊式共源共柵結(jié)構(gòu),利用增益提高和三支路電流基準(zhǔn)技術(shù)實(shí)現(xiàn)一個(gè)可用于12~14

2012-06-06 13:08:28 42

42 設(shè)計(jì)了一種用于高速ADC中的高速高增益的全差分CMOS運(yùn)算放大器。主運(yùn)放采用帶開關(guān)電容共模反饋的折疊式共源共柵結(jié)構(gòu),利用增益提高和三支路電流基準(zhǔn)技術(shù)實(shí)現(xiàn)一個(gè)可用于12~14 bit精度

2012-06-07 14:21:36 38

38 恒跨導(dǎo)軌對(duì)軌CMOS運(yùn)算放大器的設(shè)計(jì)_趙雙

2017-01-07 22:14:03 2

2 是有很用的。 這種靈活性允許在 CMOS

工藝中發(fā)展高性能無緩沖運(yùn)算放大器。 目前, 這樣的放大器已被廣泛用于無線電通信的集成電路中。 介紹了一種折疊共源

共柵的運(yùn)算放大器, 采用 TSMC 0. 18 混合信號(hào)雙阱 CMOS 工藝庫(kù), 用 HSpice W 2005. 03 進(jìn)行設(shè)計(jì)仿真, 最后與設(shè)計(jì)指標(biāo)

2022-07-08 16:32:35 21

21 基于 chartered 0.35 m 工藝,采用 PMOS 管作為輸入管的折疊式共源共柵結(jié)構(gòu),設(shè)計(jì)了一種采用增益提高技術(shù)的兩級(jí)運(yùn)算放大器。利用 Cadence 公司的spectre 對(duì)電路進(jìn)行仿真

2017-11-04 10:40:17 29

29 CMOS運(yùn)算放大器的基本分類1、單級(jí)差分運(yùn)算放大器(電流鏡做負(fù)載的差分放大器)2、套筒式共源共柵CMOS運(yùn)算放大器(單級(jí))3、折疊共源共柵CMOS運(yùn)算放大器(單級(jí))4、兩級(jí)CMOS運(yùn)算放大器

5、Rail-to-Rail CMOS運(yùn)算放大器6、Chopper CMOS運(yùn)算放大器 運(yùn)放的概念、組成與電路結(jié)構(gòu)

2018-11-07 10:10:57 89

89 我的論文題目是《CMOS 運(yùn)算放大器的設(shè)計(jì)和優(yōu)化》。我們可以知道無論在數(shù) 字還是模擬電路中,運(yùn)算放大器運(yùn)用之廣泛是顯而易見的。

2021-04-13 09:32:44 15

15 淺析采用高速運(yùn)算放大器進(jìn)行低失真設(shè)計(jì)

2022-02-11 15:28:18 10

10 電子發(fā)燒友網(wǎng)站提供《差分運(yùn)算放大器板.zip》資料免費(fèi)下載

2022-07-04 10:27:11 1

1 電子發(fā)燒友網(wǎng)站提供《全差分運(yùn)算放大器開源分享.zip》資料免費(fèi)下載

2022-07-26 15:06:11 5

5

![]()

![]()

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論