(2)

故定義最大采樣頻率,其構成為:

其本身由輸出數據的讀取速率調理,其中,

圖4.AD4020的時序圖。

幸運的是,AD4020的轉換時間超短,為325 ns,采樣速率為1 MSPS,采樣時間為675 ns,基于此,其串行數據讀取頻率低于33 MHz,與DSP同步串口(如SHARC® ADSP-21479)相當,功耗也非常低。

一款超低功耗的多通道系統(tǒng)

出于能耗、精度和操作模式選擇靈活性的原因,同時也是出于商業(yè)考慮,在這些應用中不能考慮基于FPGA的解決方案。要處理來自這些20位ADC的串行輸出并實現最優(yōu)抽取濾波器,只能使用DSP浮點處理器。

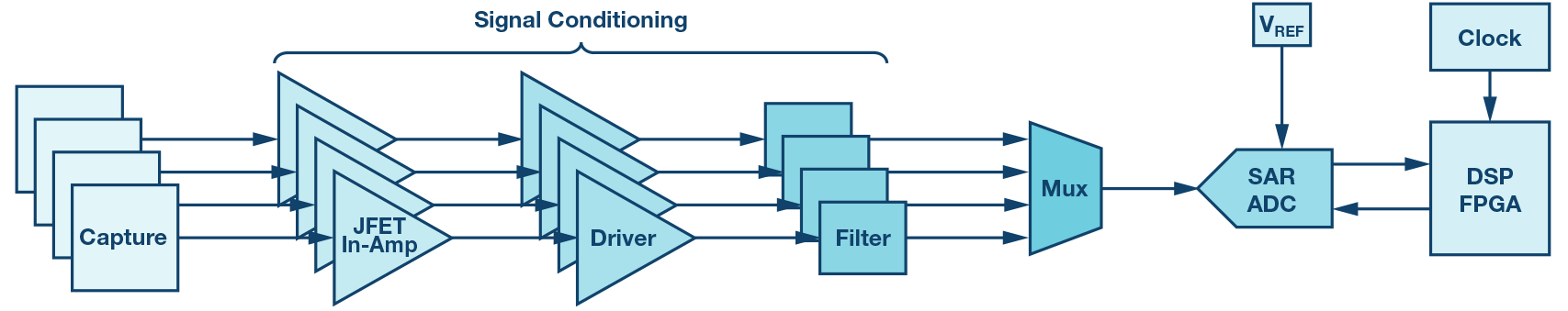

如今,有許多數據采集系統(tǒng)都能通過大量信道同時采樣。這就導致許多ADC并行運行,同時由同一個控制器控制,該控制器還要負責收集數據并將其存儲在存儲器中以供后續(xù)分析。

運用SHARC ADSP-21479或其快速版ADSP-21469和ADSP-21489(時鐘頻率為450 MHz)等高性能SAR ADC構建的系統(tǒng)不但現實可行,而且在性能、開發(fā)時間、能耗和緊湊性等方面也是可圈可點。這些處理器具有支持8個模數數字化通道所需要的全部功能和外設,包括同步串行接口、不同時鐘信號的發(fā)生以及觸發(fā)轉換等。在所有SHARC處理器中,ADSP-21479是唯一一款采用低泄漏65納米CMOS工藝制造的32/40位浮點DSP,其優(yōu)勢是能大幅降低泄漏或靜態(tài)電流,并且其結溫幾乎呈指數級演進。作為處理器及其外設頻率和活動函數的動態(tài)電流也低于以標準或快速CMOS工藝制造的處理器。不足之處則在于,相比常規(guī)版本,其最大CPU頻率下降了約30%-40%,但仍然足以滿足此類應用的需求。

ADSP-21479搭載了多種外設,其中有一個特殊模塊被稱為串行輸入端口(SIP),該模塊能同時從同步運行的8個外部串口發(fā)射器接收信號流以及時鐘和同步信號。事實上,可以將與AD4020類似的8個ADC直接接入該接口,從而接入處理器。如圖5所示,8個通道有自己的IDP_SCK時鐘、IDP_FS同步和IDP_DAT輸入信號,一旦解串行,它們的數據會自動復用到32位、8字FIFO存儲器中,然后通過64位DMA數據包或CPU執(zhí)行的讀取操作,傳輸到SHARC內部RAM。DMA傳輸操作中,SIP由運行于自動乒乓模式下的雙索引DMA通道伺服。此外,ADSP-21479還搭載有四個精密時鐘發(fā)生器(用于低抖動,縮寫為PCG),能夠從內部或外部源(TCXO)生成獨立的時鐘和同步信號對。通過編程20位內部分頻器可取得這些激勵的頻率、周期、脈沖寬度和相位。每個PCGx生成單元提供由一對AD4020轉換器共享的一對CLK/FS信號,但在轉換階段時鐘必須靜音,所以需要一個邏輯門,以便把IDP_FS信號和IDP_SCK信號結合起來形成SCK時鐘。圖5中的時序圖顯示,一旦轉換時間tconv已經過去,必須盡可能快地以33.3 MHz的速率,從當前樣本中讀取20位數據,以在采樣頻率中維持1 MSPS的神奇屏障。大約600 ns后,數據被傳輸到其中一個SIP緩沖器中,此時可以使用IDP_FS或CNV信號啟動新的轉換周期,使AD4020進行新的轉換操作。使后者的最大轉換時間達到325 ns,這對應于CNV信號的脈沖寬度,即12個IDP_SCK時鐘周期或360 ns。總之,如圖5中的時序圖所示,一個完整的掃描周期需要32個IDP_SCK信號周期,總時間為960 ns,因此其最大采樣速率為1.040 MSPS。

同樣,ADC LTC2378-20可以與ADSP-21489相關聯,因為它能夠在高達50 MHz的外設時鐘頻率下工作,在這種情況下,采樣速率為900 kSPS,如表1所示。遺憾的是,靜態(tài)電源電流(Iddint)或后者的泄漏電流遠高于動態(tài)電流,使得該配置的總功耗超過可用功率,達到不可接受的程度。

抽取濾波

假設將這些轉換器用于過采樣模式,如此,就有必要提供一個能滿足上述要求且針對目標頻帶定制的抽取濾波器,在所需計算能力和功耗方面盡量降低對DSP的影響。目前,用于改變采樣速率的程序已經成為一種標準的數字信號處理操作,可以用內插器和數字抽取器實現。出于相位響應線性度考慮,低通抽取濾波器采用有限脈沖響應(FIR)拓撲結構,可以根據效率要求采用不同的拓撲結構:

► 抽取專用直接或優(yōu)化FIR濾波器

► 級聯多速率FIR濾波器(1/2頻段)

► 多相FIR濾波器

無論是FIR還是IIR類型的多相濾波器都是抽取或插值濾波器最有效的實現方案之一。然而,傳統(tǒng)數字處理方案要求在抽取之前進行濾波。在此假設下,1/M抽取濾波器由低通濾波器和緊隨其后的采樣頻率降級組成(圖6a)。預先對信號濾波,避免頻譜混疊,然后以M-1的速率定期消除樣本。然而,常規(guī)FIR或其他結構針對這些抽取濾波器的直接實現方案存在資源浪費問題,因為被拒樣本是幾十甚至幾百次累乘(MAC)的結果。使用分解成若干濾波器組的多相濾波器或是針對抽取進行優(yōu)化的濾波器,可以基于某些特點(如圖6b所示)形成高效的濾波器。

憑借FIR濾波專用SIMD架構和硬件加速器,以及針對數字信號處理而優(yōu)化的指令集,SHARC ADSP-21479特別適合實現這些類型的濾波器。每個SHARC處理單元都有一個32/40位乘法器累加器,能夠在266 MHz的CPU頻率下,每秒實現533次定點或浮點MAC計算。然而,對于一些存在顯著延遲(房間均衡或音效)的應用,需要增加計算能力,使內核從諸如FIR、IIR、FFT濾波等密集和持續(xù)乘法運算中解脫出來,用專門的硬件加速器去執(zhí)行這些運算。如此,用戶就能完全自主決定,將CPU用于計算需要執(zhí)行復雜搜集的復雜算法。FIR濾波專用加速器有專門的本地存儲器,用于存儲數據和系數,并具有以下特征:

故定義最大采樣頻率,其構成為:

前天 11:34 上傳

下載附件 (1.44 KB) (3)其本身由輸出數據的讀取速率調理,其中,

前天 11:34 上傳

下載附件 (1.42 KB) (4) tsck = 1/Fsck

前天 11:34 上傳

下載附件 (18.78 KB)圖4.AD4020的時序圖。

幸運的是,AD4020的轉換時間超短,為325 ns,采樣速率為1 MSPS,采樣時間為675 ns,基于此,其串行數據讀取頻率低于33 MHz,與DSP同步串口(如SHARC® ADSP-21479)相當,功耗也非常低。

一款超低功耗的多通道系統(tǒng)

出于能耗、精度和操作模式選擇靈活性的原因,同時也是出于商業(yè)考慮,在這些應用中不能考慮基于FPGA的解決方案。要處理來自這些20位ADC的串行輸出并實現最優(yōu)抽取濾波器,只能使用DSP浮點處理器。

如今,有許多數據采集系統(tǒng)都能通過大量信道同時采樣。這就導致許多ADC并行運行,同時由同一個控制器控制,該控制器還要負責收集數據并將其存儲在存儲器中以供后續(xù)分析。

運用SHARC ADSP-21479或其快速版ADSP-21469和ADSP-21489(時鐘頻率為450 MHz)等高性能SAR ADC構建的系統(tǒng)不但現實可行,而且在性能、開發(fā)時間、能耗和緊湊性等方面也是可圈可點。這些處理器具有支持8個模數數字化通道所需要的全部功能和外設,包括同步串行接口、不同時鐘信號的發(fā)生以及觸發(fā)轉換等。在所有SHARC處理器中,ADSP-21479是唯一一款采用低泄漏65納米CMOS工藝制造的32/40位浮點DSP,其優(yōu)勢是能大幅降低泄漏或靜態(tài)電流,并且其結溫幾乎呈指數級演進。作為處理器及其外設頻率和活動函數的動態(tài)電流也低于以標準或快速CMOS工藝制造的處理器。不足之處則在于,相比常規(guī)版本,其最大CPU頻率下降了約30%-40%,但仍然足以滿足此類應用的需求。

ADSP-21479搭載了多種外設,其中有一個特殊模塊被稱為串行輸入端口(SIP),該模塊能同時從同步運行的8個外部串口發(fā)射器接收信號流以及時鐘和同步信號。事實上,可以將與AD4020類似的8個ADC直接接入該接口,從而接入處理器。如圖5所示,8個通道有自己的IDP_SCK時鐘、IDP_FS同步和IDP_DAT輸入信號,一旦解串行,它們的數據會自動復用到32位、8字FIFO存儲器中,然后通過64位DMA數據包或CPU執(zhí)行的讀取操作,傳輸到SHARC內部RAM。DMA傳輸操作中,SIP由運行于自動乒乓模式下的雙索引DMA通道伺服。此外,ADSP-21479還搭載有四個精密時鐘發(fā)生器(用于低抖動,縮寫為PCG),能夠從內部或外部源(TCXO)生成獨立的時鐘和同步信號對。通過編程20位內部分頻器可取得這些激勵的頻率、周期、脈沖寬度和相位。每個PCGx生成單元提供由一對AD4020轉換器共享的一對CLK/FS信號,但在轉換階段時鐘必須靜音,所以需要一個邏輯門,以便把IDP_FS信號和IDP_SCK信號結合起來形成SCK時鐘。圖5中的時序圖顯示,一旦轉換時間tconv已經過去,必須盡可能快地以33.3 MHz的速率,從當前樣本中讀取20位數據,以在采樣頻率中維持1 MSPS的神奇屏障。大約600 ns后,數據被傳輸到其中一個SIP緩沖器中,此時可以使用IDP_FS或CNV信號啟動新的轉換周期,使AD4020進行新的轉換操作。使后者的最大轉換時間達到325 ns,這對應于CNV信號的脈沖寬度,即12個IDP_SCK時鐘周期或360 ns。總之,如圖5中的時序圖所示,一個完整的掃描周期需要32個IDP_SCK信號周期,總時間為960 ns,因此其最大采樣速率為1.040 MSPS。

同樣,ADC LTC2378-20可以與ADSP-21489相關聯,因為它能夠在高達50 MHz的外設時鐘頻率下工作,在這種情況下,采樣速率為900 kSPS,如表1所示。遺憾的是,靜態(tài)電源電流(Iddint)或后者的泄漏電流遠高于動態(tài)電流,使得該配置的總功耗超過可用功率,達到不可接受的程度。

抽取濾波

假設將這些轉換器用于過采樣模式,如此,就有必要提供一個能滿足上述要求且針對目標頻帶定制的抽取濾波器,在所需計算能力和功耗方面盡量降低對DSP的影響。目前,用于改變采樣速率的程序已經成為一種標準的數字信號處理操作,可以用內插器和數字抽取器實現。出于相位響應線性度考慮,低通抽取濾波器采用有限脈沖響應(FIR)拓撲結構,可以根據效率要求采用不同的拓撲結構:

► 抽取專用直接或優(yōu)化FIR濾波器

► 級聯多速率FIR濾波器(1/2頻段)

► 多相FIR濾波器

無論是FIR還是IIR類型的多相濾波器都是抽取或插值濾波器最有效的實現方案之一。然而,傳統(tǒng)數字處理方案要求在抽取之前進行濾波。在此假設下,1/M抽取濾波器由低通濾波器和緊隨其后的采樣頻率降級組成(圖6a)。預先對信號濾波,避免頻譜混疊,然后以M-1的速率定期消除樣本。然而,常規(guī)FIR或其他結構針對這些抽取濾波器的直接實現方案存在資源浪費問題,因為被拒樣本是幾十甚至幾百次累乘(MAC)的結果。使用分解成若干濾波器組的多相濾波器或是針對抽取進行優(yōu)化的濾波器,可以基于某些特點(如圖6b所示)形成高效的濾波器。

憑借FIR濾波專用SIMD架構和硬件加速器,以及針對數字信號處理而優(yōu)化的指令集,SHARC ADSP-21479特別適合實現這些類型的濾波器。每個SHARC處理單元都有一個32/40位乘法器累加器,能夠在266 MHz的CPU頻率下,每秒實現533次定點或浮點MAC計算。然而,對于一些存在顯著延遲(房間均衡或音效)的應用,需要增加計算能力,使內核從諸如FIR、IIR、FFT濾波等密集和持續(xù)乘法運算中解脫出來,用專門的硬件加速器去執(zhí)行這些運算。如此,用戶就能完全自主決定,將CPU用于計算需要執(zhí)行復雜搜集的復雜算法。FIR濾波專用加速器有專門的本地存儲器,用于存儲數據和系數,并具有以下特征:

前天 11:34 上傳

下載附件 (74.81 KB) 電子發(fā)燒友App

電子發(fā)燒友App

評論