鎖相環 (PLL) 和壓控振蕩器 (VCO) 輸出特定頻率的RF信號,理想情況下此信號應當是輸出中的唯一信號。但事實上,輸出中存在干擾雜散信號和相位噪聲。本文討論最麻煩的雜散信號之一——整數邊界雜散——的仿真與消除。

僅可工作在鑒頻鑒相器參考頻率整數倍的PLL和VCO組合 (PLL/VCO) 稱為整數N分頻PLL。具有更精細頻率步進的PLL/VCO稱為小數N分頻PLL。小數N分頻PLL/VCO靈活性更高,使用更廣。小數N分頻PLL能以參考速率調制PLL中的反饋路徑,從而實現該目標。小數N分頻PLL/VCO相比鑒相器參考頻率雖然具有更為精細的頻率步進,但它會產生稱為整數邊界雜散 (IBS) 的雜散輸出。整數邊界雜散發生在PLL鑒頻鑒相器參考(或比較)頻率 (fPFD) 的整數倍(1、2、3 … 20、21 …)之處。例如,假設fPFD = 100 MHz,則整數邊界雜散將位于100 MHz、200 MHz、300 MHz … 2000 MHz、2100 MHz。在所需VCO輸出信號為2001 MHz的系統中,IBS將位于2000 MHz——相比所需信號偏移1 MHz。由于PLL系統的有效采樣,這種偏移1 MHz的IBS混疊至所需信號的兩側。因此,當所需輸出為2001 MHz時,雜散信號將位于2000 MHz和2002 MHz。

整數邊界雜散不受歡迎的兩個主要原因:

如果它們距離載波(期望信號)頻偏小,則IBS功率會對相位噪聲積分產生貢獻。

如果它們距離載波(期望信號)頻偏大,則IBS將調制/解調相鄰通道至目標通道,導致系統失真。

在某些系統中,高整數邊界雜散會導致部分輸出通道無法使用。如果某個系統在特定頻譜帶寬內有1000個通道,并且10% 通道內的雜散信號高于某個功率水平,那么這100個通道可能無法使用。在頻譜帶寬成本高昂的協議中,如果有10%的通道不可用,那么這將是一種浪費。

當整數邊界離開目標輸出頻率而落在PLL帶寬內的時候,整數邊界雜散最強。也就是說,如果輸出頻率為2000.01 MHz,并且環路帶寬為50 kHz,則IBS最大。隨著輸出頻率遠離整數邊界,IBS功率也隨之以可計算和可重復的形式下降。ADI公司的全新免費仿真器——ADIsimFrequencyPlanner——采用這種可預測的特性來精確仿真整數邊界雜散功率(及其它)。

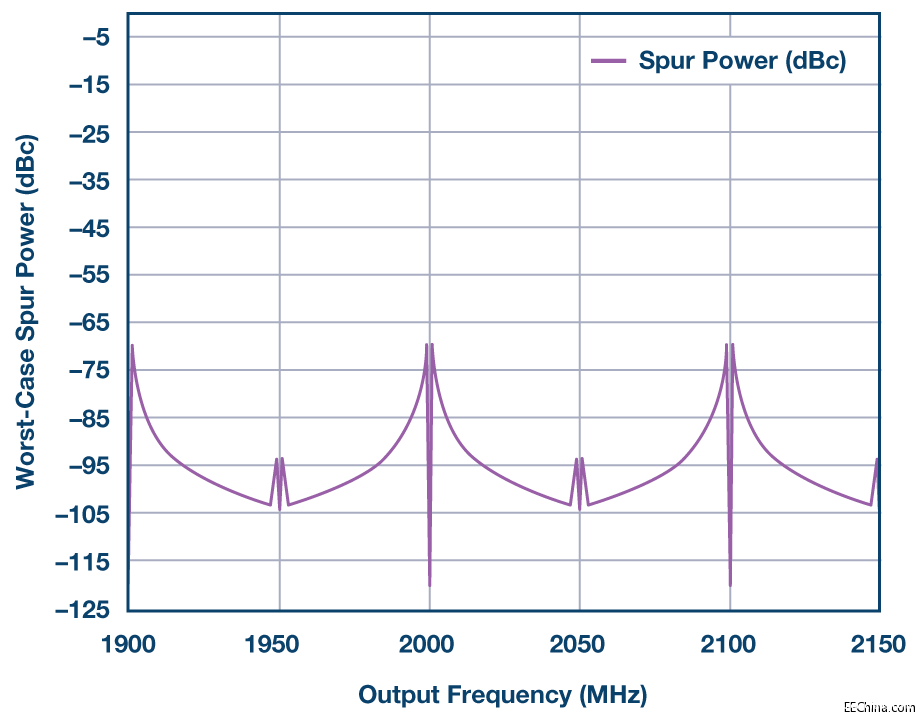

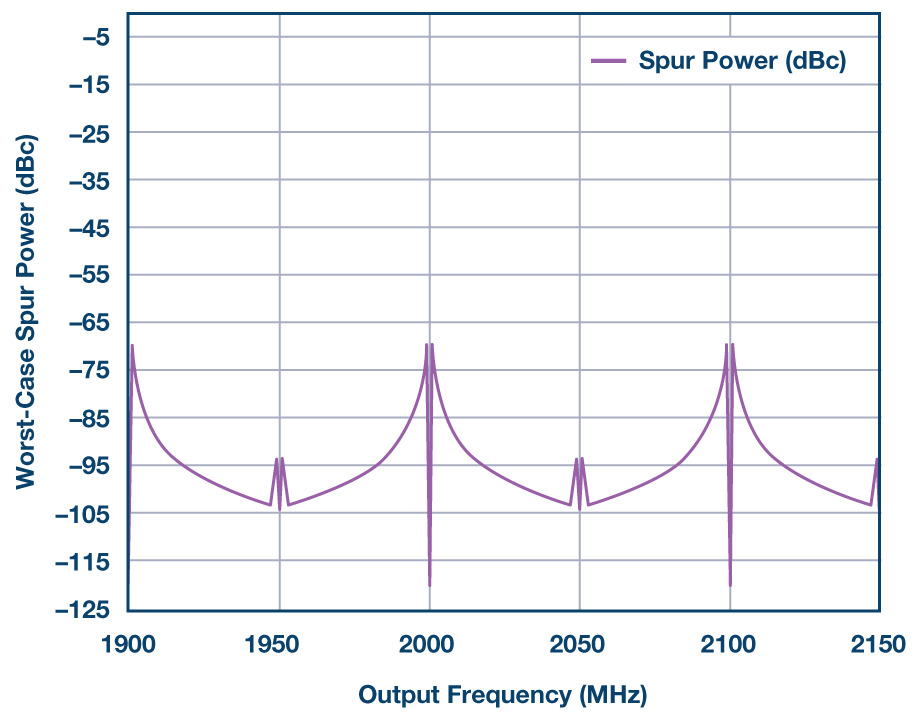

圖1顯示了最差情況下的整數邊界雜散功率,此時各輸出頻率范圍為1900 MHz至2150 MHz(1 MHz步進頻率)。可以看到,在2001 MHz時,最差情況IBS功率為 –70 dBc(載波功率以下70 dB)。在2000 MHz處沒有IBS,因為輸出頻率落在整數邊界上。IBS功率隨著載波遠離整數邊界而下降,直到載波開始接近下一個整數邊界。

落在兩個整數邊界(圖1中的2049 MHz和2051 MHz)之間的一半處的雜散信號,屬于二階整數邊界雜散。二階整數邊界雜散出現在整數邊界之間的一半位置。通常情況下,二階IBS比一階IBS低10 dB至20 dB。ADIsimFrequencyPlanner可以仿真一階、二階、三階、四階和五階整數邊界雜散。

圖1. 1900 MHz至2150 MHz范圍內各輸出頻率的最差情況整數邊界雜散功率(1 MHz頻率步進;100 kHz環路帶寬;HMC830)。

假設某個調制方案聲明整數邊界雜散功率高于 –80 dBc的通道不可用;那么,圖1中大約有10% 的通道將不再可用。為了解決這個問題,ADIsimFrequencyPlanner可以優化PLL/VCO配置以便降低(并且在大多數情況下消除)整數邊界雜散。前文提到整數邊界雜散發生在PFD頻率的整數倍之處,并且在靠近載波頻率時最大。如果可以改變PFD頻率,使PFD頻率的整數倍落在足夠大的載波頻率偏移頻率處,那么IBS功率將下降至不會產生問題的水平。這就是ADIsimFrequencyPlanner算法所做的事情——ADIsimFrequencyPlanner計算一階到五階整數邊界雜散的相對功率,并找到最優解決方案,使VCO輸出的整數邊界雜散最低。

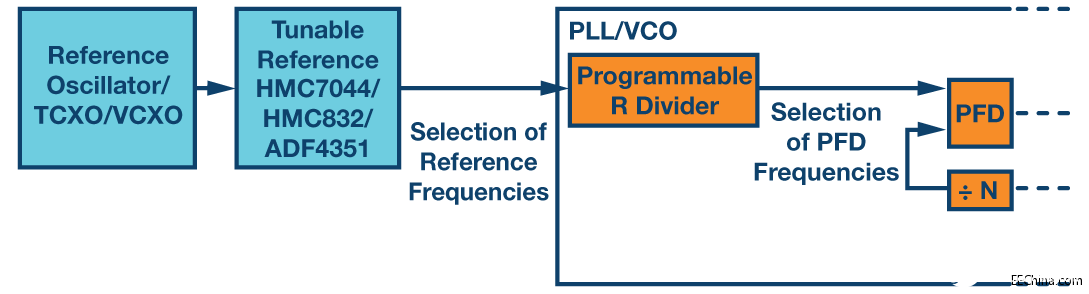

如何改變PFD頻率?一般而言,在PLL/VCO系統中,PFD頻率是固定的。然而,對于大部分可編程時鐘分配源、PLL參考輸入分頻器和PLL小數N分頻調制器架構來說,現在可以輕松改變每個輸出通道的PFD頻率了。

在推薦的解決方案中,我們采用新型時鐘生成和分配芯片HMC7044。HMC7044具有14個超低噪聲輸出,每個輸出均集成可編程分頻器。通過將這些輸出之一連接到PLL參考輸入,然后對輸出分頻器按需進行編程,則參考頻率陣列便可用于PLL。

HMC7044是時鐘分配系統,可用于針對ADC、DAC和其它系統元件采用多種同步時鐘的應用。無需那么多輸出的較簡單應用可以使用更為簡單的替代方案,比如HMC832或ADF4351——這兩款器件均為集成式PLL和VCO芯片。

然后,在PLL參考輸入端,參考輸入分頻器(R分頻器)可按需編程,將可用參考頻率陣列分為更大的PFD頻率陣列(PFD頻率是R分頻器輸出端的頻率)。多虧了PLL內置的高階小數N分頻調制器,改變PFD頻率不會妨礙得到所需的輸出頻率。此外,PLL的可編程電荷泵電流可用來補償PFD頻率的變化,因此可以保持恒定環路帶寬。

圖2. PFD頻率選擇框圖。

示例:

fPFD (MHz)NICPfPFD × N = RFOUT (MHz)注釋

10020.012.082001IBS ( ± 1 MHz 時)

7526.681.882001IBS ( ± 24 MHz 時)

其中:

ICP= 可編程電荷泵電流;

fPFD = PLL PFD頻率;

N = PLL小數N分頻值;

RFOUT = VCO輸出頻率/載波頻率/目標信號

可編程電荷泵電流的變化方向與PFD頻率相反——PFD頻率增加則電荷泵電流下降。這是為了保持環路濾波器的動態恒定。

使用ADIsimFrequencyPlanner時,用戶輸入所需的輸出頻率范圍、步進大小、PFD頻率和參考頻率限制條件,以及環路濾波器參數。用戶還可選擇可用的時鐘發生器輸出分頻器和PLL參考輸入分頻器。隨后,ADIsimFrequencyPlanner逐一對目標頻率進行分析,并根據可用PFD頻率陣列計算最優PFD頻率。然后,ADIsimFrequencyPlanner將所需的分頻器設置和電荷泵電流返回至用戶。數據可輕松導出至查找表中,供最終應用的固件讀取,然后相應編程HMC7044和PLL/VCO。ADIsimFrequencyPlanner還可生成一系列照片,向用戶顯示發生了什么。

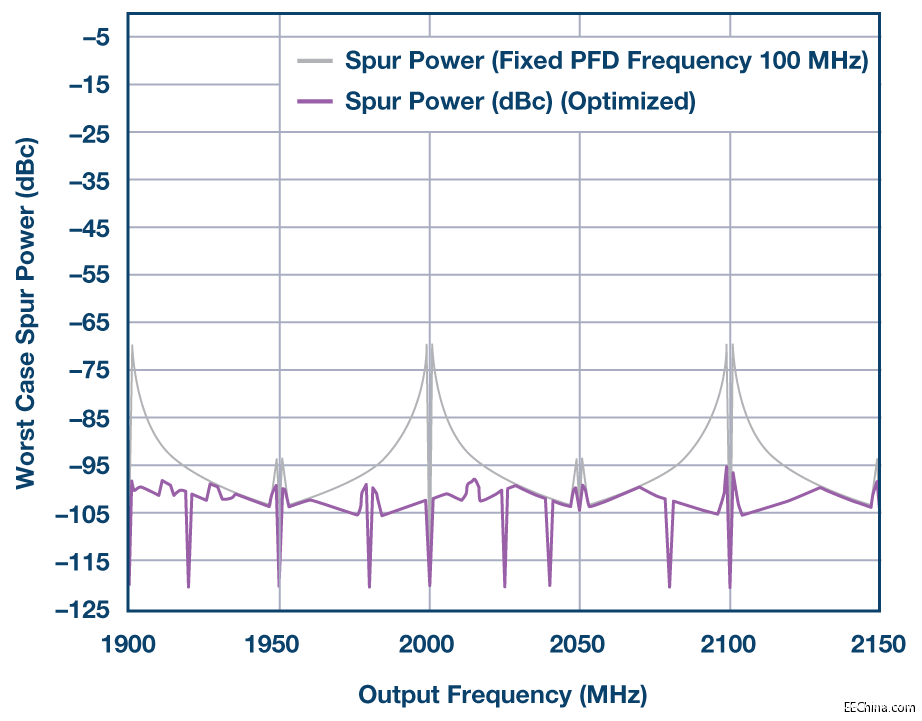

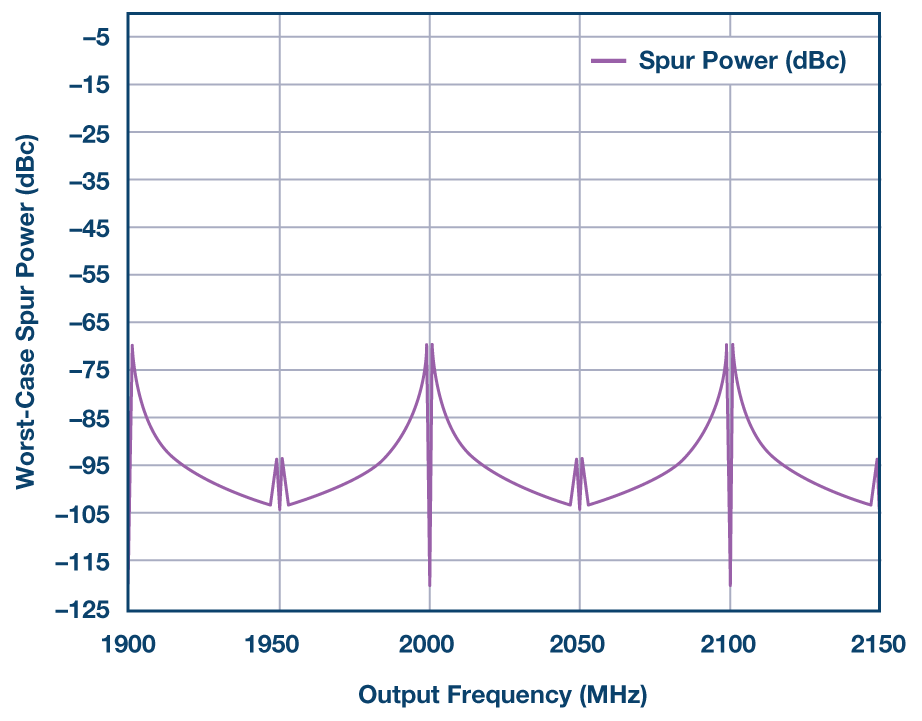

在圖3中,用戶使用了與圖1相同的配置,不同的是這次PFD頻率通過改變HMC7044輸出分頻器和PLL參考輸入分頻器而優化。未優化的仿真如圖中灰色部分所示,供對比。

圖3. 與圖1相同的輸出配置,不過這次優化了PFD頻率。

由圖3可見,在輸出范圍內(1900 MHz至2150 MHz,1 MHz步進),所有整數邊界雜散現在都低于 –95 dBc。這表示性能有了大幅提升,并且目標輸出有極高的百分比具有相同的高質量。

將ADIsimFrequencyPlanner應用到寬帶VCO

在測量ADIsimFrequencyPlanner精度和有效性的實驗中,將部分ADI高性能器件放在一起,并在實驗室中進行評估。該實驗需要用到下列器件:

HMC7044時鐘生成和分配:

高達3.2 GHz輸出。

J符合JESD204B標準。

超低噪聲(抖動低于50 fs,12 kHz至20 MHz)。

–142 dBc/Hz(偏移983.04 MHz輸出800 kHz)。

6個可編程輸出。

集成式PLL和VCO ADF5355:

RF輸入高達8 GHz。

100 MHz最大PFD頻率。

–233 dBc/Hz歸一化相位噪底。

超低噪聲PLL HMC704:

RF輸入高達8 GHz。

100 MHz最大PFD頻率。

–233 dBc/Hz歸一化相位噪底。

雖然ADF5355內部集成PLL,但是使用HMC704從外部鎖定ADF5355 VCO。這樣做有兩個主要好處:

總相位噪聲得益于ADF5355業界領先的VCO相位噪聲性能,以及得益于HMC704業界領先的PLL相位噪聲性能。

隔離VCO和PLL可減少干擾信號耦合,從而降低雜散信號的功率。

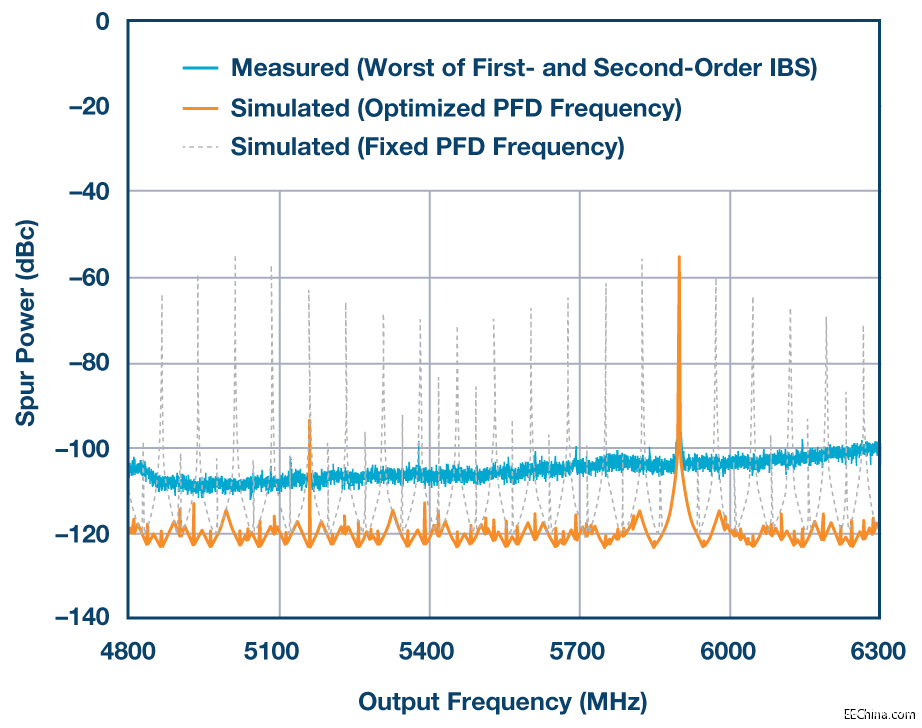

ADIsimFrequencyPlanner用來優化4800 MHz至6300 MHz范圍的輸出,步進為250 kHz(6000次步進)。在每個步進處,最優分頻器設置(因而PFD頻率也最優)和電荷泵電流編程至HMC7044、ADF5355和HMC704。一旦器件編程并產生步進,頻譜分析儀便測量載波功率、一階和二階整數邊界雜散的功率。頻譜分析儀采用極為狹窄的頻率范圍和分辨率帶寬——即便如此,在大部分通道中僅測量噪聲,因為整數邊界雜散功率低于儀器的噪底。

以下測量為PFD頻率限制在60 MHz至100 MHz范圍內的時候測得。環路帶寬和相位裕量分別為17 kHz和49.6°。

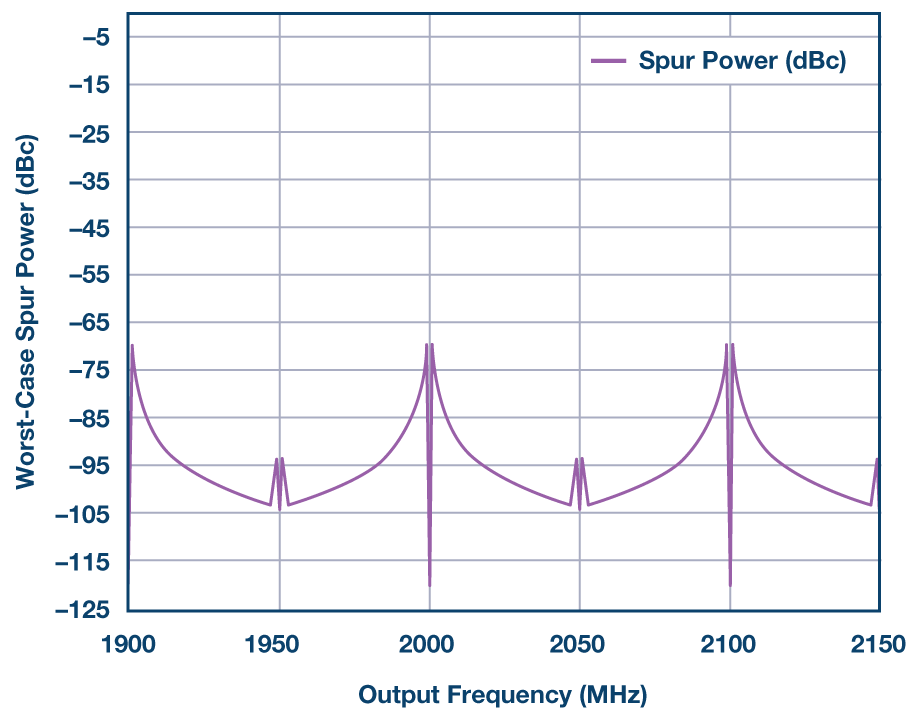

圖4顯示了HMC7044、ADF5355和HMC704解決方案的測量和仿真結果。

仿真和測量6000個輸出通道。

大部分整數邊界雜散都在 –120 dBc附近仿真。這低于頻譜分析儀的噪底,因而僅測量噪聲。

大部分頻率的雜散低于 –100 dBc!典型要求是 –70 dBc至 –80 dBc。

優化不改進IBS的唯一區域是低于2 MHz寬的部分,并且發生在2 × HMC7044主機時鐘處——在該頻率下,沒有任何分頻器組合可以改善IBS性能。下文提供替代解決方案。

圖4. HMC7044、ADF5355和HMC704的測量與仿真結果。注意ADIsimFrequencyPlanner正確仿真了不可優化的較窄頻率范圍。在其它大部分頻率處,測量受限于頻譜分析儀的噪底。

只有在一個非常窄的頻率范圍內,優化PFD頻率才無法改善IBS性能。該頻率范圍是系統主時鐘的兩倍(本例中為2949.12 MHz × 2 = 5898.24 MHz)。在此頻率下,如果應用可行的話,建議將載波頻率轉換至附近更為干凈的頻率,然后將基帶頻率轉換至數字 (NCO) 以補償。例如,載波頻率偏移2 MHz,然后將數字基帶頻率偏移2 MHz以補償。此外,如果系統可行的話,可改變主機時鐘頻率,創造干凈的輸出頻率。

如果采用上述較為簡單的解決方案(使用HMC832或ADF4351而非HMC7044),那么就不會產生任何有問題的頻率!

由圖4可以看出,ADIsimFrequencyPlanner可以:

精確仿真整數邊界雜散。

成功優化參考源和PLL/VCO系統,以便實現出色的整數邊界雜散性能。

這樣可以在某個范圍內使更多通道可用,從而提升昂貴頻譜的成本價值。

快速仿真寬頻率范圍。如進行手動處理的話,可能需要數天或數周。上文中的6000個步進在ADIsimFrequencyPlanner中處理只需花不到1分鐘的時間。

責任編輯:gt

電子發燒友App

電子發燒友App

評論