集電極開路電路、集電極開路晶體管電路、集電極開路工作原理、集電極開路TTL、集電極開路輸出接線圖、集電極開路優缺點。

2023-02-01 08:59:17 529

529 今天給大家分享的是:集電極開路電路、集電極開路晶體管電路、集電極開路工作原理、集電極開路TTL、集電極開路輸出接線圖、集電極開路優缺點。

2023-02-06 11:54:41 2842

2842

今天給大家分享的是:集電極開路電路、集電極開路晶體管電路、集電極開路工作原理、集電極開路TTL、集電極開路輸出接線圖、集電極開路優缺點。

2023-07-17 09:03:55 2322

2322

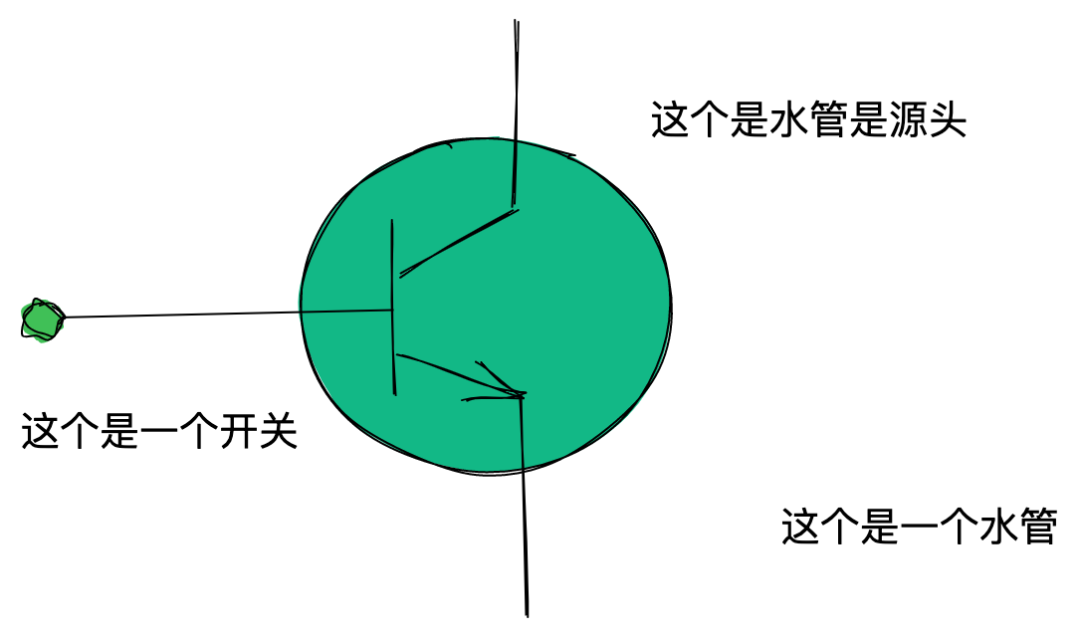

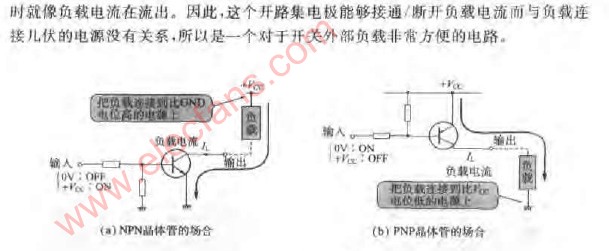

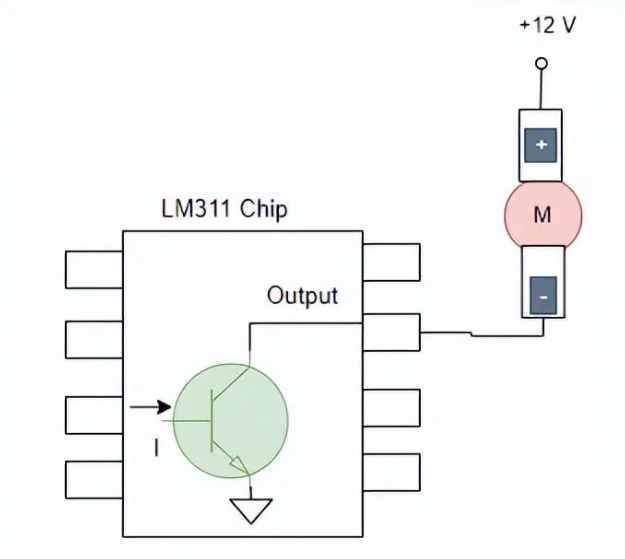

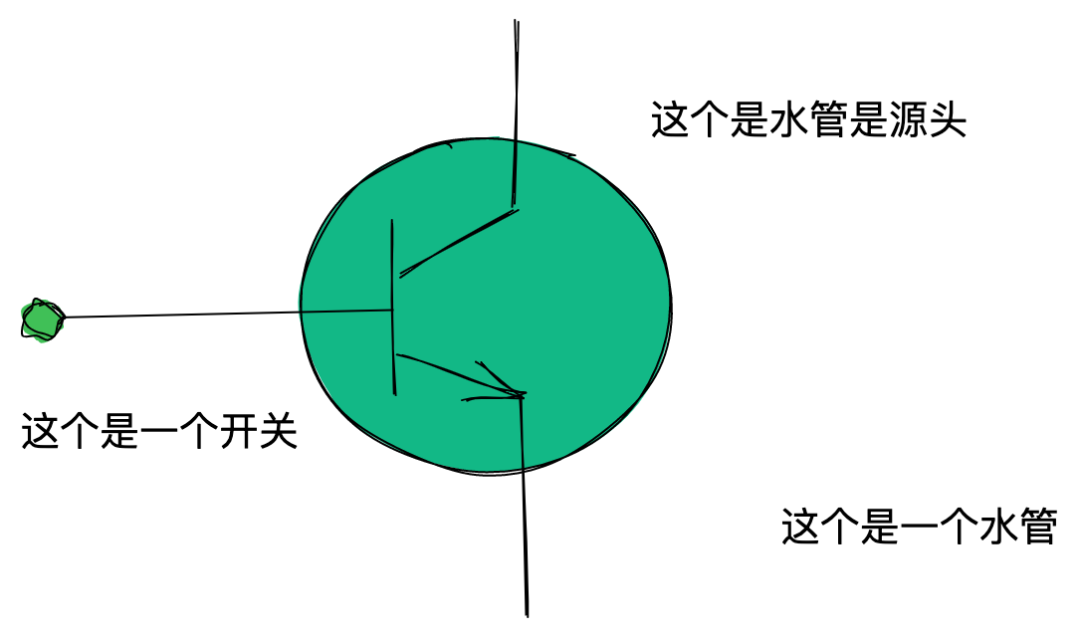

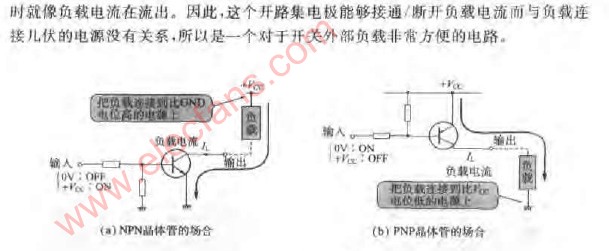

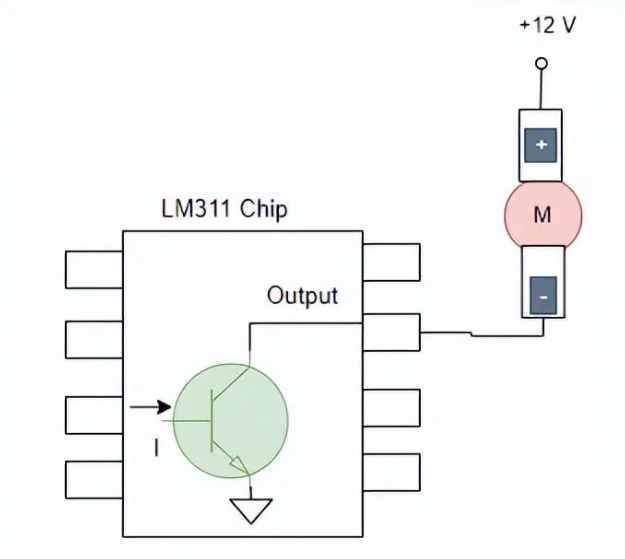

集電極開路就像是一個開關,其一端連接電源或接地。集電極開路電路常用在集成電路的輸出,其輸出可以根據使用的晶體管類型(NPN型或PNP型)為外圍提供灌電流和拉電流能力。

2023-07-21 10:00:28 793

793

漏極開路上拉電阻取值為何不能很大或很小?開關電源布線注意哪些?為何用萬用表量電路板的電阻時需斷電?

2021-11-12 07:59:46

地在MOS管的漏-源穩態截止電壓上,出現電壓尖峰。我的問題如下【1】MOS管的漏極就是相當于三極管的集電極,為什么要說成漏極,漏這個說法我一直不明白?【2】經常可以看到說變壓的漏磁,漏磁通,或者電感的漏感,怎么理解這些定義?【3】上文說的,漏磁通下降了,漏感就任然可以釋放儲能,是根據什么?謝謝

2017-07-22 11:57:00

集電極開路 漏極開路 推挽 上拉電阻 弱上拉 三態門 準雙向口

2016-06-02 16:22:21

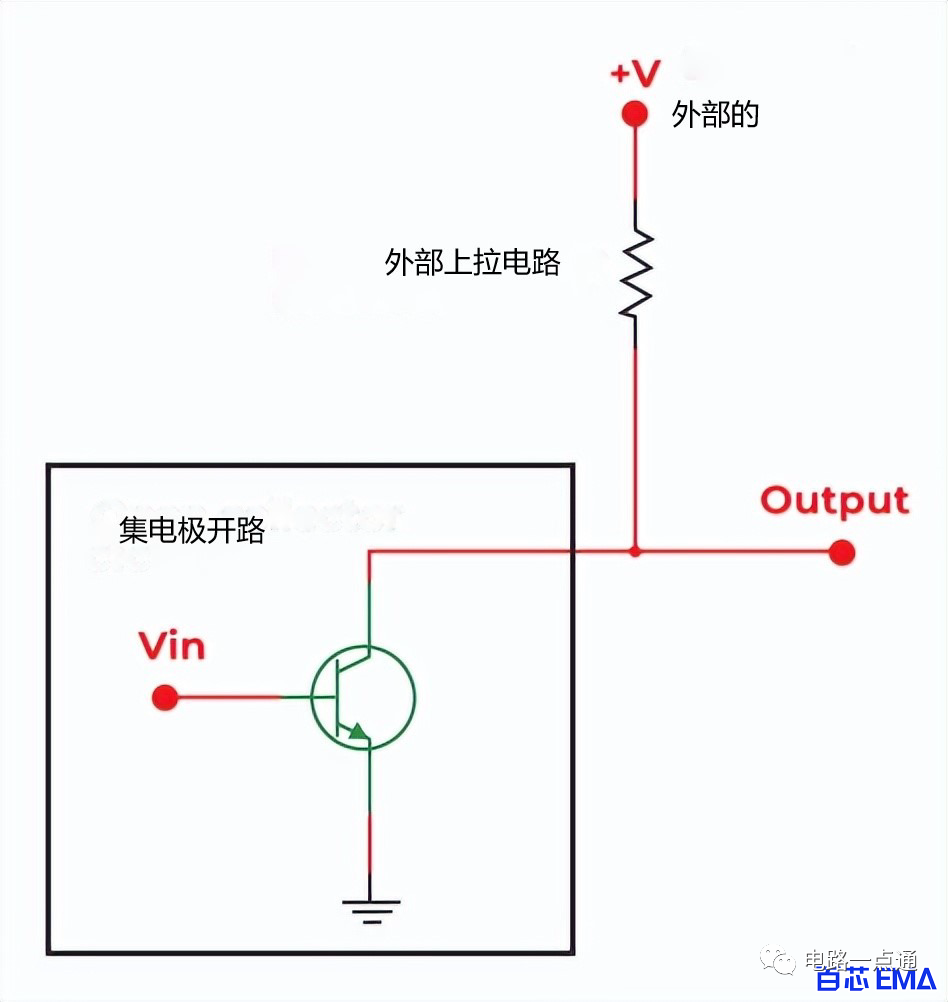

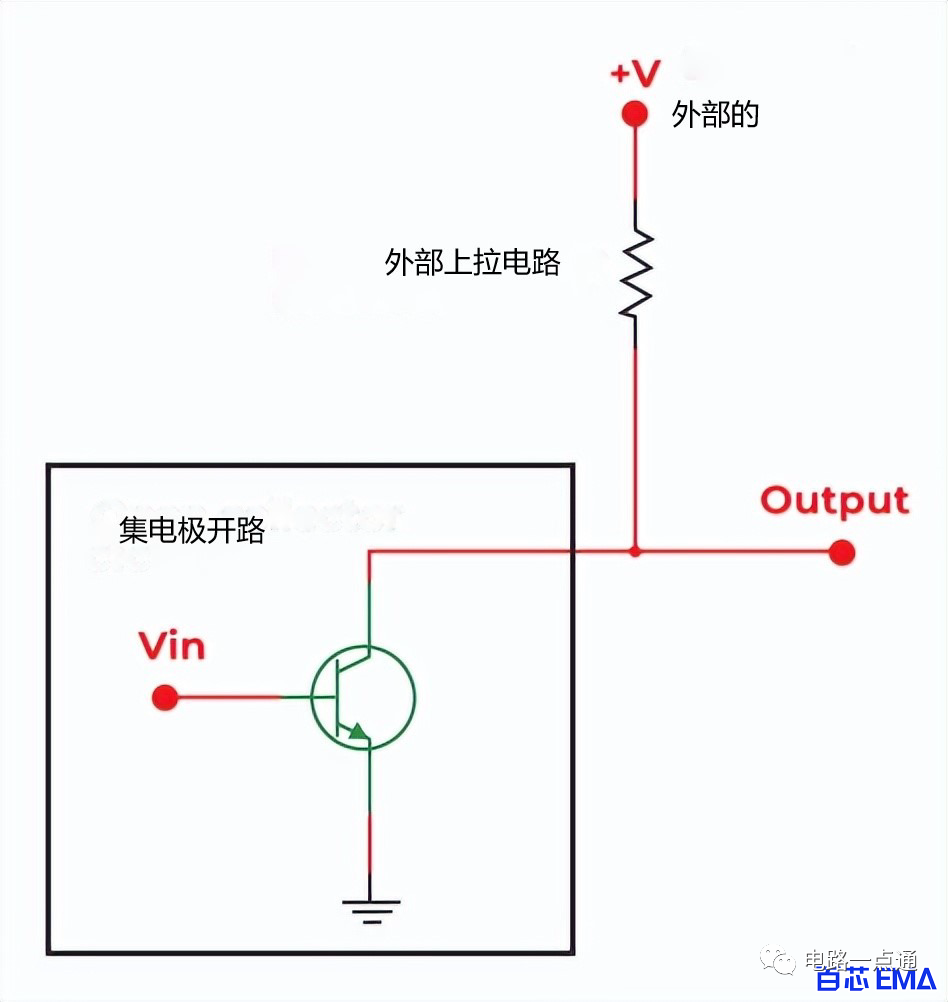

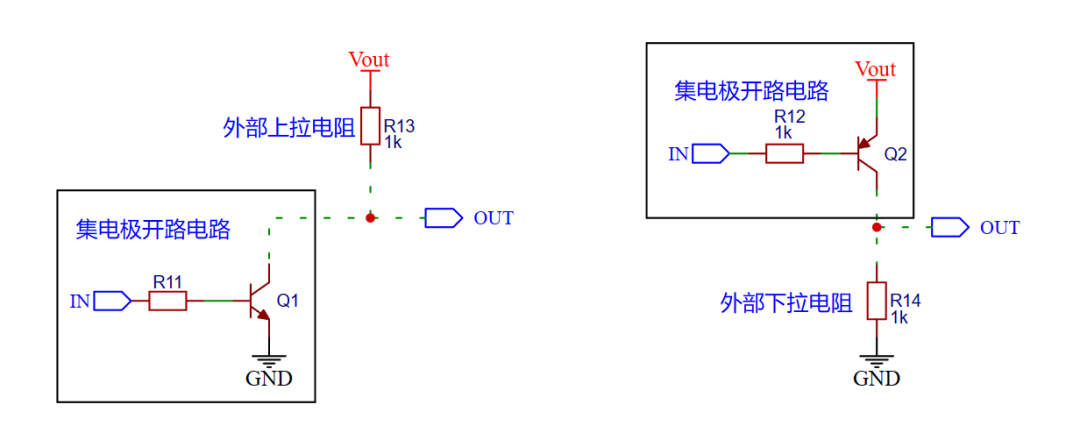

上拉就是通過一個電阻將芯片的一個引腳或線路中的一點接電源正極(Vcc),將該處電平拉向高電平。下拉就是通過一個電阻將芯片的引腳或線路中的一點接地,將該處電平拉向低電平。其主要目的是在電路驅動器關閉時給引腳或線路節點一個固定的默認的電平。上拉電阻有時還用來增加輸出引腳的驅動能力。當所接電阻值比較大時稱為弱上拉或弱下拉,否則就是強上拉或強下拉。上拉電阻應用比較普遍,大部分OC或OD輸出都需要接上拉電阻。單片機的大部分I/O引腳也配備了弱上拉電阻。

2019-05-20 11:15:28

1、集電極開路輸出上拉電阻電路為什么會速度降低和噪聲變大?在此基礎出引出了三態門?

2、多集電極開路上拉電阻輸出實現了線或結構,有高為低,全低為高。那么什么電路結構可以實現線與結構,射極跟隨,推挽,互補或者其他簡單輸出電路?

2024-01-28 16:32:00

三極管的原理光敏二極管的原理集電極電流Ic的形成

2021-03-10 07:36:40

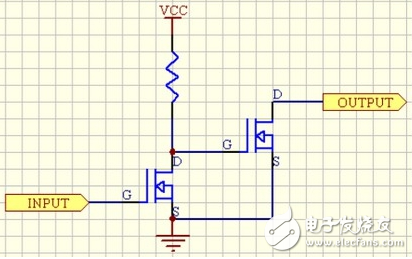

斷開,而對于P0口來說,就是高阻態了。對于漏極開路(OD)輸出,跟集電極開路輸出是十分類似的。將上面的三極管換成場效應管即可。這樣集電極就變成了漏極,OC就變成了OD,原理分析是一樣的。另一種輸出結構

2016-06-29 11:11:00

斷開,而對于P0口來說,就是高阻態了。對于漏極開路(OD)輸出,跟集電極開路輸出是十分類似的。將上面的三極管換成場效應管即可。這樣集電極就變成了漏極,OC就變成了OD,原理分析是一樣的。另一種輸出結構是推挽

2017-03-21 09:20:02

推挽輸出:可以輸出高,低電平,連接數字器件;開漏輸出:輸出端相當于三極管的集電極. 要得到高電平狀態需要上拉電阻才行. 適合于做電流型的驅動,其吸收電流的能力相對強(一般20ma以內).推挽結構一般

2022-02-08 06:50:38

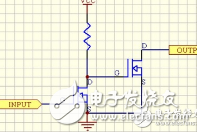

即可。這樣集電極就變成了漏極,OC就變成了OD,原理分析是一樣的。另一種輸出結構是推挽輸出。推挽輸出的結構就是把上面的上拉電阻也換成一個開關,當要輸出高電平時,上面的開關通,下面的開關斷;而要輸出

2017-10-12 10:41:10

開關斷開,而對于P0口來說,就是高阻態了。 對于漏極開路(OD)輸出,跟集電極開路輸出是十分類似的。將上面的三極管換成場效應管即可。這樣集電極就變成了漏極,OC就變成了OD,原理分析是一樣的。 另一種

2018-03-20 16:19:06

端口需要配置為漏極開路輸出或集電極開路輸出,請問該怎么用啊沒有相關的寄存器可以配置輸出模式

2018-08-13 06:41:32

我使用 xmc7100 芯片,使用 pwm 功能時,我需要將引腳配置為開路和漏極輸出。 當我沒有連接上拉電阻器時,示波器會檢測到應該沒有波形,但是有波形表明開路和漏極輸出配置不成功,為什么不呢? 能否將 pwm 引腳配置為開路和漏極輸出?

2024-01-23 06:34:37

本帖最后由 gk320830 于 2015-3-4 23:25 編輯

【經典】集電極開路,漏極開路,推挽,上拉電阻,弱上拉,三態門,準雙向口

2012-07-29 21:17:03

什么是集電極開路(OC)?什么是漏極開路(OD)?

2021-03-10 06:35:21

推挽輸出:可以輸出高,低電平,連接數字器件;推挽結構一般是指兩個三極管分別受兩互補信號的控制,總是在一個三極管導通的時候另一個截止.開漏輸出:輸出端相當于三極管的集電極. 要得到高電平狀態需要上拉

2021-11-24 07:22:11

單片機I/O開漏輸出詳解開漏輸出:輸出端相當于三極管的集電極. 要得到高電平狀態需要上拉電阻才行. 適合于做電流型的驅動,其吸收電流的能力相對強(一般20ma以內).我們先來說說集電極開路輸出的結構

2021-11-24 08:11:44

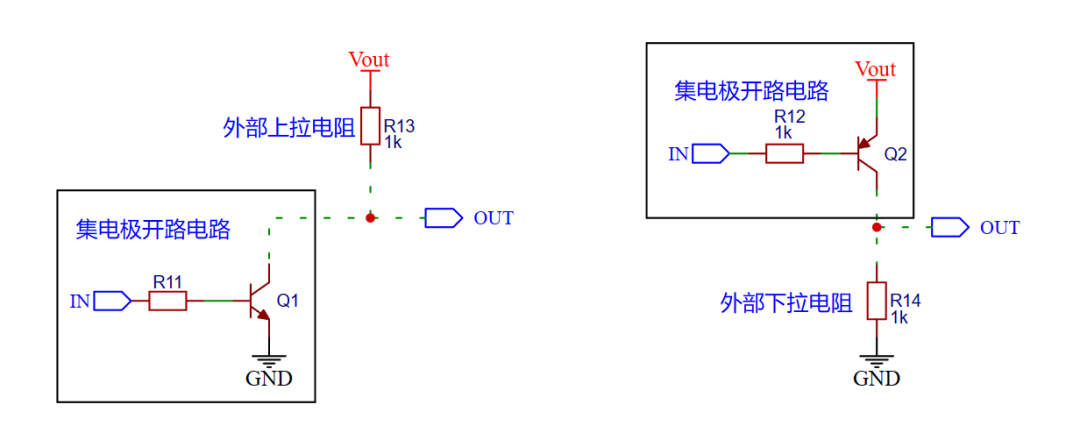

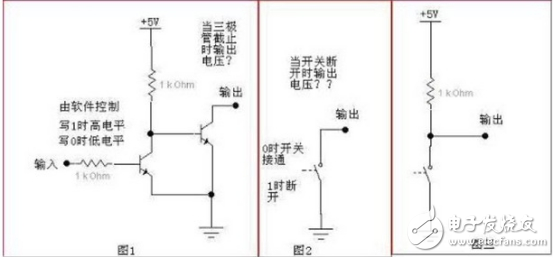

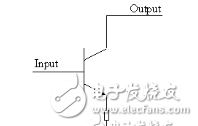

1.什么是源型 漏型?什么是上拉電阻?下拉電阻?什么是 線驅動輸出 集電極開路輸出,推挽式輸出?我們先來說說集電極開路輸出的結構。集電極開路輸出的結構如圖1所示,右邊的那個三極管集電極什么都不接

2021-07-15 09:15:48

本帖最后由 zhihuizhou 于 2011-11-2 10:20 編輯

集電極開路、漏極開路、推挽、上拉電阻、弱上拉、三態門、準雙向口集電極開路輸出的結構如圖1所示,右邊的那個三極管集電極

2011-11-02 10:20:11

你好,我使用的是PIC16F18854和開放漏極輸出模式,我的問題是開放漏極泄漏電流似乎沒有在數據表中指定。指定了輸入漏電流(D340,D341),但是沒有提到開路漏極。端口部分中的電路顯示通過

2020-03-11 06:35:45

的IIC引腳設置為漏極開路。我讀了ug471:7系列fpga selectedIO資源, ug768:7系列硬盤 ug865:zynq-7000-pkg-pinout但我沒有找到將iic引腳設置為漏極開路的方法。你可以幫幫我嗎?謝謝。

2020-05-14 06:37:27

我正在連接一個5V PIC18到2.5V設備。PIC18上的一些輸出可以是開路漏極。我非常熟悉漏極/開路集電極輸出,并使用了很多年。然而,說明書上的措辭有點麻煩。從PIC18F66K80系列說明書第

2020-05-12 10:28:10

我正在嘗試清理我們的代碼,現在正在查看我們的代碼,該代碼將兩個 RMT 通道(一個輸入,一個輸出)配置為在同一引腳上工作,輸出為漏極開路。我想我明白其中的大部分內容,但我不明白為什么我們需要設置

2023-03-02 08:25:00

我正在使用 NUCLEO-L552ZE-Q 并制作了一個非常簡單的測試電路來測試漏極開路輸出信號。我將引腳配置為漏極開路輸出,沒有上拉或下拉,信號通過 1K 電阻上拉至 3.3V。當我設置引腳時,我

2022-12-27 06:13:19

用運算放大器和三極管組成的恒流電路,想加上開路檢測,檢測到開路時輸出高電平(或者是低電平)

2013-04-13 22:36:27

你好。我用的是STM32G071GBU6,VDD電壓我設計成1.8V。我有一些關于董事會的問題。1. 3.3V GPIO 輸出控制- 我是否應該將 MCU 的 GPIO 引腳設置為漏極開路并連接它

2022-12-07 08:43:22

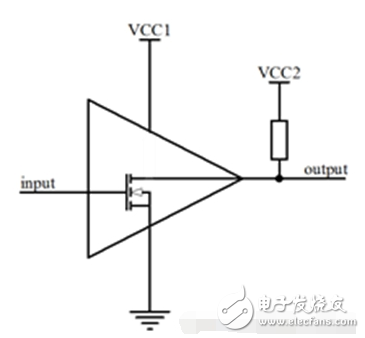

1.1.1 接口相關電路及概念1. 集電極開路輸出在電路中常會遇到漏極開路(Open Drain)和集電極開路(Open Collector)兩種情形。漏極開路電路概念中提到的“漏”是指

2022-01-14 07:57:32

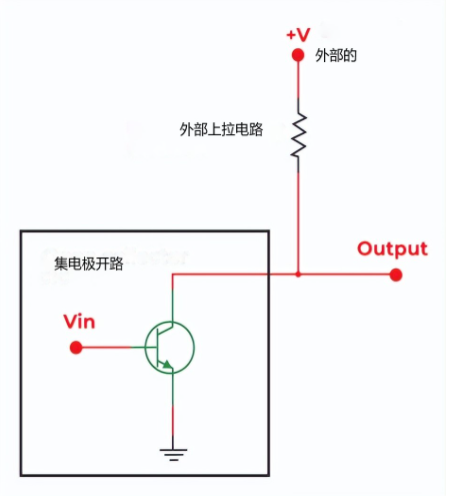

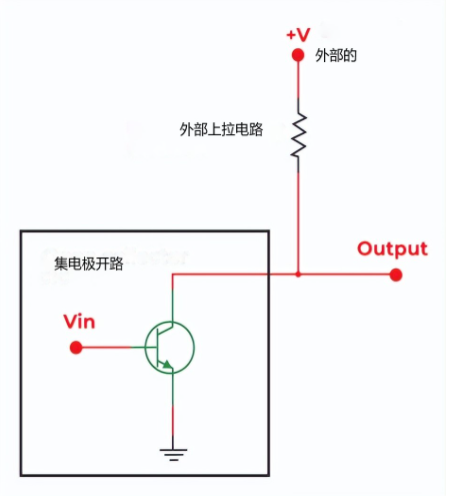

的,Vcc也要在數據手冊規定的范圍內。集電極或者漏極開路輸出引腳是由一個晶體管控制的,當晶體管關閉時,輸出引腳為懸空狀態(開路或者高阻態)。一個常見的列子就是當N溝道晶體管導通時,輸出信號接地,但關斷時,輸出

2019-04-23 08:00:00

集電極開路輸出結構與推挽輸出結構有什么不同?開漏電路有哪些特點?在使用開漏電路時有哪些注意事項?

2021-04-19 10:41:41

以前記三極管的何為發射極和集電極的時候都是死記硬背的,如下圖帶箭頭的是e也就是發射極但是今天看到IGBT的原理圖PNP的箭頭處是集電極,于是就搞不太清楚這集電極和發射極的命名搜了網上說的 發射極即

2019-03-04 15:51:00

求助電路分析見下兩圖:MCU信號到集電極是高電平三極管導通嗎?

2020-08-26 11:06:09

1.什么是源型漏型?什么是上拉電阻?下拉電阻?什么是線驅動輸出集電極開路輸出,推挽式輸出?我們先來說說集電極開路輸出的結構。集電極開路輸出的結構如圖1所示,右邊的那個三極管集電極什么都不接,所以叫做

2021-11-23 07:22:08

推挽輸出:可以輸出高,低電平,連接數字器件;開漏輸出:輸出端相當于三極管的集電極. 要得到高電平狀態需要上拉電阻才行. 適合于做電流型的驅動,其吸收電流的能力相對強(一般20ma以內).推挽結構一般

2021-11-03 06:28:05

共集電極三極管能放大電壓,而三極管本身就是可以放大電流的,這樣應該來說共集電極接法的三極管能夠進行功率放大,可是好像書上不是這樣的,請問我的錯誤在哪?

2017-05-28 17:13:31

當三極管為開路輸出時,三極管集電極通過一個負載,再從負載另一端接到電源,-----------------------------通常我們稱為集電極開路輸出。那么三極管為發射極這邊來接負載時,這個

2019-08-01 00:03:31

請問各位:如何在QUARTUS II里將EPM1270的管腳配置為漏極開路?

2021-04-13 15:48:08

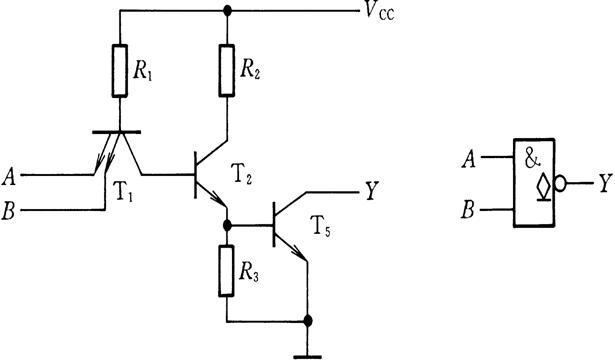

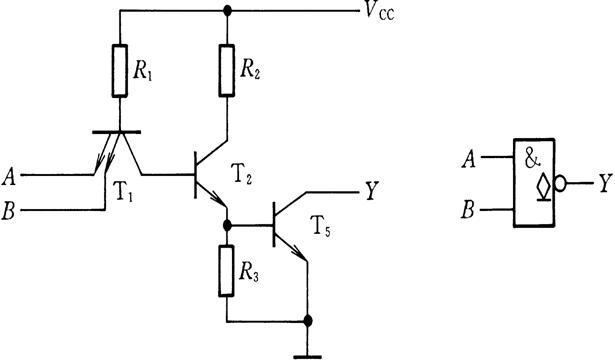

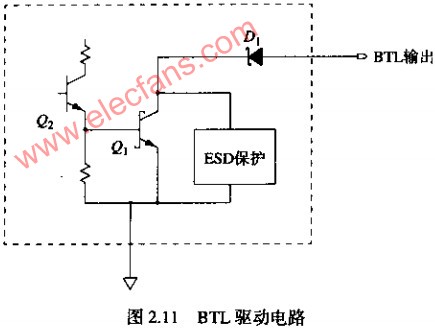

集電極開路門和三態輸出門的應用

一、 實訓目的1.熟悉集電極開路門(OC門)和三態輸出門(TSL門)的邏輯功能;2.熟悉用OC門構成線與功能;3.熟悉用TSL門

2009-04-07 23:23:53 59

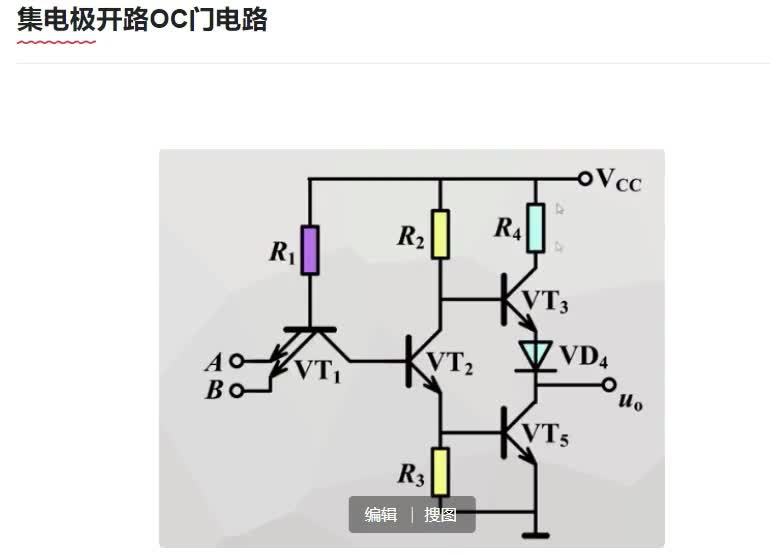

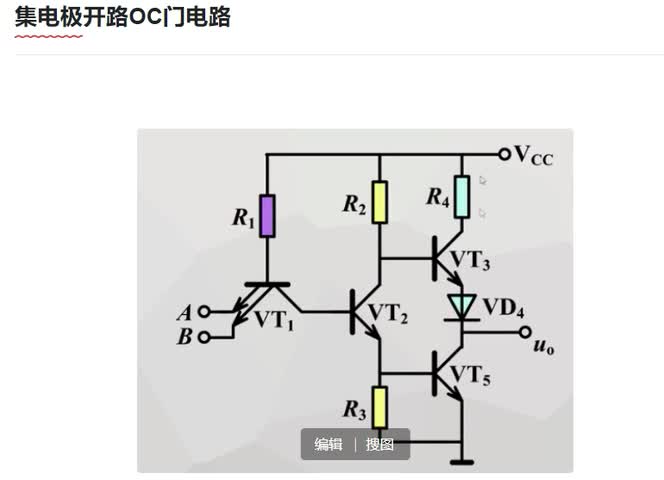

59 我們先來說說集電極開路輸出的結構。集電極開路輸出的結構如圖1所示,右邊的那個三極管集電極什么都不接,所以叫做集電極開路(左邊的三極管為反相之用,使輸入為“0”時,

2010-08-14 17:15:55 136

136 TTL或非門、集電極開路門和三態門電路

1.TTL或非門

下圖為TTL或非門的邏輯電路及其代表符號。

2009-04-07 00:11:59 14317

14317

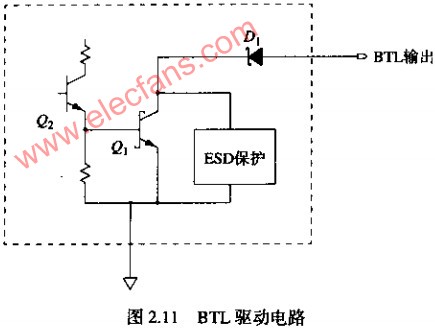

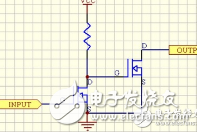

集電極開路門

在工程實踐中將兩個門的輸出端并聯以實現與邏輯的功能稱為線與。 考察下圖所示的情況。當將圖中所示的兩個邏輯門的輸出連接在一起,并且

2009-04-07 00:15:19 20553

20553

集電極開路與非門的電路和圖形符號

2009-07-15 19:02:06 7870

7870

開路集電極電路圖

2009-08-15 17:27:30 864

864

什么是漏極開路(OD)? 對于漏極開路(OD)輸出,跟集電極開路輸出是十分類似的。將上面的三極管換成場效應管即可

2010-03-04 15:37:00 51861

51861 漏極開路(OD)原理說解

漏極開路(OD),它與集電極開路(OC)是一致的,就是把下圖的三極管改成CMOS管就是了。

2010-03-04 15:38:44 3052

3052 集電極開路(OC)/漏極開路(OD)輸出的結構

A:我們先來說說集電極開路輸出的結構。集電極開路輸出的結構如圖1所示,右邊的那個

2010-03-04 15:41:39 2810

2810 用來計算TTL集電極開路輸出電路靜態功耗的公式如下:

其中:VT=上拉電阻的有效

2010-06-01 16:17:42 2549

2549

通過比較平衡電位和穩定電位的區別,進一步闡述了電池的電動勢與開路電壓的本質區別。討論了各類鋅錳電池開路電壓的構成及其影響因素,以及生產過程中常見的開路電壓問題。

2011-05-16 18:07:12 28

28 2012-11-23 21:49:17 4

4 2012-12-18 14:34:37 13

13 集電極開路_漏極開路_推挽_上拉電阻_弱上拉_三態門_準雙向口,感興趣的小伙伴們可以瞧一瞧。

2016-11-16 18:32:35 0

0 介紹了什么是集電極開路,漏極開路,推挽上拉,電阻弱上拉,三態門。

2017-02-28 22:08:40 1

1 在電路中常會遇到漏極開路(Open Drain)和集電極開路(Open Collector)兩種情形。漏極開路電路概念中提到的“漏”是指 MOSFET的漏極。同理,集電極開路電路中的“集”就是指三極管的集電極。在數字電路中,分別簡稱OD門和OC門。

2017-11-09 12:11:00 30603

30603

三極管導通時,集電極輸出低電平;三極管關斷時,集電極輸出懸空,因此該電路在工作時需要外接負載電阻和電源。只要電阻的阻值和電源電壓的數值選擇得當,就能夠做到既保證輸出的高、低電平符合要求,輸出端三極管的負載電流又不過大。

2017-11-09 12:17:53 145604

145604

漏極開路(OD)輸出,跟集電極開路輸出是十分類似的。將上面的三極管換成場效應管即可。這樣集電極就變成了漏極,OC就變成了OD,原理分析是一樣的。對于漏極開路(OD)來說,輸出端相當于三極管的集電極。 要得到高電平狀態需要上拉電阻才行。 適合于做電流型的驅動,其吸收電流的能力相對強(一般20ma以內)。

2017-11-09 14:17:01 17820

17820

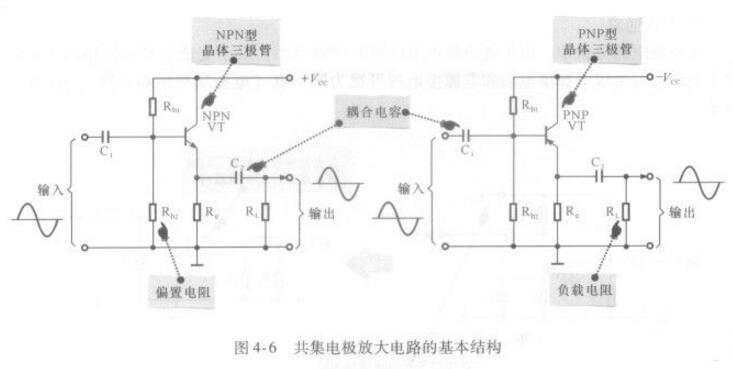

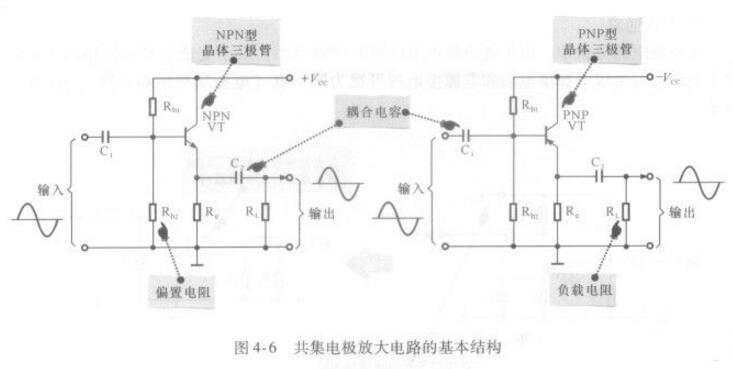

本文開始闡述了什么是共集電極電路和共集電極放大電路的基本結構,其次闡述了共集電極放大電路的功能與工作原理,最后介紹了共集電極放大電路的特性及詳細的共集電極放大電路計算與分析。

2018-03-27 14:06:52 203764

203764

該裝置包含六個獨立的門,每個門執行緩沖功能。開路集電極輸出需要外部上拉電阻才能正常邏輯操作。

2019-04-24 08:00:00 1

1 集電極開路輸出端或者MOS管漏極輸出端其性質都是一樣的,這種電路在數字電路中都要加上拉電阻。比如在單片機P0口其內部驅動電路是MOS構成的,其結構就是一個漏極開路電路,其內部沒有上拉電阻。

2019-09-28 07:00:00 8622

8622 PmodOC1是使用MMBT3904晶體管的集電極開路BJT模塊。

2019-11-29 14:38:33 1351

1351

本文首先介紹了開路電壓的概念,其次介紹了開路電壓的計算方法,最后闡述了開路電壓的影響因素。

2020-08-14 09:25:55 51230

51230 A、開路集電極NPN的接線方式,采用內部電源(由于采用內部電源,所以“+24V”和“PLC”的短接片必須連接可靠,而且電流的流向為從“+24V”到“PLC”到控制板內部整理電路,再到“Xi”端子,經過外部接點后回到變頻器的“COM”端子):

2020-11-11 08:00:00 1

1 電子發燒友網為你提供什么是集電極開路(OC)?什么是漏極開路(OD)?資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-13 08:42:31 9

9 DM5438/DM7438緩沖器集電極開路輸出資料手冊免費下載。

2021-06-01 17:51:18 11

11 1.什么是源型漏型?什么是上拉電阻?下拉電阻?什么是線驅動輸出集電極開路輸出,推挽式輸出?我們先來說說集電極開路輸出的結構。集電極開路輸出的結構如圖1所示,右邊的那個三極管集電極什么都不接,所以叫做

2021-11-15 13:51:02 0

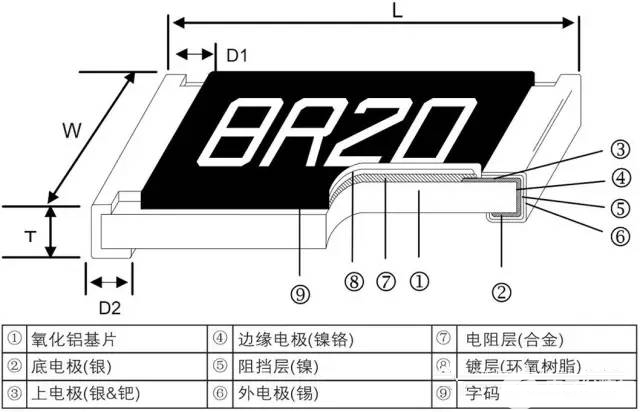

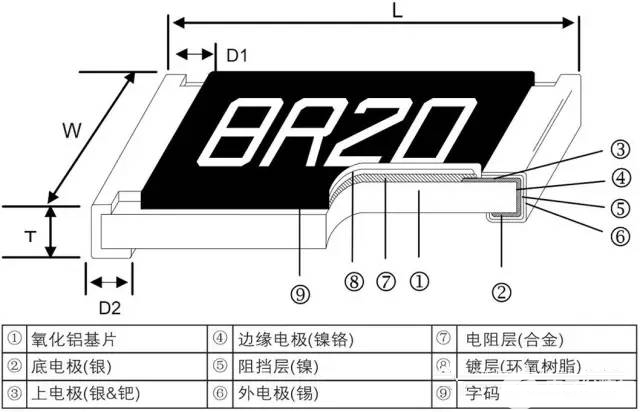

0 下圖為貼片電阻結構圖: 失效背景:電阻開路 問題分析:從失效樣品圖片來看,電阻本體沒有電應力和結構損傷。如果沒有電應力和結構損傷,一般是由于電極開路造成的失效,確定好失效模式和機理就可以針對性進行

2021-12-11 10:11:59 2702

2702

1.1.1 接口相關電路及概念1. 集電極開路輸出在電路中常會遇到漏極開路(Open Drain)和集電極開路(Open Collector)兩種情形。漏極開路電路概念中提

2022-01-14 14:32:40 23

23 如果開關斷開,則由于開關電阻為無窮大(不考慮實際中的漏電流),所以流過的電流為0,因此在1k電阻上的壓降也為0,所以輸出端的電壓就是5v了,這樣就能輸出高電平了。

2022-08-31 14:18:39 1925

1925 因此集電極開路的輸出視為NPN晶體管,它允許電流吸收到公共端。對于這樣集電極開路電路,必須有一個電源才能使輸出正常工作。當我們要求未連接任何電源時計算輸出電壓時,電壓不會發生變化。必須計算輸出端的電壓以了解集電極開路電路的正常運行。

2023-01-08 15:03:01 2856

2856 今天給大家分享的是:集電極開路電路、集電極開路晶體管電路、集電極開路工作原理、集電極開路TTL、集電極開路輸出接線圖、集電極開路優缺點。

2023-01-13 09:48:30 908

908 集電極開路是各種集成電路中常見的輸出。集電極開路就像一個接地或斷開的開關。除了將IC或任何其他晶體管的輸出連接到特定設備外,還連接到NPN晶體管的集電極開路的基極端子,NPN晶體管的發射極端子與接地引腳內部連接。

2023-01-16 09:16:28 756

756 何為集電極開路電路?集電極開路就像是一個開關,其一端連接電源或接地。集電極開路電路常用在集成電路的輸出,其輸出可以根據使用的晶體管類型(NPN型或PNP型)為外圍提供灌電流和拉電流能力。由于NPN

2023-07-31 23:07:05 890

890

ttl電路中推拉輸出,集電極開路輸出,三態輸出有何不同?? TTL電路是一種常見的數字邏輯電路,在電路中經常出現推拉輸出、集電極開路輸出、三態輸出這些術語。這些輸出方式在不同的電路中具有不同的意義

2023-08-31 10:32:19 2131

2131 開路電壓是什么意思? 開路電壓指的是在電路中沒有負載負荷的情況下,測量到的電源輸出的電壓大小。在沒有負載的情況下,電源輸出電壓的測量結果往往會比有負載時高出一定比例。 為了更好地理解開路電壓的概念

2023-12-12 14:09:47 3501

3501 集電極開路電路是一種常見的邏輯電路,它的特點是輸出端有一個開路的集電極。

2024-02-17 15:11:00 292

292

集電極開路是各種集成電路中常見的輸出。集電極開路就像一個接地或斷開的開關。除了將IC或任何其他晶體管的輸出連接到特定設備外,還連接到NPN晶體管的集電極開路的基極端子,NPN晶體管的發射極端子與接地引腳內部連接。

2024-02-15 09:24:00 179

179

pcb開路分析,這6個原因要注意

2024-02-21 16:43:39 181

181 集電極開路門的內部結構設計會直接影響其開關速度。例如,電極間的距離、材料選擇、通道長度等都會對開關速度產生影響。

2024-03-18 17:10:20 125

125

電子發燒友App

電子發燒友App

評論