引言

短波通信信道具有時變和色散的特性,并且容易受到噪聲干擾,所以模擬其傳輸特性,具有很高的實用價值。短波信道模擬器借助先進的仿真技術手段實現在實驗室環境下進行通信試驗,因其具有有效性、經濟性、安全性和直觀性等特點,在通信試驗中可廣泛使用。傳統的短波信道模擬器大部分停留在話音帶寬上,其主要不足是功耗過高、體積龐大、可控性不高及實時性不好。模數轉換器( A/ D)器件和數字信號處理理論的飛速發展,為研制寬帶短波信道模擬器奠定了堅實的基礎,但由于現有的數字信號處理器( DSP) 處理速度有限,往往難以對高速率A/ D 采樣得到的數字信號直接進行實時處理,為了解決這一矛盾,需要采用數字下變頻( DDC) 技術。所以數字下變頻技術在寬帶短波信道模擬器的數字化和軟件化過程中起到了重要的作用。FPGA 具有較高的處理速度和很強的穩定性,而且設計靈活、易于修改和維護,同時可以根據不同的系統要求,采用不同的結構來完成相應的功能,大大提高系統的適用性及可擴展性。因此,FPGA 逐漸成為實現DDC 的首選。

1 寬帶短波信道模擬器設計

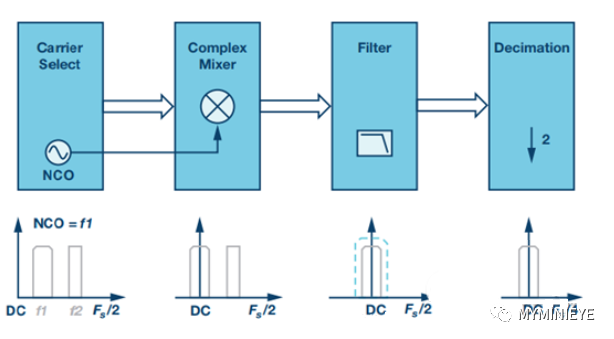

寬帶短波信道模擬器的輸入為短波調制信號( 3~ 30 MHz) ,首先經過高速A/ D 直接進行采樣,將模擬的調制信號轉換為數字信號,然后再通過數字下變頻技術分離出I、Q 兩路數字基帶信號,以便于后續的數字信號處理。信號處理中通過顯示控制設備對信道參數進行設置和輸出。最后處理好的信號再經過D/ A 轉換后,通過低通濾波器、放大器和程控衰減等設備輸出最終所需的模擬信號。這樣就大大降低了ADC 和DSP 器件性能的要求,減輕了數字信號處理的負擔,便于實現并有效降低成本。寬帶短波信道模擬器的體系結構如圖1 所示。

?

圖1 寬帶短波信道模擬器的體系結構圖

寬帶短波信道模擬器通過數字下變頻降低采樣數據率,減輕后續信號處理的壓力。數字下變頻在模擬器中起到前端ADC 和后端DSP 器件之間的橋梁作用。在數字下變頻部分中可以方便地對接收信號頻段和濾波器特性等進行編程控制,極大地提高了寬帶短波信道模擬器的性能和靈活性,對于系統的升級或是兼容,都非常方便。

2 基于FPGA 的數字下變頻實現方案

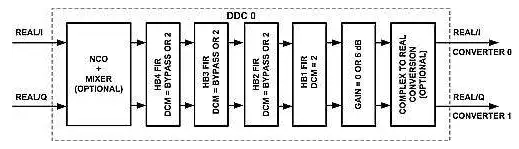

寬帶短波調制信號的輸入頻率為3~ 30 MHz,根據帶通采樣理論,在工程實現上,信號采樣速率一般為模擬信號帶寬的2. 5 倍左右,考慮到在器件滿足要求的前提下可以盡量提高采樣頻率,選用了64 MHz 作為ADC 的采樣頻率。經過數字下變頻的32 倍變頻,最終輸出到DSP 的信號帶寬為2 MHz。

該文中的DDC 實現不采用Altera 公司所提供的IP核,這樣可以降低成本,減少對國外技術依賴。

FPGA 器件采用cyclone III 器件,它是Altera 公司新一代采用SRAM 工藝低成本的FPGA,該系列器件的特點是低成本、低功耗和高性能。具有嵌入式乘法器,實現專門的乘法和乘加運算,還可實現有限脈沖響應( FIR) 濾波器; 最多有20 個全局時鐘,支持動態時鐘管理以降低用戶模式時的功耗; 并且有4個鎖相環( PLL) 。根據該設計的數據處理要求,估算處理所需的資源,以及引腳封裝有利于制板的原則,選用EP3C40Q240C8N 型FPGA,并在開發工具Quartus II 上對信號發生器的設計、綜合及仿真。

NCO 是決定DDC 性能的主要因素之一。NCO的目標是產生頻率可變的正交正、余弦樣本信號。

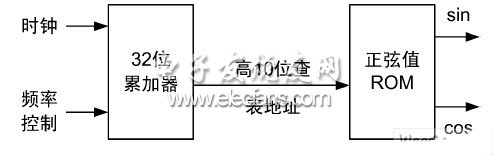

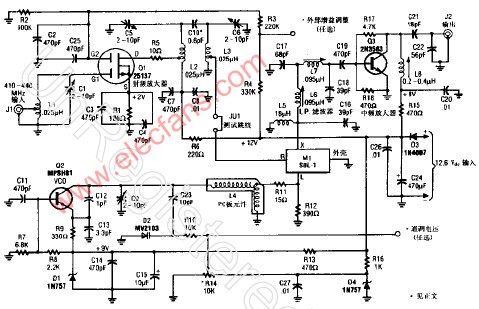

NCO 采用直接數字合成( DDS) 的方法實現,目前常見的技術有查表法和CORDIC 計算法,在軟件無線電超高速的信號采樣頻率的情況下,NCO 實時的計算方法是很難實現的。此時,NCO 產生的正弦樣本最有效和最簡單的方法就是查表法,即事先根據各個NCO 正弦波相位計算好相位的正弦值,并按相位角度作為地址存儲該相位的正弦值數據,其原理圖如圖2 所示。

?

圖2 基于查表法的NCO 原理圖

圖2 中,32 位累加器由一個32 位的加法器和一個32 位寄存器組成,在時鐘的作用下,加法器通過寄存器將輸出數據送入到加法器的一個輸入端,與32 位的頻率控制字進行相加運算,得到一個有規律的相位累加結果。查找表實際上是一個存儲了正弦信號抽樣點幅度編碼的只讀存儲器ROM,但ROM表的大小會隨地址位數的增加成指數遞增關系,因此,為了不減少查找表的地址位數而滿足信號性能,必須采用優化方法來減小ROM 表的大小。根據正弦波的對稱特性,只需存儲四分之一周期的幅值,再通過相應的轉換即可恢復出整個周期的幅值。同時,由于余弦波和正弦波相位差為??/ 2,可以很容易地實現余弦信號。

完成DDC 的NCO 模塊設計后,將需要下變頻的輸入信號與NCO 產生的2 路正交本振信號進行相乘,完成數字混頻正交變換,即完成頻譜搬移。

2. 2 CIC 濾波器設計

CIC 積分梳狀濾波器是實現高速抽取非常有效的單元。CIC 濾波器的單位沖激響應為:

?

?

?

從式( 2) 可以看出CIC 濾波器由2 部分組成,即積分器和梳狀器級聯組成,其實現非常簡單,只有加減運算,沒有乘法運算,FPGA 實現時可達到很高的處理速率。但是,單級CIC 濾波器的旁瓣電平只比主瓣低13. 46 dB,這就意味著阻帶衰減很差,一般是難以滿足實用要求的。為了降低旁瓣電平,可以采取多級CIC 濾波器級聯的辦法解決。

N 級CIC 濾波器級聯的帶內容差是單級CIC 濾波器帶內容差的N 倍,這意味著多級CIC 濾波器級聯增大阻帶衰減的同時也增大了帶內容差。所以,CIC 濾波器的級聯數是有限的不宜超過5 級。

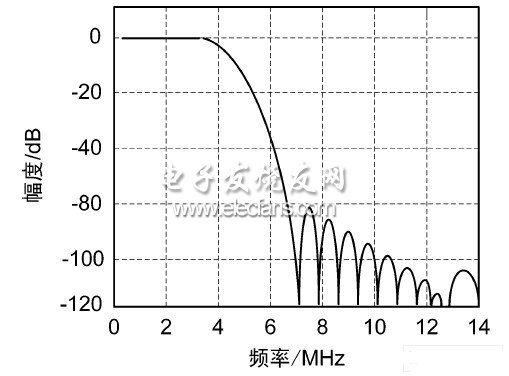

該設計中,CIC 濾波器需要完成16 倍的抽取,采用5 級級聯來實現,輸入和輸出部分的位寬均為12 bit,在MATLAB 仿真的結果如圖3 所示。

?

圖3 CIC 濾波器幅度特性

經過CIC 濾波器后,信號采樣速率經過16 倍抽取后變為4 MHz,從而實現了抽取功能,同時也降低了采樣速率。

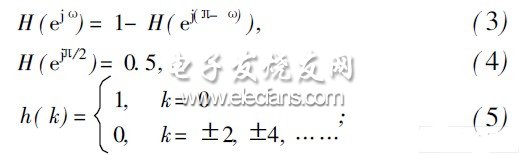

2. 3 半帶濾波器

所謂半帶濾波器,就是其頻率響應滿足以下關系的FIR 濾波器:

?

HB 濾波器由于其系數幾乎一半為0,濾波時運算量減少一半,因此被作為第2 級低通濾波和抽取。

HB 的抽取因子固定為2,特別適合采樣率降低一半的要求。通過CIC 和HB 濾波抽取后,基帶信號由最初的高數據率被降到較低的速率,適于后級FIR處理。

2. 4 FIR低通濾波器設計

數字下變頻器的最后一個模塊是低通FIR 濾波器,主要用來對信號進行整形濾波不作抽取功能。

信號經過CIC、HB 濾波器后,輸入到FIR 濾波器的采樣速率相對來說已經很低,因此在一定的處理時鐘速率下,能夠有較高階的FIR 濾波,使得濾波器的通帶波動、過渡帶帶寬、阻帶最小衰減等指標能夠設計的很好。

調用MATLAB 的Filter design 獲得濾波器的系數。在MATLAB 中設計一個通帶截止頻率為2 MHz的FIR,并將濾波器系數導入到FPGA 的FIR 中; FIR的階數( 系數長度) 越高,性能越好,但考慮資源占用情況,FIR 的階數不宜過高,該設計采用37 階FIR。

3 基于FPGA 的DDC 系統仿真結果

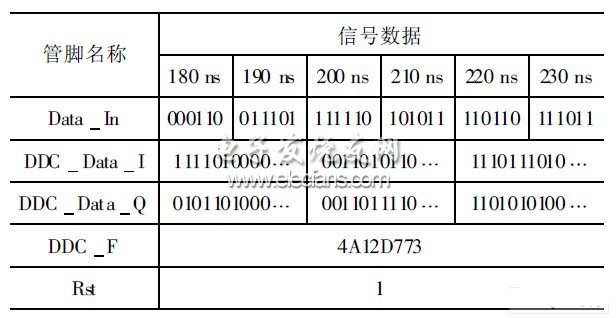

根據以上的設計分析結果,編寫了FPGA 程序,在Quartus II 平臺上進行了仿真測試。輸入采樣速率為64 MHz 的短波調制信號,針對Cyclone III 系列的EP3C40Q240C8 器件對其進行綜合與時序仿真,如表1 所示。

表1 DDC 實現的時序仿真圖

輸入信號經過混頻器后,再經過CIC 濾波器的16 倍抽取,半帶濾波器的2 倍抽取和FIR 濾波器的整形濾波,最終輸出I,Q 兩路正交的信號。如表1所示,Data In 為輸入信號,DDC Data I 為輸出同相分量,DDC Data Q 為輸出正交分量。64MHz 的采樣信號經過NCO 混頻后,CIC 濾波器的16 倍和HB 濾波器的2 倍抽取后,變為2 MHz 的信號,并經過FIR 濾波器整形輸出。從表1 中可以看出設計的DDC 對于高速采樣的信號具有降速和下變頻的作用,處理帶寬大大減小,因此對后續器件處理速度的要求降低。

仿真中還有一定量的毛刺,這是由于信號的延時控制不精準造成的。延時的大小不僅和連線的長短和邏輯單元的數目有關,而且也和器件的制造工藝和工作環境等有關,毛刺的消除是有待解決的問題。

4 結束語

在分析了寬帶短波信道模擬器工作機理和數字下變頻原理的基礎上,結合Matlab 算法仿真技術,設計基于FPGA 的數字下變頻。功能與時序仿真結果表明: 基于FPGA 設計實現的數字下變頻功能,其技術指標滿足寬帶短波信道模擬器的性能要求。該設計方法降低了對FPGA IP 核的依賴性,提高了DDC的處理速率,實現了數字載波控制和抽取濾波可編程,具有很大的靈活性和通用性,對于實現寬帶短波信道模擬器具有十分重要的意義,并且可以推廣用于其他需要進行下變頻的場合。

電子發燒友App

電子發燒友App

評論