用AD9850激勵的鎖相環頻率合成器

提出了一種DDS和PLL相結合的頻率合成方案,介紹了DDS芯片AD9850的基本工作原理、性能特點及引腳功能,給出了以AD9850作為參考信號源的鎖相環頻率合成器實例,并對該頻率合成器的硬件電路和軟件編程進行了簡要說明。

??? 關鍵詞:DDS 鎖相環 頻率合成器 數據寄存器

以DDS(直接數字合成)

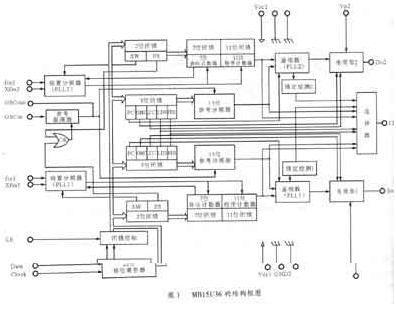

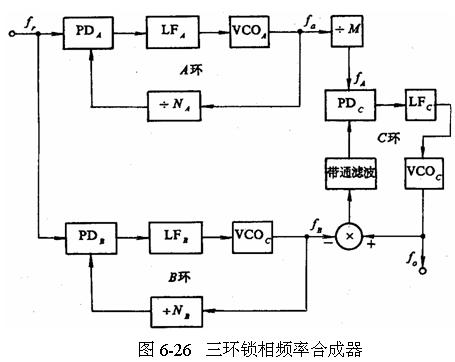

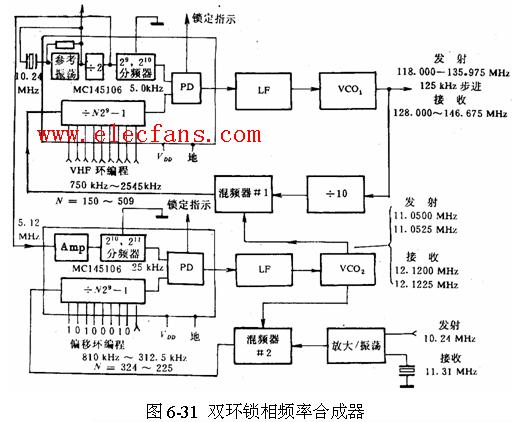

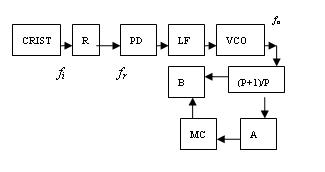

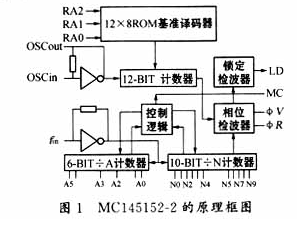

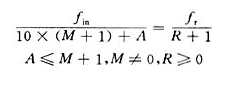

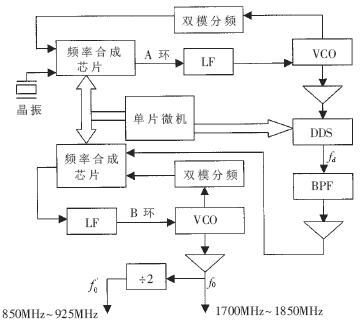

激勵的PLL(鎖相環)頻率合成器,是用DDS作為參考信號源,將DDS和PLL組合在一起的一種獨特的頻率合成器方案。它綜合了DDS和PLL頻率合成器的優點,具有極高的頻率分辨率、極短的換頻時間和較好的噪聲性能,而且頻率范圍寬、控制靈活,是應用于雷達、通信等領域中的一種較為先進的頻率合成方案。其電路原理框圖如圖1所示。

我們在實際工作中,以美國AD公司生產的DDS芯片AD9850和MITEL公司的PLL芯片SP8858為核心,完成了一款高性能的DDS+PLL的頻率合成器的設計與試驗,并將其應用于一無線測量接收機,收到了極好的效果。下面介紹AD9850的基本工作原理和引腳功能等,并給出頻率合成器實例的方案組成。

1 AD9850的工作原理與引腳功能

1.1 基本工作原理

AD9850采用先進的DDS技校,在內部集成了32位相位累加器、14位正/余弦查詢表和高性能的10位D/A轉換器以及一個高速比較器,其原理框圖見圖2。它通過并口或串口寫入的頻率控制字來設定相位累加器的步長大小,相位累加器輸出的數字相位通過查找正/余弦查詢表得到所需頻率信號的采樣值,然后通過D/A變換,輸出所需頻率的正弦波信號。還可以通過高速比較器將正弦波信號轉換成方波,作為時鐘信號輸出。

輸出信號的頻率FDDS由下式確定:

FDDS=Δf·FCLK/2 32???? (1)

式中,Δf為32位頻率控制字的值,FCLK為工作時鐘。

1.2 控制方式

AD9850內部的5個8位寄存器構成一個40位的數據寄存器,儲存來自外部數據總線的數據和控制字,其中32位為頻率控制字、5位為相位調制字、1位是電源休眠(power down)功能控制,另2位儲存工廠保留碼(用戶編程時,應將其設定為“00”)。寄存器可通過并行或串行方式裝載。

并行方式是在使能信號FQ_UD和寫脈沖WCLK的控制下,通過8位數據總線D0~D7分五次來完成全部40位數據的輸入,其工作時序圖見圖3。在FQ_UD的上升沿,40位數據從輸入寄存器打入數據寄存器,同時將地址指針復位到第一個輸入寄存器。隨后,在WCLK的上升沿寫入第一組8位數,并把指針指向下一個輸入寄存器。連續五次裝載以后,WCLK的上升沿無效,直到復位信號Reset有效或者FQ_UD的上升沿再次來到。

串行輸入方式如圖4所示,

在WCLK的上升沿,40位數據由低位到高位依次從引腳25(D7)移入到輸入寄存器,并在FQ_UD的脈沖作用下,一次性打入到數據寄存器,以便新芯片的輸入頻率(或相位)。

1.3 主要性能

(1)單電源工作:+3.3V或+5V。

(2)接口簡單,可用8位并行口或串行口直接裝載頻率和相位調制數據。

(3)片內直高性能D/A轉換器和高速比較器,可輸出正弦波和方波。

(4)最高工作時鐘125MHz,32位頻率控制字保證在125MHz的工作時鐘下頻率分頻率達0.0291Hz。

(5)5位調相控制字,可實現相位調制功能。

(6)頻率轉換速率極快,可達2.3×10 7次/秒。

(7)低功耗:在125MHz時鐘頻率、+5V電源工作時,功耗為380mW;110MHz時鐘、+3.3V工作時,功耗為155mW。

(8)工作溫度范圍寬:-40℃~+85℃。

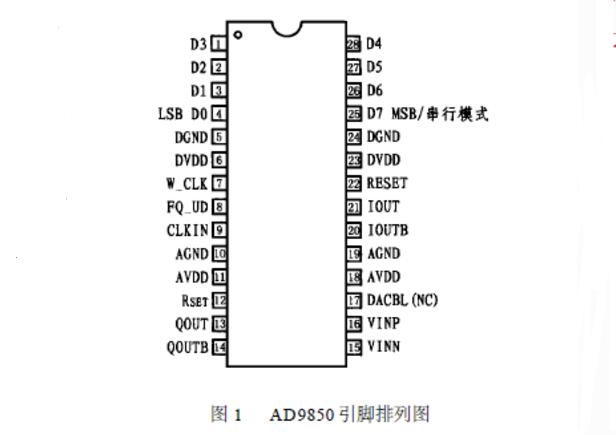

1.4 引腳功能

AD9850為28腳緊縮型小外形封裝(SSOP),其管腳排列見圖5,引腳功能如表1所示。

表1 引腳功能

?

| 引腳名稱 | 引? 腳? 功? 能 |

|

D0~D7 DGND DVDD WCLK FQ_UD CLK IN AGND AVDD Rset QOUT QOUTB VINN VINP DACBL IOUTB IOUT RESET |

8位數據輸入口,可分次并行裝載40位控制數據,D7(第25腳)也可以作為串行數據輸入端使用 數字地 數字電源 數據寫入脈沖 頻率刷新使能信號 外部參考時鐘輸入,可是CMOS電平的脈沖序列或者是加0.5VDD的直流偏置的正弦波信號 模擬地 模擬電源 D/A輸出電流Iout的控制電阻連接端,通常接一只3.9kΩ電阻到地。Iout=32×(1.248/Rset) 內部比較器輸出端 內部比較器互補輸出端 內部比較器的負向輸入端 內部比較器的正向輸入端 D/A內部的旁路端,通常懸空 D/A的互補輸出端 D/A的輸出端 復位端。高電平時將所有數據寄存器清零,并將地址指針指向W0,同時使輸入寄存器無效,相位累加器清零 |

2 用AD9850作參考信號源的PLL頻率合成器實例

2.1 硬件設計

本頻合器是一個頻率范圍1.6GHz~2.9GHz的頻率合成器,其硬件組成框圖如圖6所示。AD9850工作在100MHz參考時鐘下,產生16MHz左右的正弦波信號,其D/A轉換器的輸出經過一個中心頻率為16MHz、帶寬為4MHz的帶通濾波器之后,給PLL芯片SP8858提供鑒相標頻。SP8858是一種高性能的脈沖吞除式數字鎖相環頻率合成器芯片,其工作頻率高達1.5GHz,片內PD采用線性的數字鑒頻—鑒相器,最高鑒相頻率可達5MHz;內部還包括÷16/17(或÷8/9)的雙模前置分頻器,兩個15位的程序分頻器,一個4位的吞脈沖計數器和一個13位的參考分頻器。兩個程序分頻器數據緩沖器可輪流工作,有助地減少頻合器的換頻時間。外部的微處理器可通過對片內的三總線串行數據接口進行操作,來控制各分頻器的狀態和數據刷新。

AD9850和SP8858的置數由數字信號處理芯片TMS320C32的串口控制。在我們設計的無線測量接收機中,整個系統的控制和數字信號的處理由TMS320C32完成。為了簡化系統,將TMS320C32的串行用于頻率合成器的置數和頻率刷新。

環路濾波器是由低噪聲運放LT1028構成的有源二階低通濾波器,VCO由HE404B和HE486B兩只低噪聲壓控振蕩器分段組成,以覆蓋1.6GHz~2.9GHz的頻率范圍。VCO的輸出信號分成兩路,一路經放大和4分頻后送入SP8858進行程序分頻、鑒相;另一路經由RFIC芯片ERA-A放大后作為本振信號輸出。

2.2 軟件編程

軟件編程比較簡單,主要是根據AD9850和SP8858的控制字方式,由TMS320C32通過串口分別將相應控制字裝載到兩只芯片中去,以產生需要信號的頻率。

在本例中,SP8858主要控制信號頻率的粗調,其步進量Δf為4MHz;AD9850實現信號頻率的細調,控制其輸出頻率在16MHz附近變化,步進量接近1Hz。

SP8858的編程規則可參考文獻[2]。從系統的總體設計考慮,為了與SP8858的串行送數方式一致,AD9850的數據輸入方式也采用串行方式(此時,芯片的2腳應接地,3腳和4腳接VDD,數據從25腳輸入),串行裝載時40位數據的功能見表2,編程時應將“W2 W33 W34”置“000”。

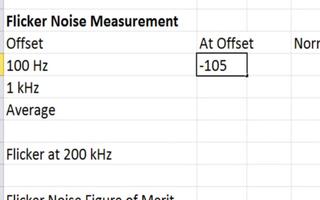

2.3 測試結果

采用此方案研制的頻率合成器經實用測試,其輸出信號頻率范圍為1.5GHz~2.9GHz,頻率分辨率為1Hz;輸出功率為+9dBm;帶內雜散抑制為-60dBc;偏離中心頻率10kHz的相位噪聲為-90dBc/Hz。

表2 串行裝載時40位數據的功能

?

| W0 | …… | W30 | W31 | W32 | W33 | W34 | W35 | W36 | W37 | W38 | W39 |

| Freq | Freq | Freq | Control | Control | Power | Phase | Phase | Phase | Phase | Phase | |

| -b0 | …… | -b30 | -b31 | -down | -b0 | -b1 | -b2 | -b3 | -b4 | ||

| (LSB) | (MSB) | (LSB) | (MSB) |

實踐證明,在本方案中,將DDS輸出端的低通濾波器改為帶通濾波器,對于減小整個頻率合成器的雜散噪聲非常有效。

更多鎖相環知識請訪問 http://m.1cnz.cn/zhuanti/PLL.html

電子發燒友App

電子發燒友App

評論